ELIAS: An Accurate and Extensible Lithography Aerial Image Simulator with Improved Numerical Algorithms

Project Director: David Z. Pan

Student: Peng Yu

|

|

|

|

|

|

Lithography simulators have been playing an indispensable role in process optimization and design for manufacturability (DFM). The ever smaller feature sizes demand higher numerical accuracy and faster runtime on these lithography simulators. Aerial image simulation is the first key step in lithography simulation, and the method using transmission cross coefficient (TCC), which is a 2-dimensional integral, is the most commonly used technique for full-chip aerial image simulation. We find that the majority of the numerical error during the TCC computation is due to the discontinuous boundaries of the support of the TCC integrand. We reduce the error dramatically by using a recursive integration algorithm. Because TCC is usually computed on uniform grids, we further speed up the algorithm without increasing the errors. Given the same accuracy, our new algorithm can speed up the runtime by 100 to 1000 times. Our algorithm also provides smooth tradeoff between accuracy and runtime. It can be used to benchmark other lithography aerial simulators. The algorithm is implemented in ELIAS, a flexible software framework that can be used to incorporate different lithography settings.

ELIAS 1.0

Author: Peng Yu. Copyright © The University of Texas, 2009. All rights reserved.

IF YOU AGREE TO THE UT RESEARCH LICENSE, PLEASE FILL IN FOLLOWING FORM. THE CODE WILL BE DISTRIBUTED TO YOU ONCE YOU ARE APPROVED.

Peng Yu and David Z. Pan, "ELIAS: An Accurate and Extensible Lithography Aerial Image Simulator with Improved Numerical Algorithms", accepted by IEEE Transactions on Semiconductor Manufacturing.

Peng Yu and Zhigang Pan, "Method for Extensible Lithography Aerial Image Simulator", U.S. Patent Application 61/112,842.

Experimental results show that our new algorithm is more accurate than an old algorithm with the same runtime. time in the literature with the shortest wire-length. The following figures are from the paper published in IEEE Transactions on Semiconductor Manufacturing.

The following figure shows the errors of the old and new methods with Delta'=1e-4, where the defocus z=100nm.

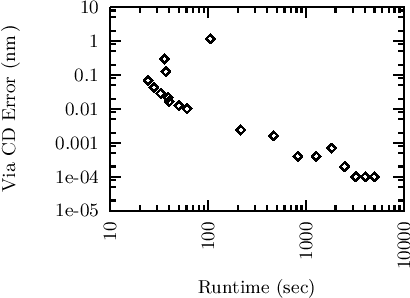

The following two figures show CD errors vs. the TCC computation runtime (the infocus case, 105nm via with a negative photoresist).

(a) The old method.

(b) The new method (n=1 and Delta'=1e-4). No data points are shown, when Runtime is over 100 sec, because the CD errors are almost zero under these conditions.

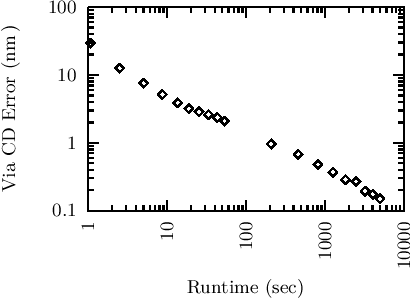

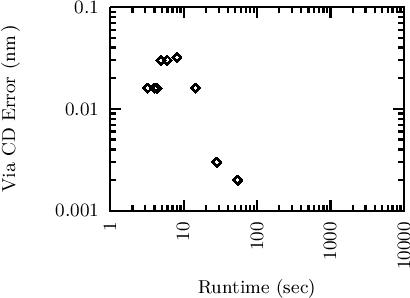

The following two figures show CD errors vs. the TCC computation runtime (the defocused case, 105nm via with a negative photoresist).

(a) The old method.

(b) The new method (n=1 and Delta'=1e-4).

last updated by April 30 2009