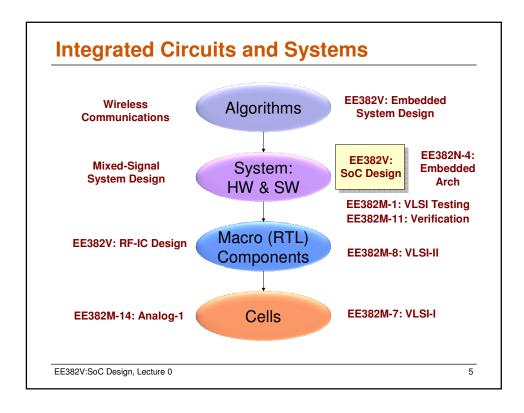

## **Course Overview**

• Systematic hardware/software co-design & co-verification

## > Class labs and project: Software-defined radio SoC

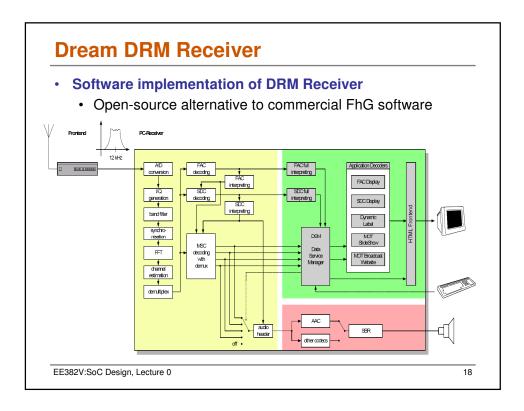

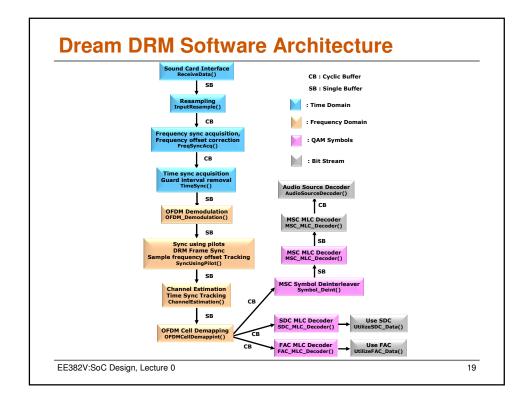

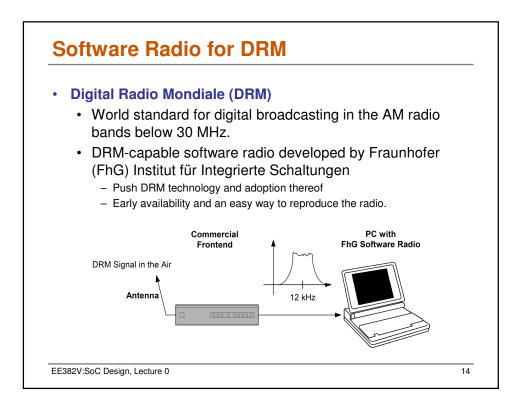

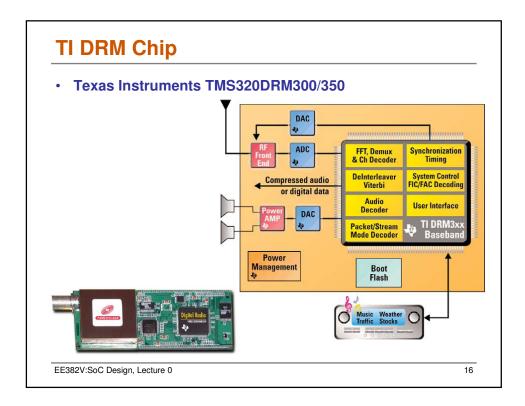

- DRM (Digital Radio Mondiale) system

Hardware/software co-design

- State-of-the-art synthesis and verification tools and flows

High-level hardware synthesis from C++ to RTL

- Virtual ARM platform modeling and simulation in SystemC

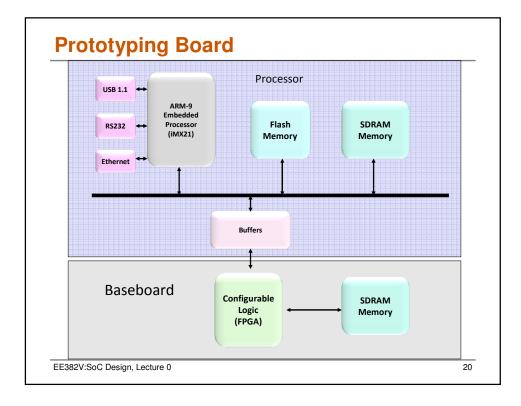

- ARM-based FPGA prototyping platform

ARM processor, I/O devices, memory components, hardware accelerators

7

EE382V:SoC Design, Lecture 0

9

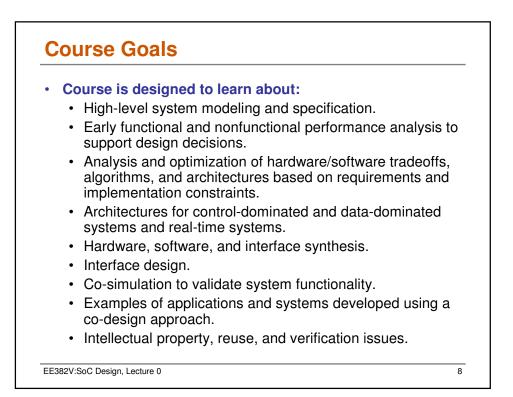

## • Likely to be covered in class:

- · System-level and SoC design methodologies and tools;

- HW/SW Co-design: analysis, partitioning, real-time scheduling, hardware acceleration;

- Virtual platform models, co-simulation and FPGAs for prototyping of HW/SW systems;

- Transaction-Level Modeling (TLM) and Electronic System-Level (ESL) languages: SystemC;

- High-Level Synthesis (HLS): allocation, scheduling, binding, resource sharing, pipelining;

- SoC and IP integration, verification and test.

EE382V:SoC Design, Lecture 0

| Ins     | structors                                                                                                             |

|---------|-----------------------------------------------------------------------------------------------------------------------|

| •       | Course Coordinator: Jacob Abraham <u>jaa@cerc.utexas.edu</u><br>– Office Hours: ACE 6.124, MW 2:30 – 3:30 or by appt. |

| •       | Guest lecturers from industry and academia:<br>– Jacob Abraham, Xtreme EDA, Mark McDermott, Steven Smith              |

| •       | TA: Hyungman Park < <u>hpark@cerc.utexas.edu</u> ><br>– Office hours: ENS 113A, TBD                                   |

| • Inf   | ormation                                                                                                              |

|         | Web: http://www.cerc.utexas.edu/~jaa/soc/<br>– Lecture notes, homework and lab exercises.<br>Blackboard               |

|         | <ul> <li>Announcements, assignments, grades.</li> </ul>                                                               |

| • Da    | ites (tentative)                                                                                                      |

| •       | Exam: November 12                                                                                                     |

| •       | Final project presentations: December 3                                                                               |

| EE382V: | SoC Design, Lecture 0                                                                                                 |

## **Course Policies** Grading: • Homework: 15% Lab assignments: 30% • Exam: 20% • Project: 35% Late penalties: • • 20% per day (24 hours) Academic dishonesty . · Homeworks - Ok to discuss questions and problems with others - But turn in own, independent solution Labs and project - In teams, one report and presentation - Collaboration encouraged and desired Plagiarism - Use of any outside source of information without quoting or referencing is cheating EE382V:SoC Design, Lecture 0 11

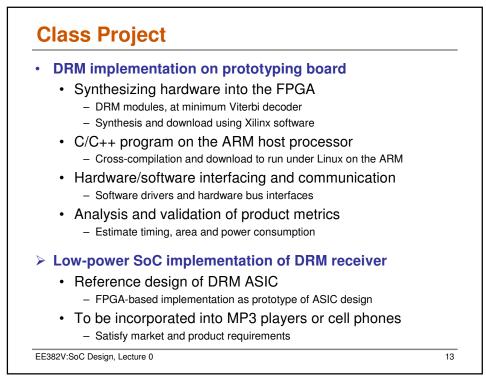

| Lab1: DRM on ARM (3 weeks, due Sept. 25)                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Profiling of DRM code on Linux host and ARM simulator         <ul> <li>Identify time consuming bottlenecks to optimize</li> </ul> </li> </ul> |

| <ul> <li>Float to fixed point conversion</li> </ul>                                                                                                    |

| <ul> <li>Improve performance without loss in accuracy (SNR)</li> </ul>                                                                                 |

| Lab 2: DRM system architecture (due October 16)                                                                                                        |

| <ul> <li>ARM plus hardware acceleration</li> </ul>                                                                                                     |

| <ul> <li>Identify and partition DRM code into hardware and software</li> </ul>                                                                         |

| <ul> <li>Virtual platform modeling and simulation</li> </ul>                                                                                           |

| <ul> <li>Isolate and interface hardware as SystemC module</li> </ul>                                                                                   |

| <ul> <li>Co-simulation w/ software and firmware on ARM-Linux using OVPsim</li> </ul>                                                                   |

| Lab 3: DRM hardware synthesis (due Nov. 6)                                                                                                             |

| <ul> <li>High-level synthesis of Viterbi decoder from C++ to RTL</li> </ul>                                                                            |

| <ul> <li>Mentor Catapult-C synthesis tool</li> </ul>                                                                                                   |

| <ul> <li>Verification of synthesis results</li> </ul>                                                                                                  |

| <ul> <li>Testbench around standalone C++ vs. RTL hardware module</li> </ul>                                                                            |

| E382V:SoC Design, Lecture 0                                                                                                                            |

|                                                                                                                                                        |

| UTC       | Days  | kHz   | Beam | Target      | Power | Programme    | Language    |

|-----------|-------|-------|------|-------------|-------|--------------|-------------|

| 0000-0059 | daily | 1431  | ND   | Canberra    | 0.05  | MCS          | English     |

| 0000-0059 | daily | 9790  | 227  | NE USA      | 70    | TDPradio     | Dance Music |

| 0000-0300 | daily | 177   | ND   | Germany     | 150   | DLR Kultur   | German      |

| 0000-2400 | daily | 1386  | ND   | AUS-NSW     | 3     | ABC          | English     |

| 0000-2400 | daily | 1008  | ND   | Prov. Hunan | 4     | Economic Ch. | Chinese     |

| 0000-2400 | daily | 999   | ND   | Paris       | 8     | DRM test     | French      |

| 0000-2400 | daily | 25775 | ND   | Rennes      | 0.1   | TDF Radio    | French      |

| 0000-2400 | daily | 25775 | ND   | Cote d'azur | 0.7   | AGORA        | French      |

| 0000-2400 | daily | 59500 | ND   | Rennes      | 0.15  | TDF          | French      |

|           |       |       |      |             |       |              |             |