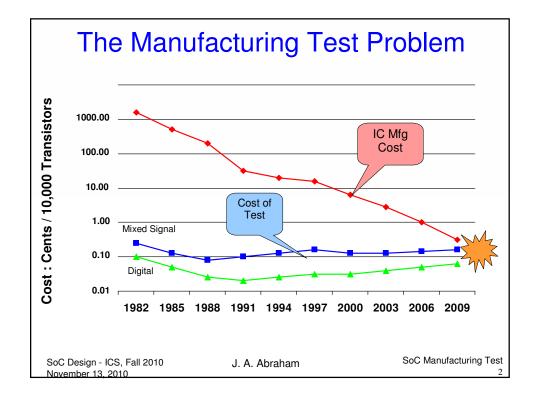

# SoC Manufacturing Test

- SoC Testability Features

- Boundary Scan

- P1500 standard

- SoC Testing Costs

- Built-In Self Test

- · Testing Mixed-Signal Components

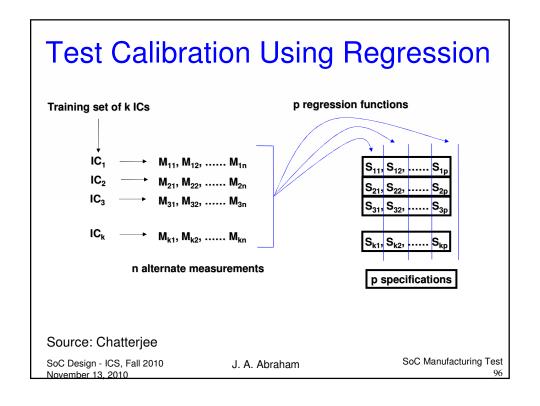

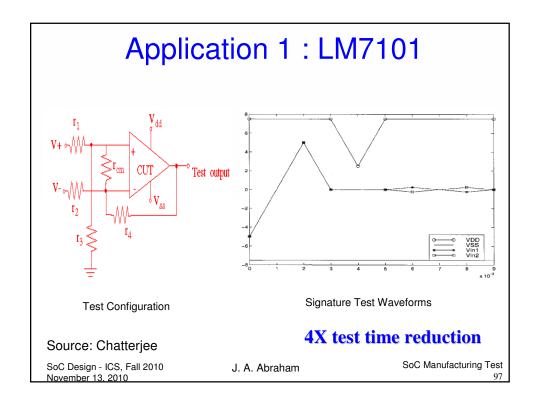

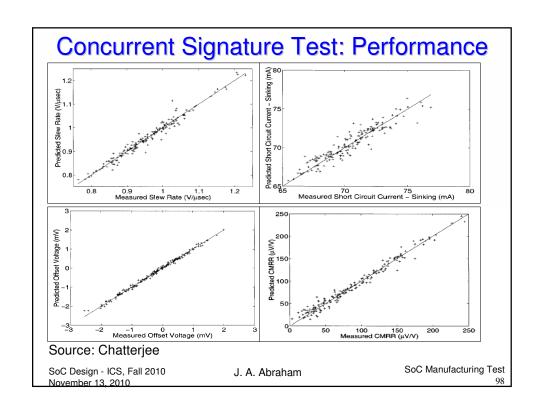

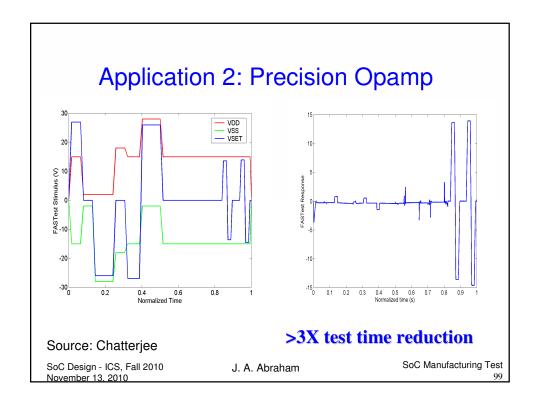

- "Alternate" test

- Defect Tolerance

- Error Detection and Fault Tolerance

- Loopback test of Mixed-Signal SoCs

SoC Design - ICS, Fall 2010 November 13, 2010

J. A. Abraham

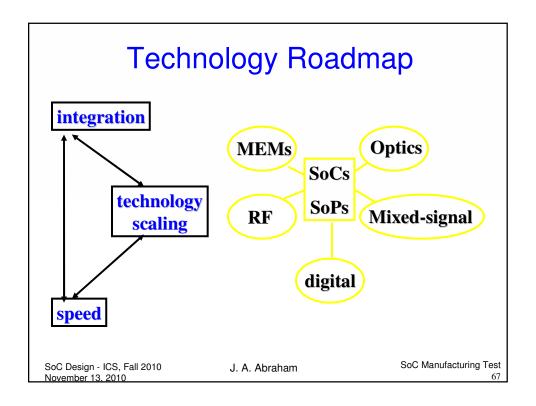

# Partitioning for SoC Test

- Partition according to test methodology:

- Logic blocks

- Memory blocks

- Analog blocks

- Provide test access:

- Boundary scan

- Analog test bus

- Provide test-wrappers for cores

SoC Design - ICS, Fall 2010 November 13, 2010

J. A. Abraham

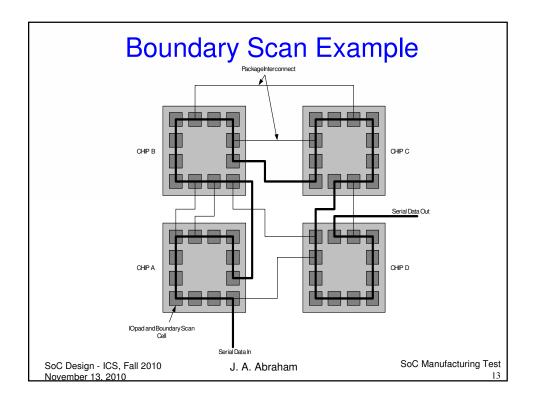

# **Boundary Scan**

- Testing boards is also difficult

- Need to verify solder joints are good

- Drive a pin to 0, then to 1

- · Check that all connected pins get the values

- Through-hold boards used "bed of nails"

- SMT and BGA boards cannot easily contact pins

- Build capability of observing and controlling pins into each chip to make board test easier

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

SoC Manufacturing Test

Boundary Scan (IEEE 1149.1) Boundary Scan Register Μ Device Identification Reg. U Optional User Test Data Register X Optional TDI Bypass Register Decoding Logic Instruction Register DR Clocks and Control IR\_Clocks and Control TDO **TMS** Select TCK Enable SoC Design - ICS, Fall 2010 SoC Manufacturing Test J. A. Abraham November 13, 2010

## **Boundary Scan Interface**

Boundary scan is accessed through five pins

- TCK: test clock

- TMS: test mode select

- TDI: test data in

– TDO: test data out

- TRST\*: test reset (optional)

Chips with internal scan chains can access the chains through boundary scan for unified test strategy.

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

#### **RUNBIST** Instruction

- Purpose: Allows issue of BIST command to component through JTAG hardware

- Optional instruction

- Lets test logic control state of output pins

- 1. Can be determined by pin boundary scan cell

- 2. Can be forced into high impedance state

- BIST result (success or failure) can be left in boundary scan cell or internal cell

- Shift out through boundary scan chain

- May leave chip pins in an indeterminate state (reset required before normal operation resumes)

Source: Bushnell and Agrawal

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

SoC Manufacturing Test

Purpose: Bypasses scan chain with 1-bit register

From

TDI

ShiftDR

ClockDR

ClockDR

ClockDR

ClockDR

Source: Bushnell and Agrawal

Soc Design - ICS, Fall 2010

November 13, 2010

BYPASS Instruction

From

TDI

CLK

CLK

CLK

CLK

CLK

CLK

Source: Bushnell and Agrawal

Soc Manufacturing Test

November 13, 2010

Soc Manufacturing Test

22

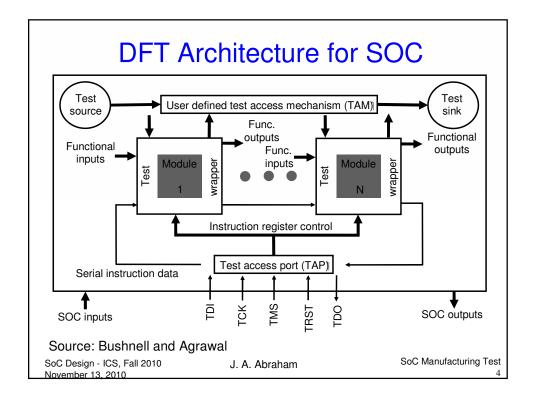

# Additional DFT Components

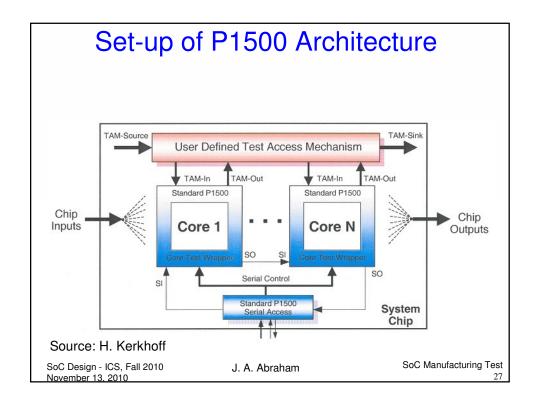

- Test source: Provides test vectors via on-chip LFSR, counter, ROM, or off-chip ATE.

- Test sink: Provides output verification using on-chip signature analyzer, or off-chip ATE.

- Test access mechanism (TAM): User-defined test data communication structure; carries test signals from source to module, and module to sink; tests module interconnects via test-wrappers; TAM may contain bus, boundary-scan and analog test bus components.

- Test controller: Boundary-scan test access port (TAP); receives control signals from outside; serially loads test instructions in test-wrappers.

Source: H. Kerkhoff

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

SoC Manufacturing Test

racturing re

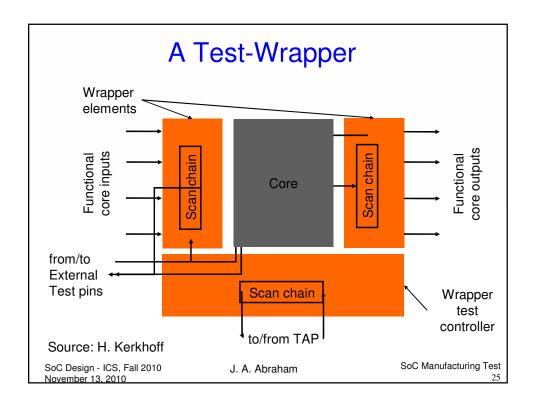

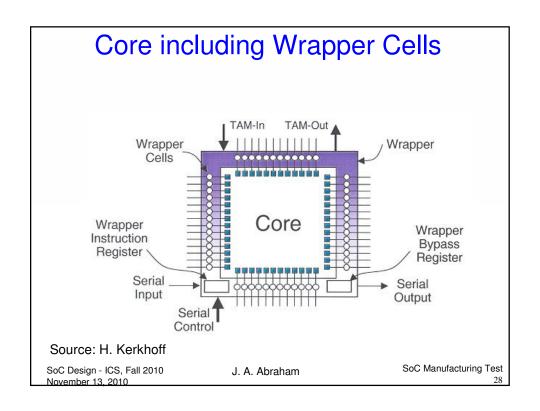

#### Test Wrapper for a Core

- Logic added around a core to provide test access to the embedded core

- ☐ Test-wrapper provides for each core input terminal

- An external test mode Wrapper element observes core input terminal for interconnect test

- An internal test mode Wrapper element controls state of core input terminal for testing the logic inside core

- For each core output terminal

- A normal mode Host chip driven by core terminal

- An external test mode Host chip is driven by wrapper element for interconnect test

- An internal test mode Wrapper element observes core outputs for core test

Source: H. Kerkhoff

SoC Design - ICS, Fall 2010 November 13, 2010

J. A. Abraham

SoC Manufacturing Test

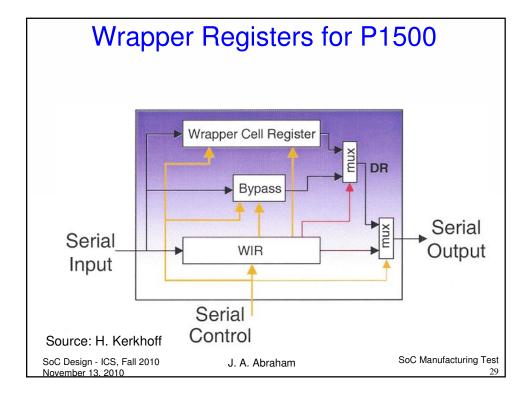

#### Goals of IEEE P1500

- Core test interface between embedded core and system chip

- Test reuse for embedded cores

- Testability guarantee for system interconnect and logic

- Improve efficiency of test between core users and core providers

Source: H. Kerkhoff

SoC Design - ICS, Fall 2010 November 13, 2010

J. A. Abraham

SoC Manufacturing Test

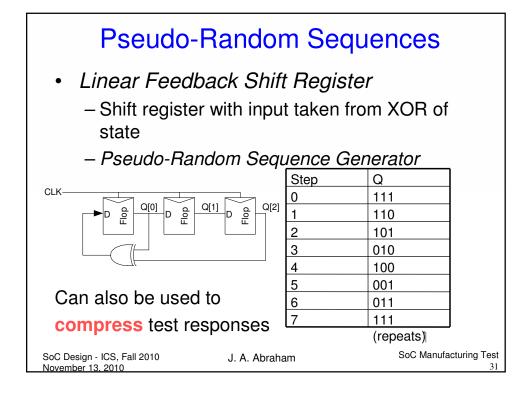

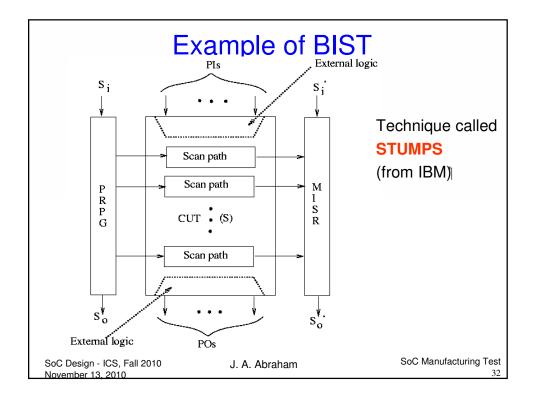

#### Built-In Self Test (BIST)

- Increasing circuit complexity, tester cost

- Interest in techniques which integrate some tester capabilities on the chip

- Reduce tester costs

- Test circuits at speed (more thoroughly)

- · Approach:

- Compress test responses into "signature"

- Pseudo-random (or pseudo-exhaustive)

pattern generator (PRG) on the chip

- Integrating pattern generation and response evaluation on chip – BIST

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

SoC Manufacturing Test

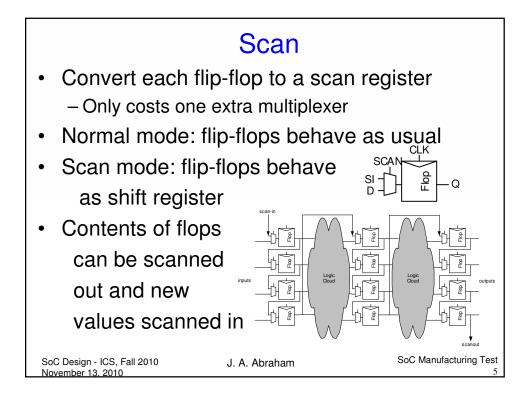

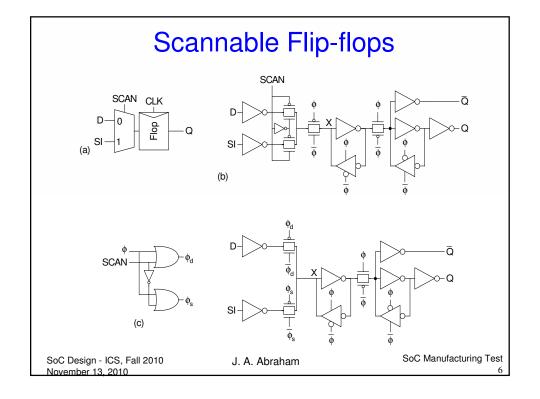

# Why is Conventional Test Successful? • Two innovations have allowed test to keep

- Two innovations have allowed test to keep up with complex designs

- The stuck-at fault model

- the model allows structural test generation, with a number of faults which is linear in the size of the circuit

- Partitioning the circuit

- partitioning the circuit (with scan latches for example), alleviates the test problem so that test generation does not have to deal with the entire circuit

- Do these two assumptions hold for Deep soc Deep soc Deep soc Deep soc Deep soc Deep soc Manufacturing Test November 13, 2010

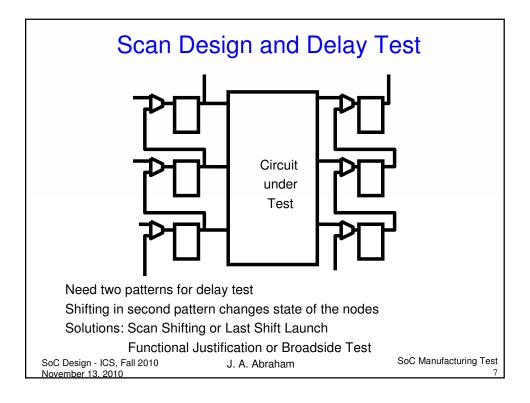

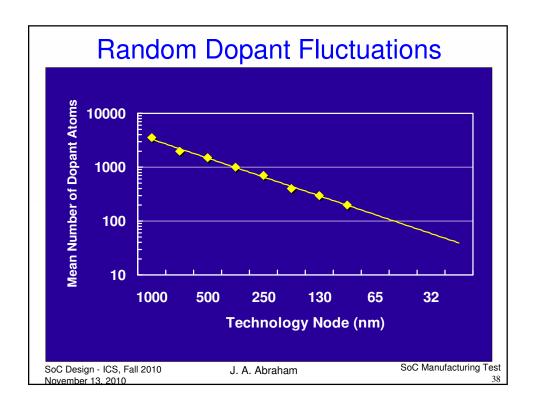

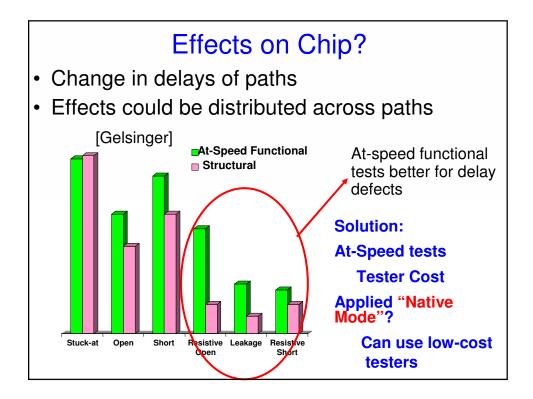

# Defects in DSM Technologies

- Experiments on real chips (e.g., Stanford University)

- Stuck-at tests do not detect some defects unless they are applied at speed

- Resistive opens comprise the bulk of test escapes in one production line

- Likely in copper interconnect cause delay faults

- Delay faults identified as the cause of most test escapes on another line

- Speed differences of up to a factor of 1.5 can exist between fast and slow devices - problems with "speed binning"

"speed binning"

SoC Design - ICS, Fall 2010

J. A. Abraham

SoC Manufacturing

November 1889 Sing possibility of shorts and crosstally

#### Native-Mode Built-In Self Test

- Functional capabilities of processors can be used to replace BIST hardware – (UT research, published in ITC 1998)

- Application to self-test of processors at Intel FRITS method applied to Pentium 4, Itanium (Published in ITC 2002)

#### **Hardware for MISR**

SoC Design - ICS, Fall 2010 .

November 13, 2010

J. A. Abraham

Software implementation

of MISR

for each data value D; {

Shift\_Right\_Through\_Carry(S);

if (Carry) { S = XOR(S, polynomial) }

S = XOR(S, D;)

}

SoC Manufacturing Test

#### Native-Mode Self Test for Processors

- Random instructions can be run from cache and results compressed into a signature

- Implementation in Intel FRITS system showed benefits for real chips (Pentium 4, Itanium)

- Technique can be used for self-test of an embedded processor in a System-on-Chip

- Is it possible to now use this processing capability to test other modules (digital, analog/mixed-signal and RF) on the SoC?

- -First, can the processor test be improved to detect realistic defects, e.g., small delays?

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

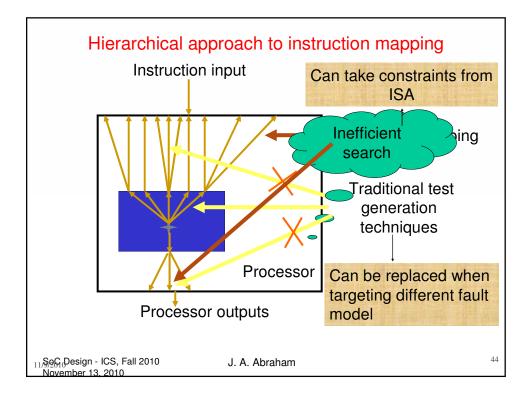

#### Are Random Tests Sufficient?

- Intel implementation involved code in the cache which generated random instruction sequences

- Interest in generating instructions targeting faults

- Possible to generate instruction sequences which will test for an internal stuck-at fault in a module (Gurumurthy, Vasudevan and Abraham, ITC 2006)

- In order to deal with defects in DSM technologies, need to target small delay defects

- Recent work: automatically generate instruction sequences which will target small delay defects in an internal module (Gurumurthy, Vemu, Abraham and Saab, European Test Symposium (ETS) 2007)

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

#### Instruction mapping using bounded model checking

- Uses symbolic model verifier's (SMV) bounded model checking option (BMC)

- -Provides verification result up to a given bound

- Accepts properties written in linear temporal logic (LTL)

- -Generates a counterexample if property fails

- Expresses the controllability and observability constraints in LTL

- Extracts instruction sequence from the counterexample

SoC<sub>9</sub>Design - ICS, Fall 2010 November 13, 2010

J. A. Abraham

45

# Application to stuck-at faults

- Used a commercial ATPG engine at the module level

- Mapped sequences generated by the ATPG engine

- No feedback

- No additional effort if the sequence generated for a fault is not mappable

- Targeted hard-to-detect faults with this approach

- Able to achieve 82% fault coverage

- -Up from 68% through random instructions

SoCoDesign - ICS, Fall 2010 November 13, 2010 J. A. Abraham

# Test for Small Delay Defects

- Weighted random instructions will give good coverage for hard defects

- Need to test paths in the circuit to detect small delay defects

- However, the number of paths in a circuit can be exponential in the number of nodes

- Solution: test the longest path through every node

- This will detect the smallest possible delay increase which will cause the circuit to fail

- Total number of tests linear in number of nodes

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

SoC Manufacturing Test

47

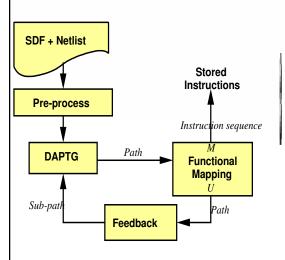

# Automatic Generation of Instruction Sequences for Small Delay Defects

Phase 1: all paths above delay threshold

Phase 2: longest paths through all nodes Delay-Based ATPG: generate "TRUE" paths above given delay threshold

Functional mapping: use verification engine

Feedback: heuristics to speed up search

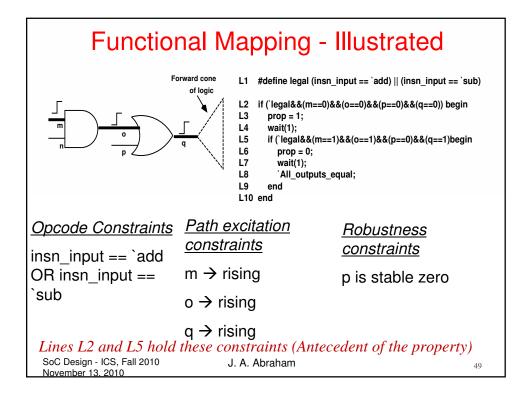

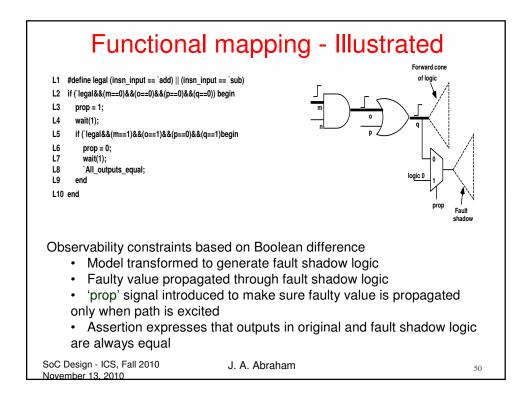

#### Functional mapping - Illustrated

- Transformed model and property given to BMC

- Counterexample, if produced, satisfies the excitation, controllability and robustness constraints

- Fails the assertion → some output is different between faulty and correct logic

- Values for 'insn\_input' in counterexample trace gives the required instruction sequence

SoC Design - ICS, Fall 2010 November 13, 2010

J. A. Abraham

51

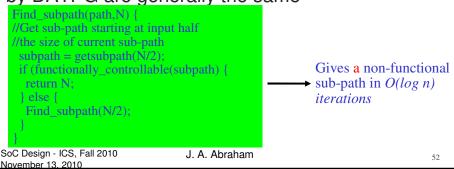

#### **Feedback**

- Many paths generated by DATPG are not functionally feasible

- Many non-functional paths have a common nonfunctional sub-path

- Process of identifying the maximal non-functional sub-path in a given path is time consuming - O(n²) iterations needed

- Fact first few nodes in consecutive paths produced by DATPG are generally the same

UT Austin, ECE Department

## Experimental setup

- OR1200

- Open source RISC processor

- -5 stage pipeline

- Source code and documentation available from

www.opencores.org

Synthesized using TSMC's 0.18uArtisan technology No. of instructions in OR1200 ISA

No. of 15878 combinational

No. of sequential elements

1594

SoC Design - ICS, Fall 2010 November 13, 2010

J. A. Abraham

53

#### Results

Phase1: Threshold 80% of clock

| Paths | Yes   | No    | Timed out |

|-------|-------|-------|-----------|

| 27424 | 15118 | 12106 | 200       |

Phase2: Results for some modules

N → Node coverage efficiency

Percentage of nodes for which mapping produced a test or rejected all paths given by DATPG

Yes - Functionally feasible

Not functionally feasible

| Module | Yes  | No    | Rejecte<br>d Sub-<br>paths | N(%) |

|--------|------|-------|----------------------------|------|

| ctrl   | 1826 | 29191 | 68087                      | 91   |

| alu    | 1427 | 16985 | 2716                       | 100  |

| Isu    | 970  | 4077  | 3744                       | 100  |

| wbmux  | 1146 | 2285  | 2118                       | 100  |

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

| N                          | 96%           |  |

|----------------------------|---------------|--|

| Average<br>mapping<br>time | 18.85se<br>cs |  |

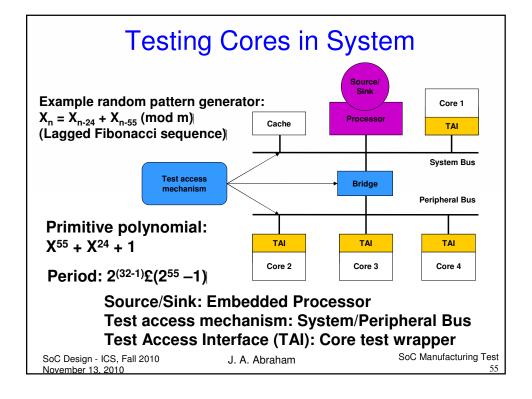

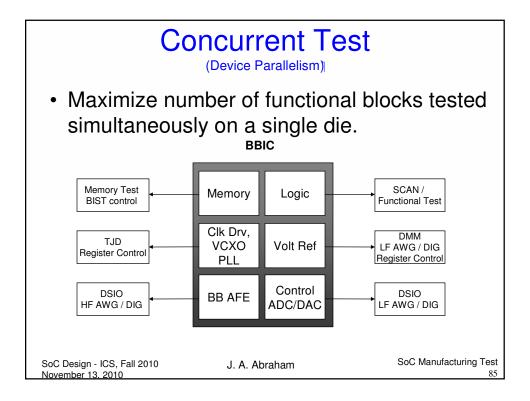

#### Test Access Mechanisms for SoC Test

- Non-functional access

- Uses a kind of access to core not allowed during the normal functional operation

- Generally based on scan chains or other design for test (DFT) structures

- Can also use the embedded processor as the test source/sink → Needs wrappers around the core under test

- Functional access

- Embedded processor is the test source/sink → No DFT structures or wrappers around the cores

#### Non-functional TAMs

- Boundary scan based

- Uses the JTAG/boundary scan mechanism to load/capture the tests

- Slow since the access is serial

- Direct access based

- Direct access to core test pins given through external pins

- Faster

- High overhead to route the access pins and also multiple pins required

57

#### Functional TAMs for Testing Cores

- Software-Based Self Test: Use the intelligence of the embedded processor to test the SOC

- At-speed tests are possible

- Cores in the SOC can be of three kinds

- White box -- internals visible, structure changeable

- 2. Grey box all the internals visible, but structure of the core cannot be changed

- Black box no internals visible, no change can be made on the core

- Any methodology for testing black box cores should not depend on knowledge of the core's internals

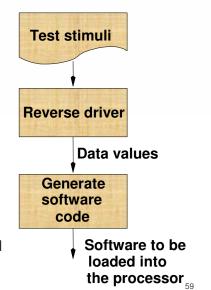

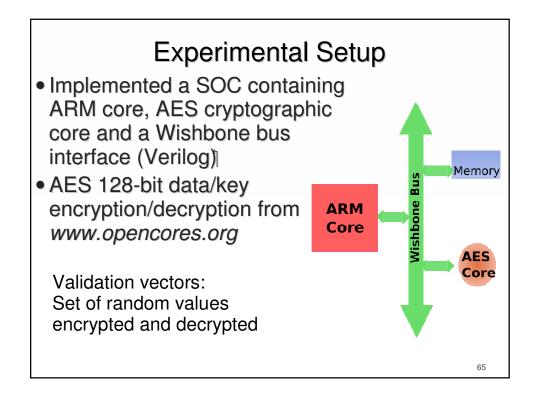

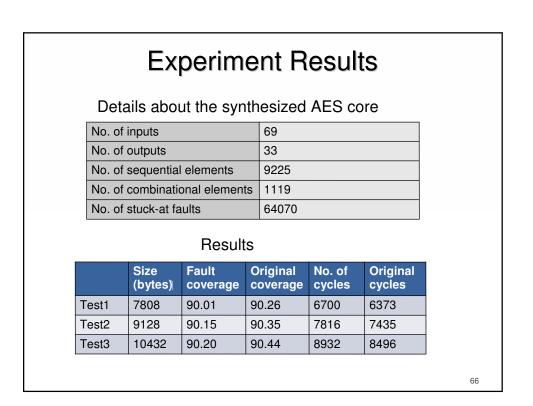

# Approach to Testing Cores

- Uses functional TAM

- Uses pre-existing vectors

- Generates software to be loaded on to the embedded processor

- Gurumurthy, Sambamurthy and Abraham, Int'l Test Synthesis Workshop (ITSW) 2008

## **Pre-Existing Vectors**

- If using a core bought from vendor

- Vectors might also be provided by the vendor

- Reusing a core

- Vectors from the previous use

- Newly designed core

- Validation vectors

- Only constraint: these vectors must be functional test patterns for the core

#### **Reverse Driver**

- Parses the vector sequence to generate the data set to be sent to the core being tested

- Is specific to each core as many as the number of driver programs

- Only overhead involved

- Generates the output in a format readable by the driver program

61

#### Reverse Driver - Illustration

- Peripheral core communicating with external environment (send/receive 32-bit data)

- Five 8-bit registers addresses 0 − 4

- Register 0 Control

- Registers 1 to 4 Data

| Address | Data |         |                    |

|---------|------|---------|--------------------|

| 0x00    | 0x07 |         |                    |

| 0x01    | 0x54 | Reverse | Send at speed rate |

| 0x02    | 0xDF | Driver  |                    |

| 0x03    | 0x71 |         | Data               |

| 0x04    | 0x78 |         | 0x0754DF7178       |

|         | •    |         | 62                 |

#### Software Generation

- Use the driver program associated with each core being tested

- Driver programs

- Software code that actually talks with the nonprocessor cores

- Know about the bus protocol

- Generally able to take in the data to be sent to the core or read back data from the core

- Developed as part of designing the SOC

63

#### Coverage Measurement

- Simulate the SOC using the software generated

- Platform used SOC validation can be used

- Monitor the core boundaries to capture the pin data

- Fault simulate the core with the captured data

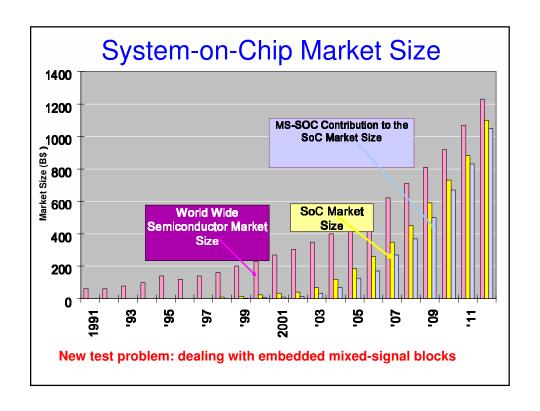

## **Testing Mixed-Signal SoCs**

- Analog test issues

- · Analog test bus

- · "Alternate" tests

- System-level Built-In Self Test

- Testers and test application

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

SoC Manufacturing Test

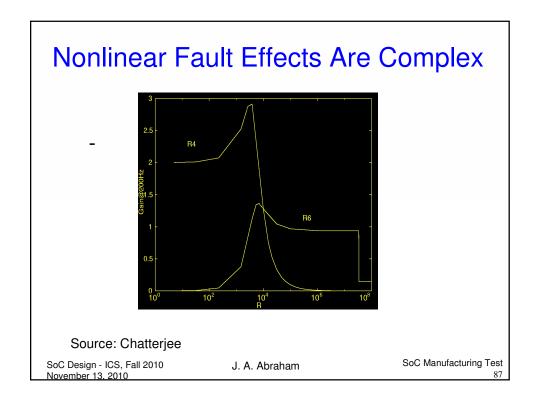

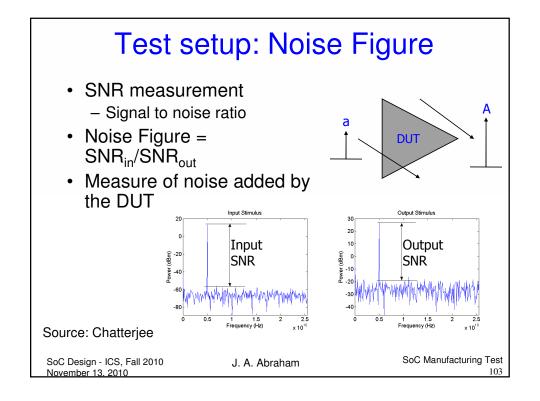

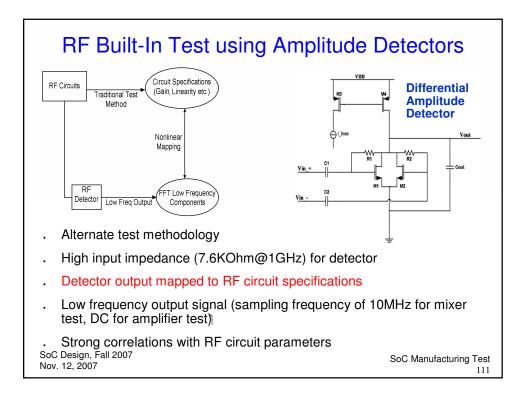

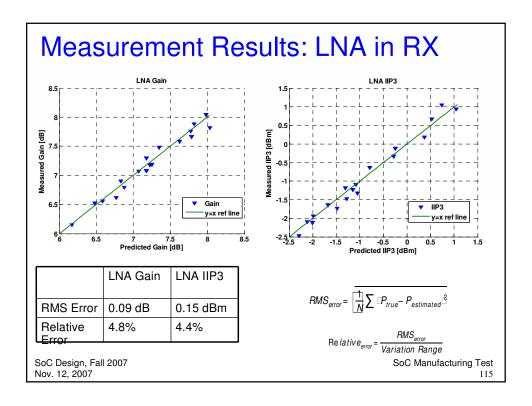

# Testing Analog/Mixed-Signal/RF Circuits

- Have to deal with continuous signals

- Customers want a guarantee of specifications

- A defect may or may not affect the desired behavior of a chip

- Tests are for the specifications, not for defects

- Similar trend in digital: testing for distributed path delays

- Test costs are very high if every specification has to be tested

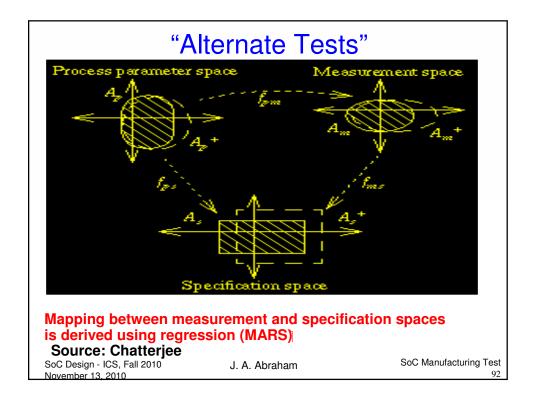

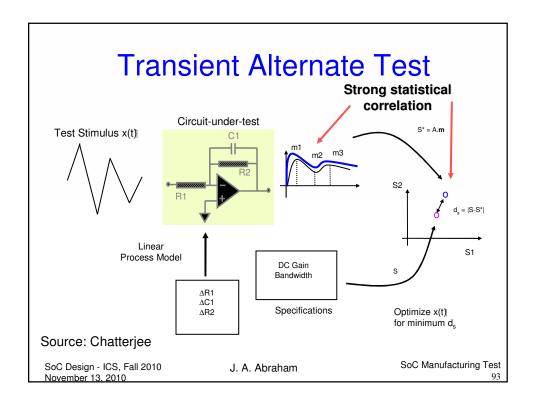

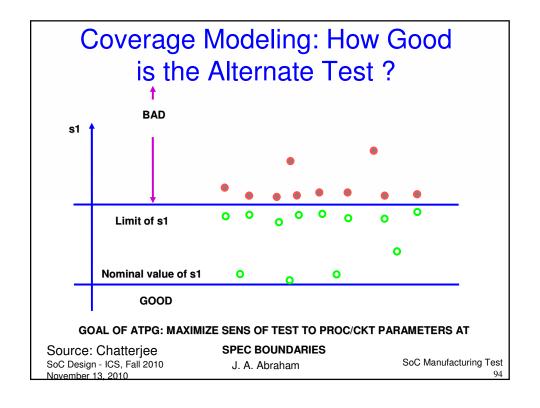

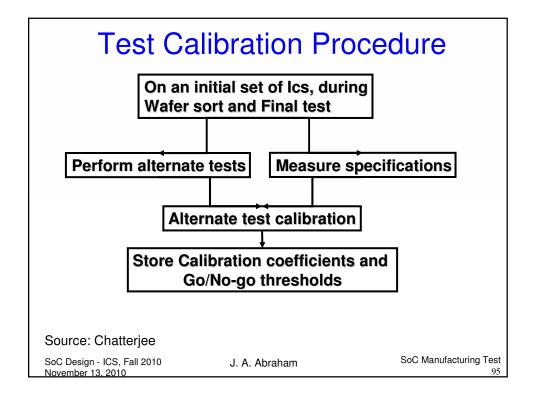

"Alternate Tests"

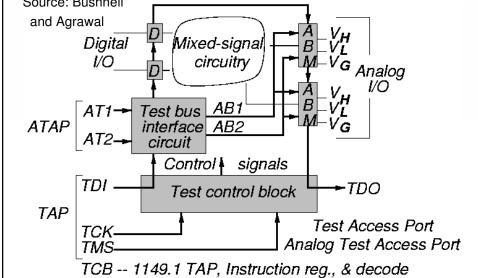

# Analog Test Bus (IEEE 1149.4)

- PROs:

- Usable with digital JTAG boundary scan

- Adds analog testability both controllability and observability

- Eliminates large area needed for analog test points

- CONs:

- May have a 5% measurement error

- C-switch sampling devices couple all probe points capacitively, even with test bus off – requires more elaborate (larger) switches

- Stringent limit on how far data can move through the bus before it must be digitized to retain accuracy

Source: Bushnell and Agrawal

SoC Design - ICS, Fall 2010 November 13, 2010

J. A. Abraham

SoC Manufacturing Test

Analog Test Bus Diagram

Source: Bushnell

and Agrawal

SoC Design - ICS, Fall 2010 November 13, 2010

J. A. Abraham

SoC Manufacturing Test

anulaciuming resi

### **Typical Mixed-Signal Test Program**

- Open-Shorts

- Detected wirebond and packaging issues

- Leakage Test Input and Tri-State pads

- · DC Levels Vol, Voh, Vih, Vil of pads

- Digital Tests: SCAN Tests, Memory, Functional Test (@ speed, high speed IO)

- Current tests Dynamic, Special Modes, Standby, Iddq

- Mixed-Signal Test

- PLL, DAC, ADC, OpAmps, Filters, References, Mixers

- Gain Stages, Impedance Match, PA, LNA . . .

SoC Design - ICS, Fall 2010 November 13, 2010

J. A. Abraham

SoC Manufacturing Test

# **Example Device**

- Cell-Phone Handset Baseband IC

- Digital

- Flash, SRAM, Keypad, LCD, SIM Card, PC & LED interfaces

- · RISC Controller, DSP, Hardware Co-processors

- · Embedded SRAM

- · Embedded ROM

- Transceiver and Power Management Control

- Control DAC/ADC

- · PA, Transceiver

- Voice CODEC

- Baseband DAC, ADC

- PLL

- Timer

- Voltage References SoC Design ICS, Fall 2010

J. A. Abraham

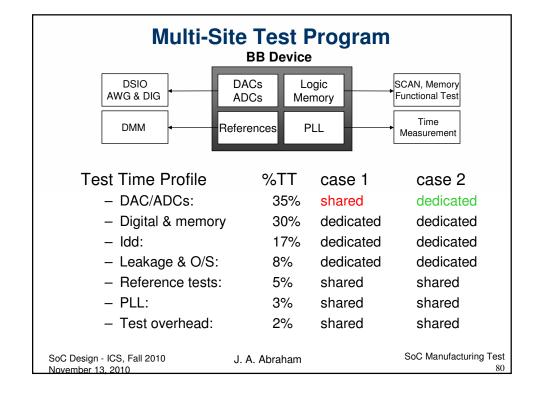

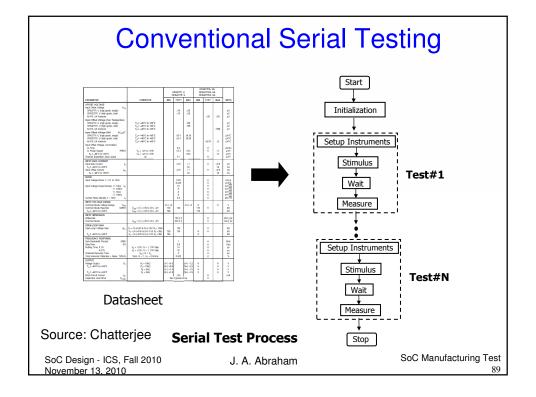

### **Single Site Test Program**

Tester: Teradyne Catalyst

• Capital Cost: \$2.3 million

Test Times: 10 Seconds

- Test time profile:

DAC/ADCs: 35%

Digital & Memory 30%

Idd 17%

Leakage & O/S: 8%

Reference tests: 5%

PLL: 3%

Test overhead: 2%

SoC Design - ICS, Fall 2010 .I A

November 13, 2010

J. A. Abraham

SoC Manufacturing Test

7

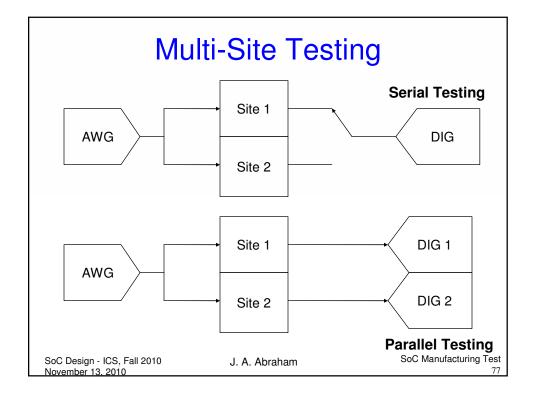

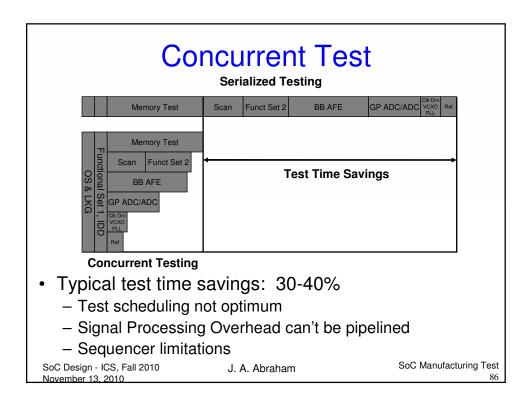

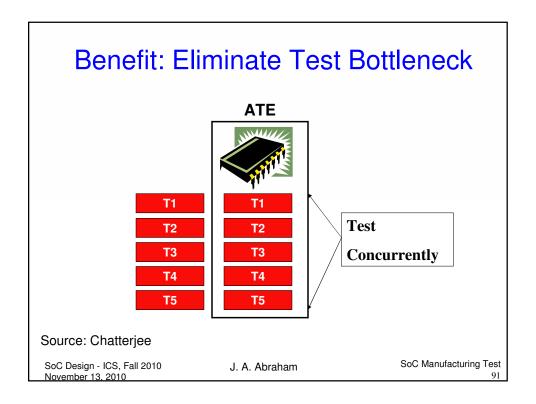

## Multi-Site Test

- Multi-Site Test testing more than 1 device at a time

- Parallel Tests testing of multiple devices simultaneously

- Assumes no resource limitations

- Serial Tests testing executed one site at a time because of resource limitations

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

SoC Manufacturing Test

76

### **Multisite Mixed-Signal Testing**

- Multi-site Functional, Scan, Memory, leakage & continuity test efficiencies are typically high: 85-98%

- Resource per-pin / site

- Per Pin PMU leakage & continuity

- Functional pattern memory behind each pin

- SCAN Capability, Memory Test Option (per site)

- Mixed-Signal efficiencies are typically driven by resource constraints

- dedicated vs. shared instruments

- which drive parallel vs. serial execution

SoC Design - ICS, Fall 2010 November 13, 2010

J. A. Abraham

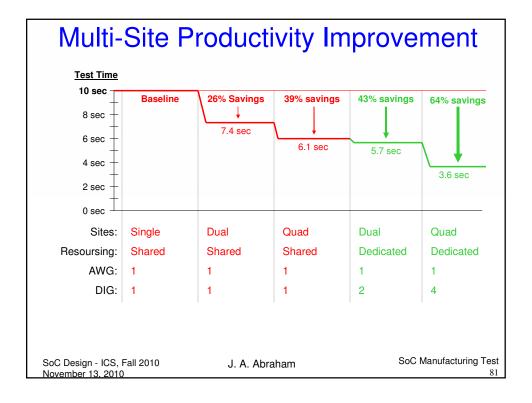

### **Multi-Site Tester**

A single site tester Test Coverage

- High Resolution AWG & Digitizer Voice Codec

GP DACs & ADCs

– Time Jitter DigitizerPLL

- High Bandwidth AWG & Digitizer BB codec

– DMM References

– Digital Pins with PMU– Digital &

Memory

Leakage & OS

- Instrument requirements for quad site Parallel Testing

- 4x if each resource is not shared

- Costly purpose build tester, with instruments shared

SoC Design - ICS, Fall 2010 November 13, 2010

J. A. Abraham

SoC Manufacturing Test

ivianulaciuming re

| Parallel Test                                          |                          |                |                       |  |  |  |  |  |

|--------------------------------------------------------|--------------------------|----------------|-----------------------|--|--|--|--|--|

| Cell Phone SOC (different device)                      |                          |                |                       |  |  |  |  |  |

|                                                        | Multi-Site<br>Efficiency | Tester<br>Cost | Ratio                 |  |  |  |  |  |

| Single site                                            | 1.00                     | 1.00           | 1                     |  |  |  |  |  |

| Dual site non-shared                                   | 1.73                     | 1.32           | 1.3                   |  |  |  |  |  |

| Qual site non-shared                                   | 3.00                     | 2.16           | 1.4                   |  |  |  |  |  |

| Multi-Site efficiency goes up faster than tester cost. |                          |                |                       |  |  |  |  |  |

| SoC Design - ICS, Fall 2010<br>November 13, 2010       | J. A. Abraham            | S              | oC Manufacturing Test |  |  |  |  |  |

### Hard Drive Read Channel Device

Typical device: DAC & ADC, AGC, Filters, Thermal Sensor, OpAmps, ROM, PLL, Digital Signal Processing, Small Memory

| # Sites | Catalyst | Efficiency | Tiger    | Efficiency |

|---------|----------|------------|----------|------------|

| Single  | 3.19 sec |            | 2.59 sec |            |

| Dual    | 3.86 sec | 79.1%      | 2.99 sec | 84.7%      |

| Triple  | 4.53 sec | 79.0%      | 3.40 sec | 84.5%      |

| Quad    | 5.18 sec | 79.2%      | 3.80 sec | 84.5%      |

Digital test:

Leakge test:

Idd test:

169ms single site - Catalyst

128ms single site - Catalyst

60ms single site - Catalyst

Signal Processing Overhead:

291ms single site - Catalyst

All other test mixed-signal in nature

SoC Design - ICS, Fall 2010 J. A. Abraham SoC Manufacturing Test November 13, 2010 83

# Pipeline Test Example

| Site 1 | O/S | LKG | Func   | PLL   | DAC   | ADC   | Codec |

|--------|-----|-----|--------|-------|-------|-------|-------|

|        | -PE | -PE | -PE    | -TJD  | -Dig  | -AWG  | -LFAC |

| Site 2 | O/S | LKG | Func - | Codec | PLL   | DAC   | ADC   |

|        | -PE | -PE | PE     | -LFAC | -TJD  | -Dig  | -AWG  |

| Site 3 | O/S | LKG | Func   | ADC   | Codec | PLL   | DAC   |

|        | -PE | -PE | -PE    | -AWG  | -LFAC | -TJD  | -Dig  |

| Site 4 | O/S | LKG | Func   | DAC   | ADC   | Codec | PLL   |

|        | -PE | -PE | -PE    | -Dig  | -AWG  | -LFAC | -TJD  |

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

### How do we define a failure?

ANY COMBINATION OF

CIRCUIT/PROCESS PARAMETERS

THAT CAUSES ONE OR MORE OF

THE CIRCUITS SPECIFICATIONS TO

BE VIOLATED IS DEFINED TO BE A

FAILURE

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

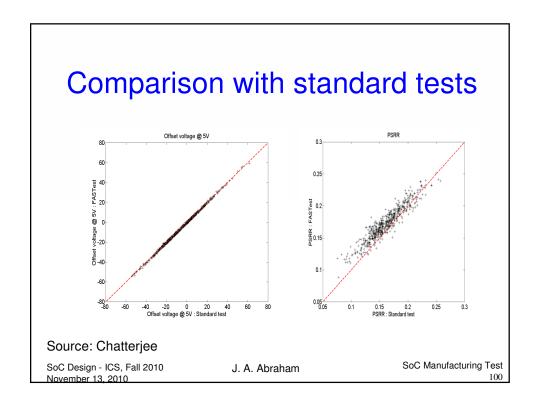

# New Alternate Test Approach

### Replace

Expensive specification tests, fully or partially

### With

Low-cost, easy-to-perform alternate tests

### Such that

No yield loss

Same coverage as specification tests

Source: Chatterjee

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

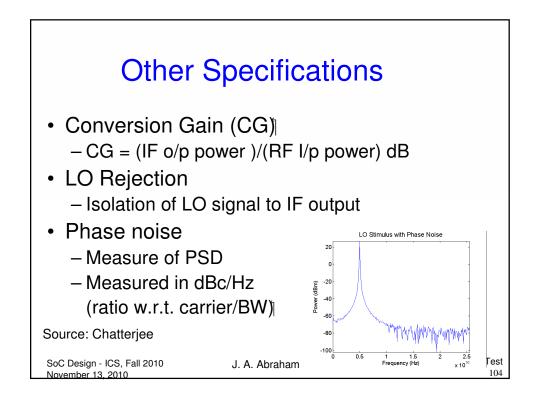

# **RF System Specifications**

- Transmitter

- System Gain, Gain Flatness, System IIP3,

System NF, ACPR, Dynamic range, Modulation quality (Spectral mask), PA switching

- Receiver

- System Gain, System IIP3, System NF, LO Stability, Sensitivity, BER/FER, EVM

Source: Chatterjee

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

SoC Manufacturing Test

Test setup: Gain and IIP3 Gain test setup - Single tone input - Gain =  $20\log_{10}(A/a)$  dB IIP3 test setup - Two tone test  $- IIP3 = a\sqrt{(A/b)}$ OIP3 - Non-linearity test for amplifiers, mixers Also measured for complete systems Source: Chatterjee SoC Manufacturing Test SoC Design - ICS, Fall 2010 J. A. Abraham November 13, 2010

# **Transmitter Specifications**

- Adjacent Channel Power Ratio (ACPR)

- Amount of energy spilled to adjacent bands

- Non-linearity measure of transmitter

- Dynamic Range

- Range of power within which transmitter operates reliably

- Gain Flatness

- Modulation Quality

- The spectral shape of the modulated signal

Source: Chatterjee

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

SoC Manufacturing Test

Desired Channe

Adjacent Channels

# Receiver Specifications

- LO Stability

- Stability of LO frequency w.r.t. time and environment

- Sensitivity

- Minimum signal level that the system can detect with acceptable SNR

- BER/FER

- Error in received bits/frames

- Error Vector Magnitude

- Quality of modulation

- Denoted in %

SoC Design - ICS, Fall 2010

November 13, 2010

Source: Chatterjee

J. A. Abraham

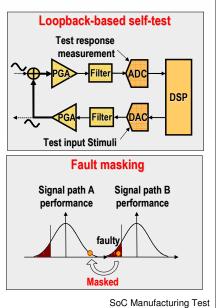

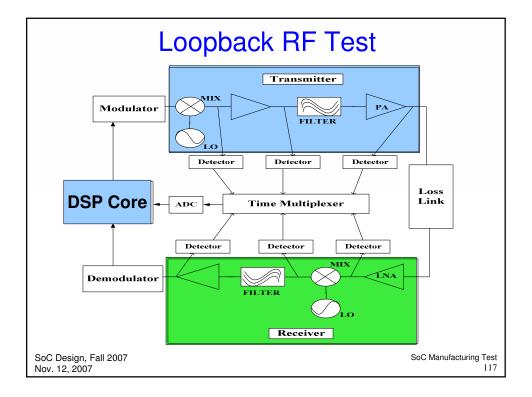

### Loopback-Based Self-Test

- · Test several blocks at the same time using loopback

- Measure the combined performance of path

- Advantages

- Reduced test time

- No performance degradation from insertion of test points

- Limitations

- Combined response of nonfunctionally related paths

- Distortion and noise of signal paths are additive

- Fault masking

- Misclassification

- Need to extract performance parameters of individual signal paths

SoC Design - ICS, Fall 2010

November 13, 2010

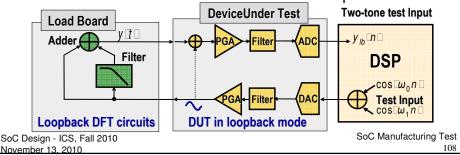

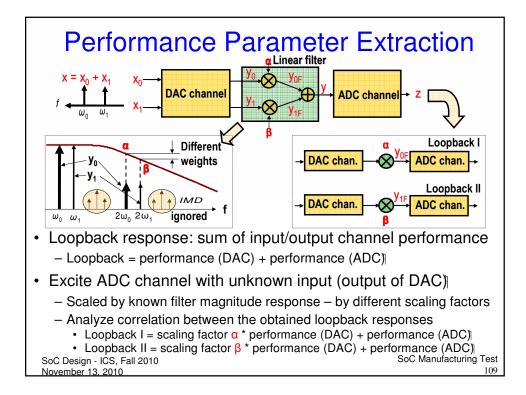

# Loopback + DFT Scheme

- · Provide dynamic performance parameters of individual signal paths

- Avoid yield loss due to fault masking

- DFT circuitry on loadboard or on chip

- Implement analog filter and adder as DFT circuitry

- Reduce silicon cost with minimal pin count (2 dedicated pins)

- · Compatible with existing loopback scheme

- Characterize harmonic distortion and noise parameters

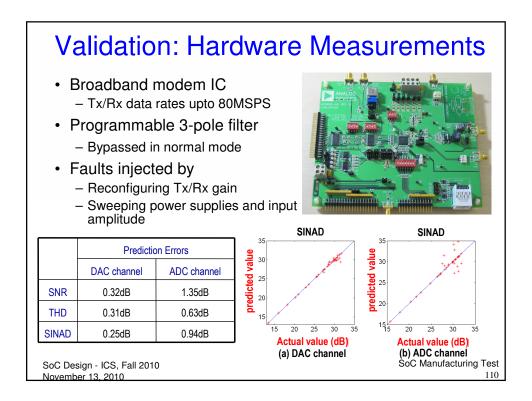

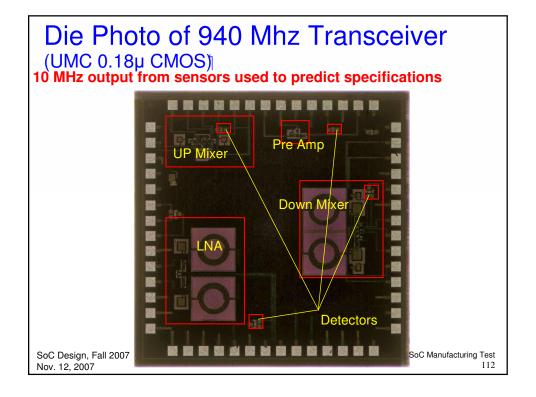

### Measurement Setup

- Agilent E8257D Signal Generator

- Agilent E4448A Spectrum Analyzer

- Tektronix DPO 7104 Digital Oscilloscope

- Many tuning knobs designed

- Almost every bias point can be adjusted to simulate real case chip variations

(mismatch, supply drop etc.).

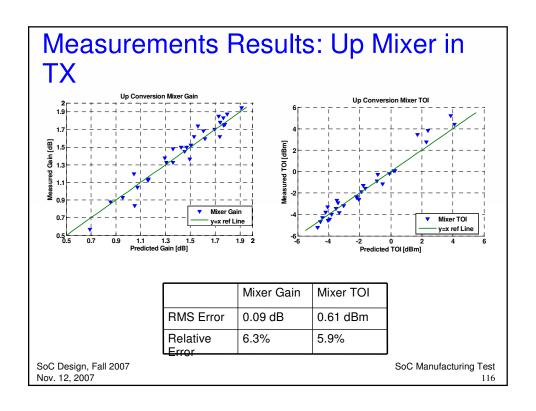

SoC Design, Fall 2007 Nov. 12, 2007

SoC Manufacturing Test

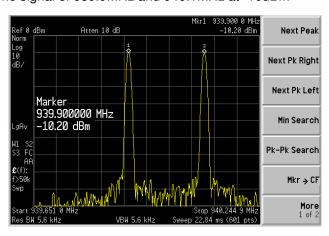

### Test Procedure: Input Signal

• Two tone signal of 939.9MHz and 940.1MHz at -10dBm

- Tone signal selection is not limited to these values

- Depends on chip applications and specifications to be tested

SoC Design, Fall 2007 Nov. 12, 2007

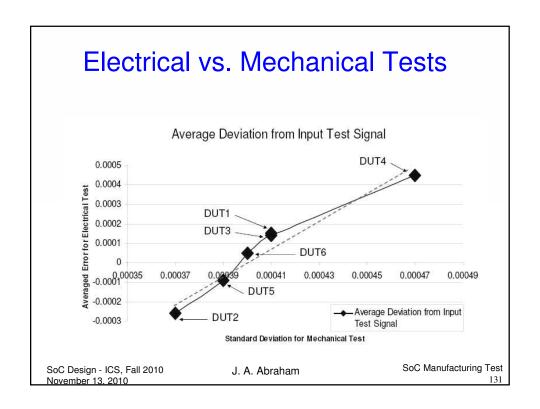

### Testing Non-Electrical Modules – MEMS

- Develop new ways of characterizing and testing MicroElectroMechanical (MEM) systems

- Use gravity to provide mechanical input

- Reduce test time and cost by using electrical tests to characterize and test mechanical subsystem

- Correlate electrical and mechanical tests

- Develop and validate approach with measurements on commercial MEM accelerometer

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

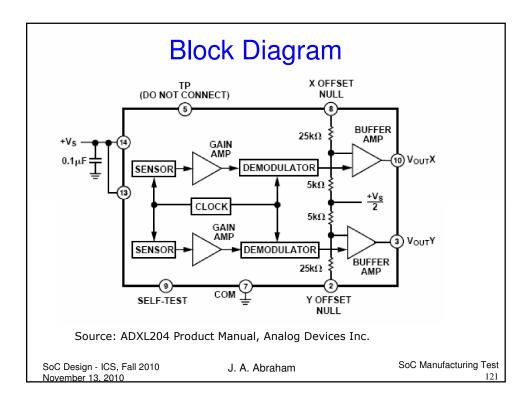

# Target Accelerometer

- Analog Devices ADXL204

- Dual-axis

- Full scale reading of +/- 1.7 g, 0g => 1.65V

- Saturates beyond full scale non-linear response

- MEM Capacitive Transducer

SoC Design - ICS, Fall 2010 November 13, 2010

J. A. Abraham

SoC Manufacturing Test

1

# Capacitor Plates Distance between capacitive plates varies with acceleration C varies with 1/d Source: ADXL204 Product Manual, Analog Devices Inc. SoC Design - ICS, Fall 2010 J. A. Abraham SoC Manufacturing Test November 13, 2010

# **Accelerometer Function**

- Simple first-order model

- · Variation in plate spacing due to displacement, d (caused by an applied acceleration), produces a voltage on output pin

- $\delta V/d$

SoC Design - ICS, Fall 2010 November 13, 2010

J. A. Abraham

### Conventional Mechanical Stimulus

- "Shaker": standardized acceleration generator

- Compare output voltage with expected value from standard acceleration

- Expensive

- Turn-table: centrifugal force

- Centrifugal acceleration from rotation

- Also expensive

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

SoC Manufacturing Test

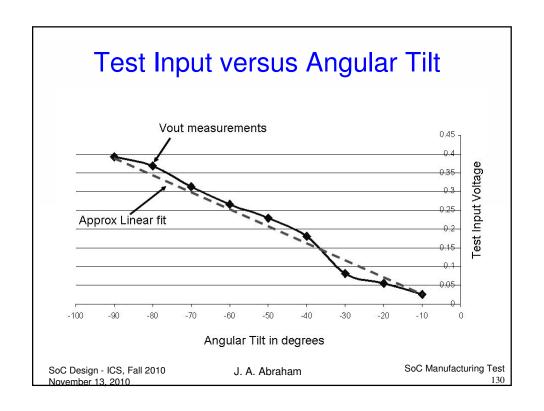

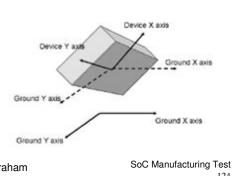

### Our Mechanical Stimulus

- · Uses fact that the DUT is a dual axis device

- Tilt device to change acceleration due to gravity (g=9.81m/s²) on different axes

- 1.65 V when horizontal

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

12

# Methodology

- Measure  $V_x$  and  $V_y$  for  $\theta x=0^{\circ}$ ,  $\theta y=0^{\circ}$

- Change the orientation of the DUT physically, imparting a gravitational acceleration component on it

- $g_{x\_eff} = g(sin\theta_x + cos\theta_x)$

- $g_{y_eff} = g(sin\theta_y + cos\theta_y)$

- Obtain marker points and interpolate to obtain a curve

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham

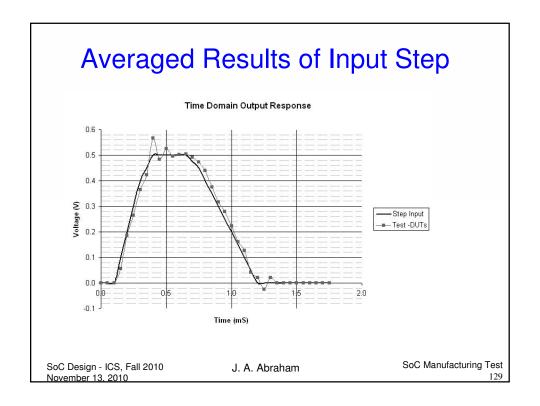

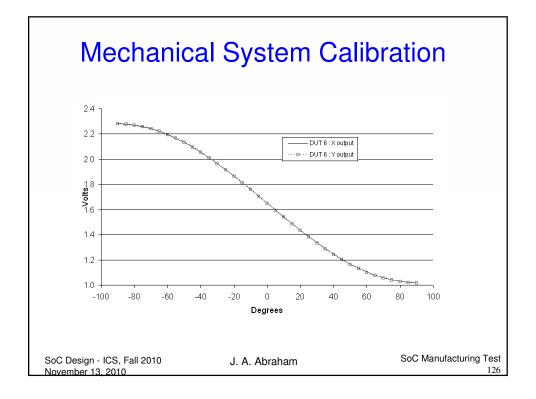

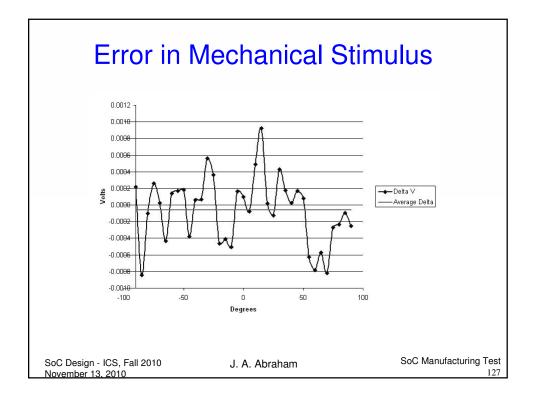

# Calibration using Electrical Test

- Unit has test input pin connected to capacitor elements

- Applied electrical signal produces electrostatic force, producing displacement

- · Resulting change in output voltage

- Measurements of result of input step

- 10,000 runs for each DUT

- National Instruments platform

SoC Design - ICS, Fall 2010 November 13, 2010 J. A. Abraham