### 2. Transistors, Fabrication, Layout

Jacob Abraham

Department of Electrical and Computer Engineering

The University of Texas at Austin

VLSI Design Fall 2020

September 1, 2020

ECE Department, University of Texas at Austin

Lecture 2. Transistors, Fabrication, Layout

Jacob Abraham, September 1, 2020 1 /

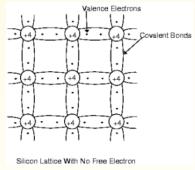

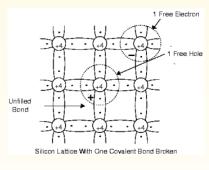

### Conductivity in Silicon Lattice

### Look at the behavior of crystalline silicon

- At temperatures close to 0 K, electrons in outermost shell tightly bound (insulator)

- At higher temps., (300 K), some electrons have thermal energy to break covalent bonds

CE Department, University of Texas at Austi

Lecture 2. Transistors, Fabrication, Layout

Jacob Abraham, September 1, 2020

Department of Electrical and Computer Engineering, The University of Texas at Austin J. A. Abraham, September 1, 2020

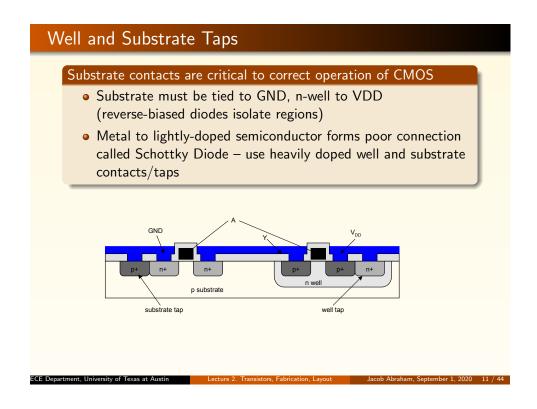

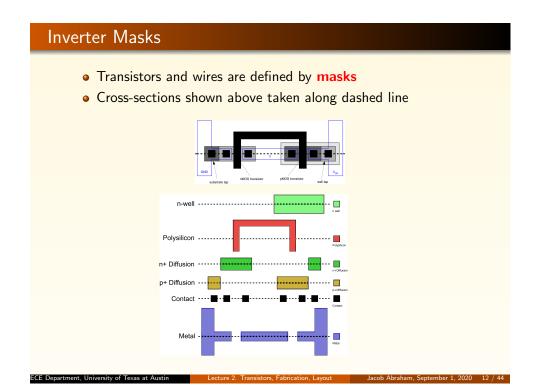

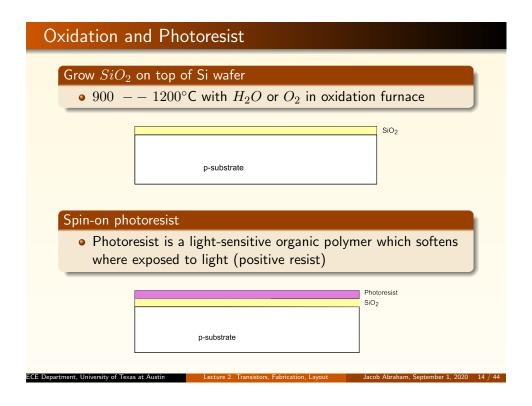

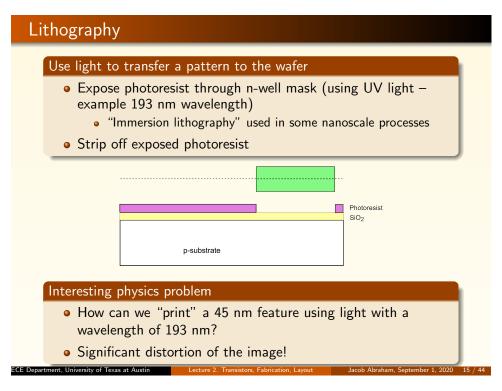

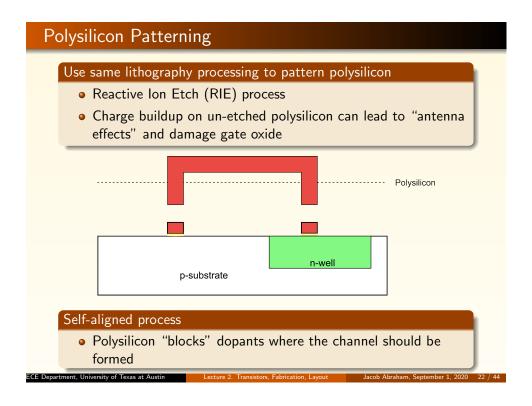

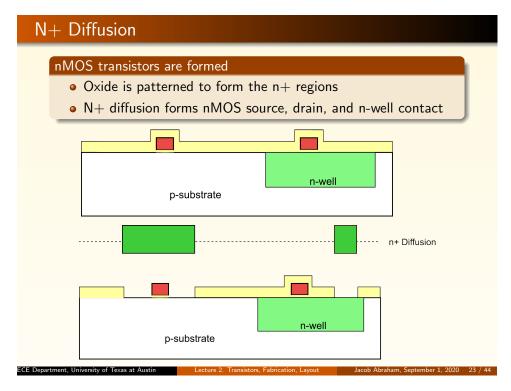

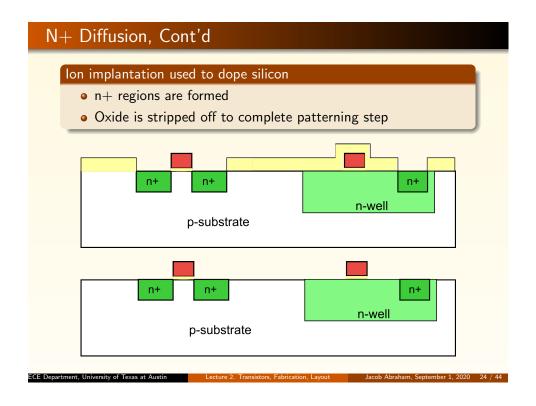

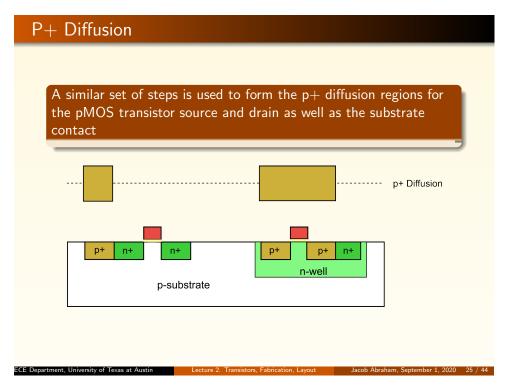

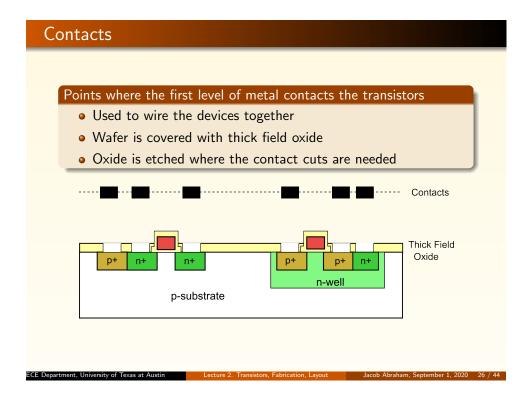

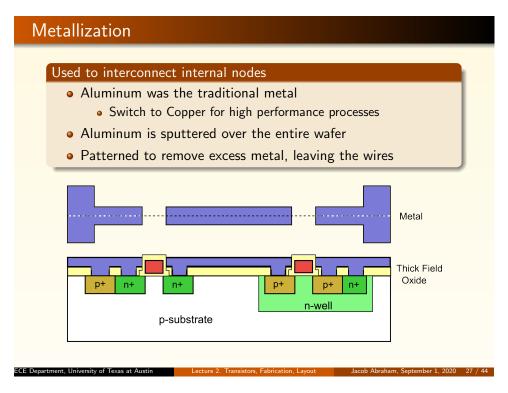

# Silicon technology CMOS transistors are fabricated on silicon wafer Lithography process similar to printing press On each step, different materials are deposited or etched Easiest to understand by viewing both top and cross-section of wafer in a simplified manufacturing process Example inverter cross-section Typically use p-type substrate for nMOS transistors Requires n-well for body of pMOS transistors Requires n-well for body of pMOS transistors

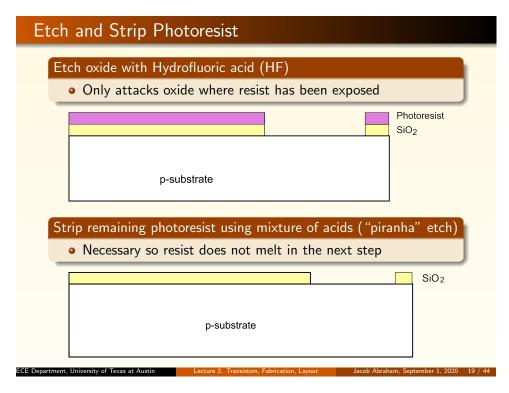

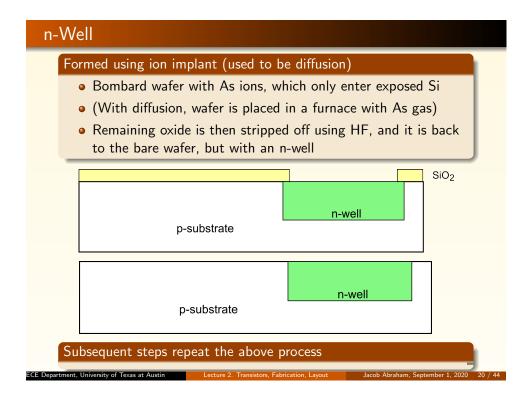

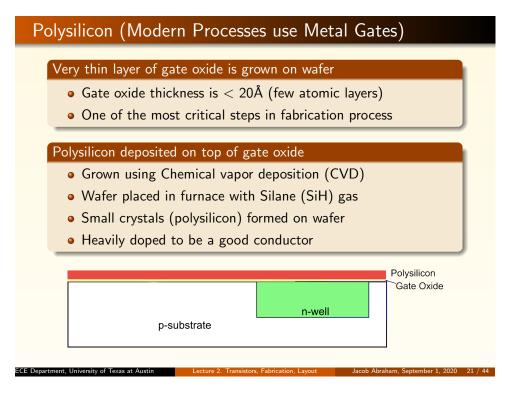

### Examples of Fabrication Steps A VERY simplified description illustrating the major step – modern processes follow these basic steps, but are much more complex • Start with blank wafer • Build inverter from the bottom up First step is to form the n-well • Cover wafer with protective layer of $SiO_2$ (oxide) • Remove layer where n-well should be built • Implant or diffuse n dopants into exposed wafer • Strip off $SiO_2$

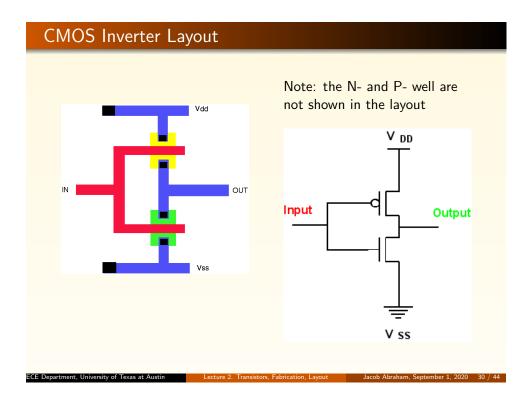

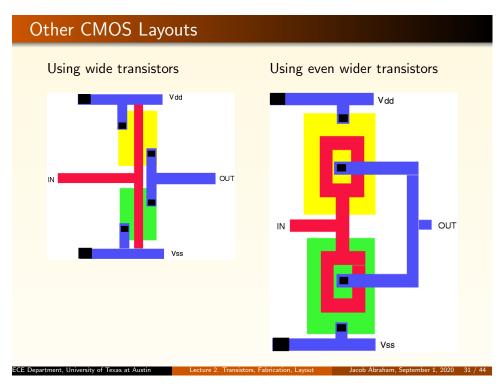

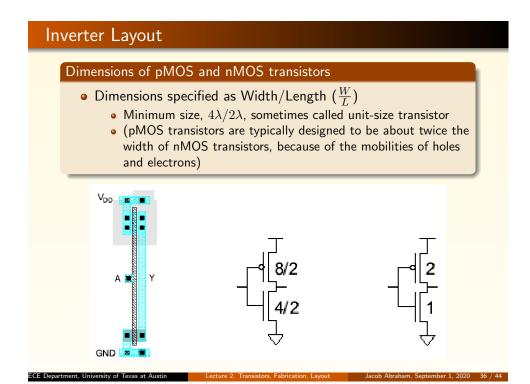

### Layout

- Describes actual layers and geometry on the silicon substrate to implement a function

- Need to define transistors, interconnection

- Transistor widths (for performance)

- Spacing, interconnect widths, to reduce defects, satisfy power requirements

- Contacts (between poly or active and metal), and vias (between metal layers)

- Wells and their contacts (to power or ground)

- Layout of lower-level cells constrained by higher-level requirements: floorplanning

- "design iteration"

ECE Department, University of Texas at Austin

Lecture 2. Transistors, Fabrication, Layout

Jacob Abraham, September 1, 2020 28

### Layout, Cont'd

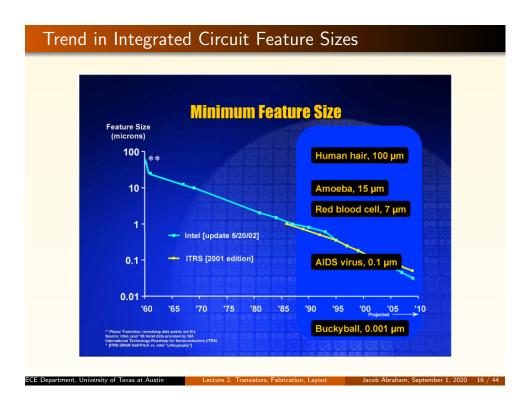

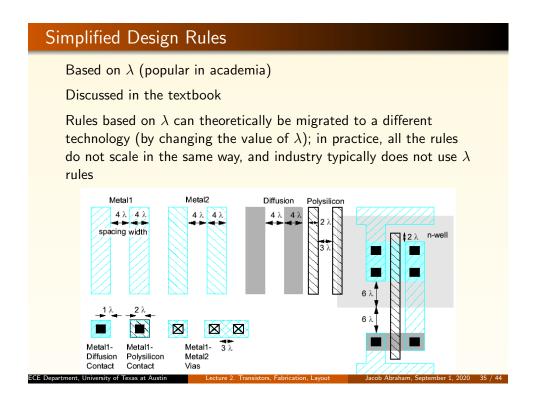

- Chips are specified with set of masks

- Minimum dimensions of masks determine transistor size (and hence speed, cost, and power)

- Feature size f = distance between source and drain

- Set by minimum width of polysilicon (= minimum "drawn" gate length)

- Feature size improves 30% every 3 years or so

- Normalize for feature size when describing design rules

- Express rules in terms of  $\lambda = f/2$

- $\bullet$  e.g.,  $\lambda=0.3\mu m$  in  $0.6\mu m$  process

CE Department, University of Texas at Austin

Lecture 2. Transistors, Fabrication, Layout

Jacob Abraham, September 1, 2020 29 /

# Stick diagrams identify actual layers (which a schematic does not); both can be annotated with transistor sizes n- and p-wells are shown metal-p-diff via metal-p-diff via metal-p-diff via metal-p-diff via p-type transistor a NAND b metal-p-type transist

### The MOSIS Scalable CMOS Rules

MOSIS is a prototyping and small-volume production service for VLSI circuit development

- MOSIS keeps costs down by combining many designs on a single die (multi-project chips)

- Similar facilities exist in Europe (Europractice, CMP), Taiwan, etc.

- $\lambda$ -based rules

- Designs using these rules are fabricated by a variety of companies

- Support for submicron digital CMOS, analog (buried poly layer for capacitor), micromachines, etc.

- https://www.mosis.com/files/scmos/scmos.pdf

CE Department, University of Texas at Austin

Lecture 2. Transistors, Fabrication, Layout

Jacob Abraham, September 1, 2020

37 / 44

### Nangate 45nm Open Cell Library

### Used in the laboratory exercises

- This is an open-source, standard-cell library

- To aid university research programs and other organizations in developing design flows, designing circuits and exercising new algorithms

- Link to the wiki:

http://www.eda.ncsu.edu/wiki/FreePDK45:Contents

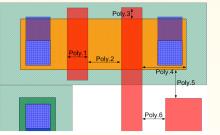

• Example: poly rules (note: summarized here)

| Rule | Value  | Description     |

|------|--------|-----------------|

| 1    | 50 nm  | Minimum width   |

| 2    | 140 nm | Minimum spacing |

| 3    | 55 nm  | Min. extension  |

| 4    | 70 nm  | Min. enclosure  |

| 5    | 50 nm  | Min. spacing    |

| 6    | 75 nm  | Min. spacing    |

ECE Department, University of Texas at Austin

Lecture 2. Transistors, Fabrication, Lavou

acob Abraham, September 1, 2020 38 / 44

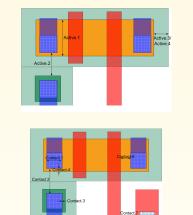

### Example of Other Design Rules: Nangate 45nm

### Active Rules Rule Value Description 1 90 nm Minimum width 2 80 nm Minimum spacing 3 - Min. well-active 4 - active inside

| Contact Rules |       |                        |

|---------------|-------|------------------------|

| Rule          | Value | Description            |

| 1             | 65 nm | Minimum width          |

| 2             | 75 nm | Minimum spacing        |

| 3             | _     | contact inside         |

| 4             | 5 nm  | Min. active around     |

| 5             | 5 nm  | Min. poly around       |

| 6             | 35 nm | Min. spacing with gate |

| 7             | 90 nm | Min. spacing with poly |

|               |       |                        |

ECE Department, University of Texas at Austin

Lecture 2. Transistors, Fabrication, Layout

Jacob Abraham, September 1, 2020

39 / 44

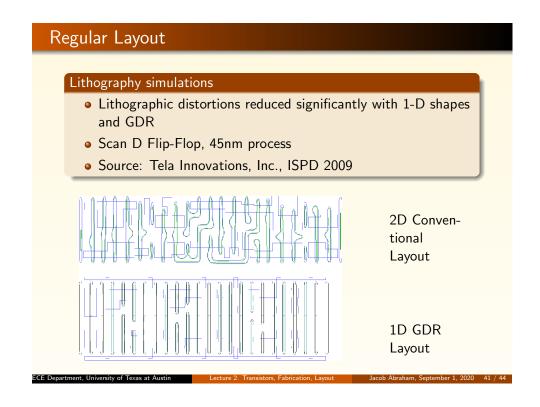

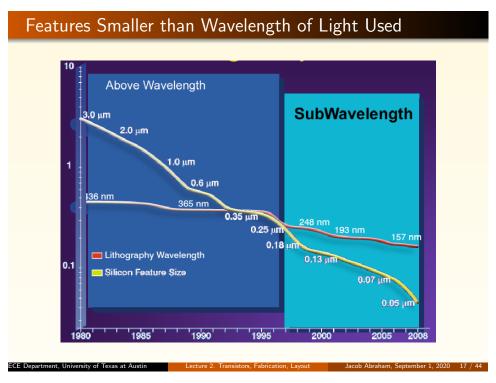

### Improve manufacturability Less flexibility for designers Intel reduced the number of poly layout rules for logic layout in 45nm by 37% compared with the 65 nm process Highly regular layout greatly reduces lithographic distortions Limit rules, thereby limiting the number of allowed structures and shape relationships Move towards 1-dimensional shapes and "Gridded Design Rules" (GDR) Example layout from Tela Innovations Example layout from Tela Innovations