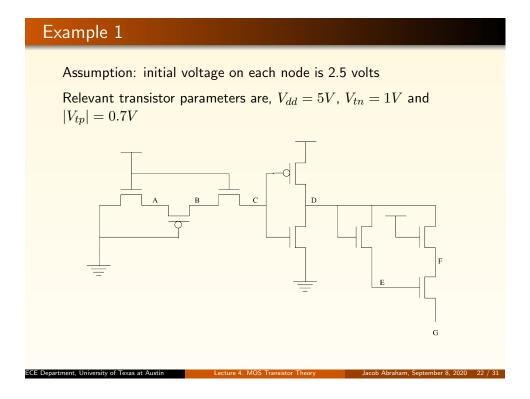

# 4. MOS Transistor Theory

Jacob Abraham

Department of Electrical and Computer Engineering

The University of Texas at Austin

VLSI Design Fall 2020

September 8, 2020

ECE Department, University of Texas at Austin

Lecture 4. MOS Transistor Theory

Jacob Abraham, September 8, 2020 1

# Electrical Properties

Necessary to understand basic electrical properties of the MOS transistor to design useful circuits

- Deal with non-ideal devices

- Ensure that the circuits are robust

- Create working layouts

- Predict delays and power consumption

As circuit dimensions scale down, electrical effects become more important, even for digital circuits

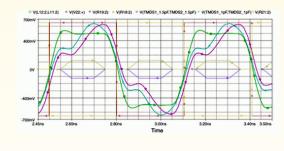

1.65 GHz square wave from an HDMI Interface (Source: Dunnihoo, *EE Times Asia*, 8/25/2005)

ECE Department, University of Texas at Austin

Lecture 4. MOS Transistor Theory

Jacob Abraham, September 8, 2020 1

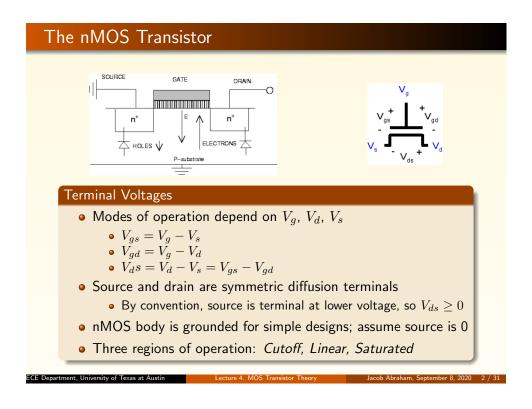

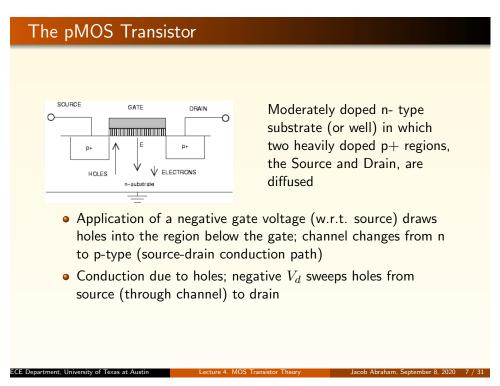

#### nMOS Transistor Operation

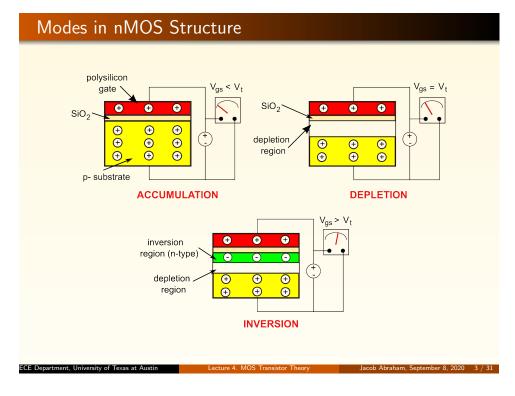

Positive voltage on Gate produces electric field across substrate attracts electrons to the Gate and repels holes

- With sufficient voltage, region under Gate changes from p- to n-Type – conducting path between the Source and Drain

- Inversion layer is field-induced junction, unlike a PN junction which is metallurgical

- Horizontal component of electric field associated with  $V_{ds} > 0$ is responsible for sweeping electrons from channel to drain

#### Threshold Voltage

- The gate voltage at which conduction takes place is the Threshold Voltage,  $V_t$

- Current flow occurs when the drain to source voltage  $V_{ds} > 0$ , and consists almost entirely of majority-carriers (electrons), that flow through the channel

- A depletion region insulates the channel from the substrate

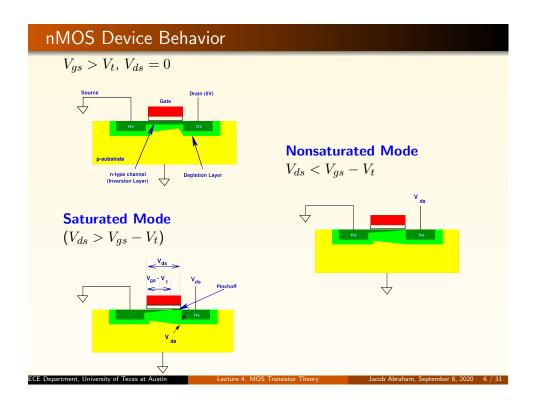

# Conducting nMOS Transistor

- Conduction when  $V_{gs} > V_t$  and  $V_{ds} > 0$

- No significant current through the substrate because of reverse biased PN junction with the channel

- As the voltage from drain to source is increased, the resistive drop along the channel begins to change the shape of the channel characteristic

- At source end of the channel, the full gate voltage is effective in inverting the channel

- At drain end of the channel, only the difference between the gate and the drain voltage is effective

- ullet If  $V_{ds} > V_{gs} V_t$ , then  $V_{gd} < V_t$ , and the channel is "pinched down" (the inversion layer no longer reaches the drain)

- In this case, conduction is brought about by the drift mechanism of electrons under the influence of positive drain voltage; as the negative electrons leave the channel, they are accelerated towards the drain

- Voltage across the pinchdown channel tends to remain fixed at  $(V_{gs} - V_t)$ , and the channel current remains constant with increasing  $V_{ds}$

### Current in the Channel

In the Linear region,  $I_{ds}$  depends on how much charge there is in the channel and how fast the charge is moving

#### Channel Charge

- MOS structure looks like parallel plate capacitor while operating in inversion (Gate – Oxide – Channel)

- $Q_{channel} = CV$

- $C = C_q = \epsilon_{ox} W L / t_{ox} = C_{ox} W L (C_{ox} = \epsilon_{ox} / t_{ox})$

- $V = V_{gc} V_t = (V_{gs} V_{ds}/2) V_t$

ECE Department, University of Texas at Austin

Lecture 4. MOS Transistor Theory

Jacob Abraham, September 8, 2020 8 /

# Carrier Velocity

- Charge is carried by electrons

- $\bullet$  Carrier velocity  $\nu$  proportional to lateral E- field between source and drain

- $\bullet$   $\nu = \mu E$

- μ is called mobility

- $E = V_{ds}/L$

- Time for carrier to cross channel:  $t = L/\nu$

CE Department, University of Texas at Austin

Lecture 4. MOS Transistor Theory

Jacob Abraham, September 8, 2020 9,

### **I-V** Characteristics

#### nMOS Linear I-V

Current can be obtained from charge in channel and the time t each carrier takes to cross

$$I_{ds} = \frac{Q_{channel}}{t}$$

$$= \mu C_{ox} \frac{W}{L} (V_{gs} - V_t - V_{ds}/2) V_{ds}$$

$$= \beta (V_{gs} - V_t - V_{ds}/2) V_{ds}$$

#### nMOS Saturation I-V

- $\label{eq:continuous} \begin{tabular}{l} \bullet & \mbox{If } V_{gd} < V_t \mbox{, channel pinches off near drain} \\ \bullet & \mbox{when } V_{ds} > V_{dsat} = V_{gs} V_t \end{tabular}$

- Now drain voltage no longer increases with current

$$I_{ds} = \beta \left( V_{gs} - V_t - V_{dsat}/2 \right) V_{dsat}$$

$$= \frac{\beta}{2} (V_{gs} - V_t)^2$$

ECE Department, University of Texas at Austin

Lecture 4. MOS Transistor Theory

Jacob Abraham, September 8, 2020 10

# nMOS I-V Summary

Shockley First Order transistor models

$$I_{ds} = \left\{ \begin{array}{cccc} 0 & V_{gs} & < & V_t & \text{Cutoff} \\ \beta \left(V_{gs} - V_t - V_{ds}/2\right) V_{ds} & V_{ds} & < & V_{dsat} & \text{Linear} \\ \frac{\beta}{2} (V_{gs} - V_t)^2 & V_{ds} & > & V_{dsat} & \text{Saturation} \end{array} \right.$$

CE Department, University of Texas at Austin

Lecture 4. MOS Transistor Theory

acob Abraham, September 8, 2020 11 /

# pMOS I-V

# All dopings and voltages are inverted for pMOS (compared with nMOS)

- Mobility  $\mu_p$  is determined by holes

- ullet Typically 2x-3x lower than that of electrons  $\mu_n$

- Thus pMOS must be wider to provide the same current

- Simple assumption,  $\frac{\mu_n}{\mu_p} = 2$

ECE Department, University of Texas at Austin

Lecture 4. MOS Transistor Theory

Jacob Abraham. September 8, 2020 12

12 / 31

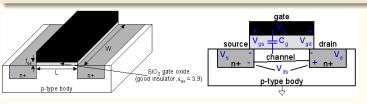

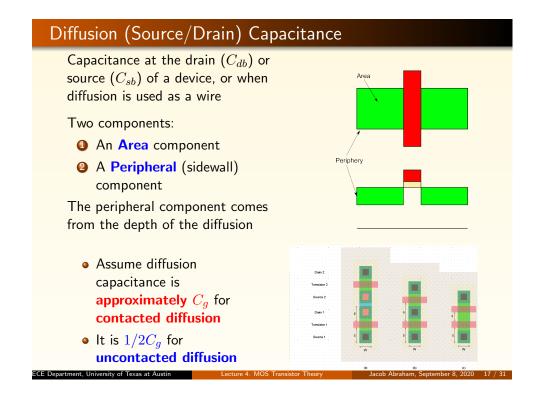

# Capacitance

#### Capacitance in CMOS circuits

- Two conductors separated by an insulator have capacitance

- Gate to channel capacitor is very important

- Creates channel charge necessary for operation

- Source and drain have capacitance to body

- Across reverse-biased diodes

- Called diffusion capacitance because it is associated with source/drain diffusion

- Interconnection wires also have (distributed) capacitance

#### Gate Capacitance

- Approximate channel as connected to source

- $C_{gs} = \epsilon_{ox}WL/t_{ox} = C_{ox}WL = C_{permicron}W$

- Typical  $C_{permicron} \approx 2 \mathrm{fF}/\mu\mathrm{m}$

$\begin{array}{c|c} & & & \\ & & & \\ \hline & & \\ & & \\ & & \\ \hline & & \\ & & \\ & & \\ \hline & & \\ \hline & & \\ & & \\ \hline & & \\ \hline & & \\ \hline & & \\ & & \\ \hline & & \\$

ECE Department, University of Texas at Austin

Lecture 4. MOS Transistor Theory

Jacob Abraham, September 8, 2020 13,

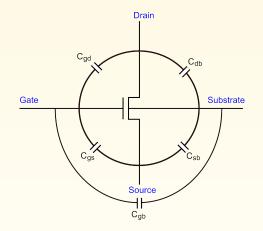

# **Device Capacitances**

The **dynamic response** (switching speed) of a CMOS circuit is very dependent on parasitic capacitances associated with the circuit

Use a simple approximation for quick estimates of capacitances; use tools for extraction of more accurate values from actual layouts

Consider the capacitances seen during the different regions of operation

CE Department, University of Texas at Austin

Lecture 4. MOS Transistor Theory

ob Abraham, September 8, 2020 14 / 3

14 / 31

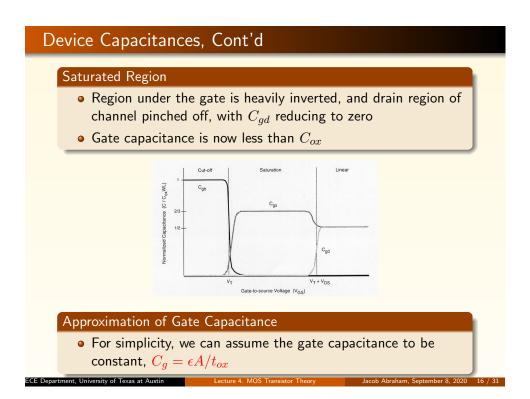

# Device Capacitances, Cont'd

#### Off Region

- $V_{gs} \leq V_t$ ; when the MOS device is off, only  $C_{gb}$  (due to the series combination of gate oxide and depletion layer capacitance) is non-zero.

- $C_{gb}=C_{ox}=\epsilon A/t_{ox}$ , where A is the gate area, and  $\epsilon=\epsilon_0\epsilon_{SiO_2}$

- $\epsilon_0$  is the permittivity of free space (8.854  $\times$  10<sup>4</sup> F/m), and  $\epsilon_{SiO_2}$  is the dielectric constant of  $SiO_2$  (about 3.9)

#### Linear Region

- $\bullet$  Depletion region exists, forming dielectric of depletion capacitance,  $C_{dep}$  in series with  $C_{ox}$

- As the device turns on,  $C_{qb}$  reduces to 0

- The gate capacitance is now a function of the gate voltage

CE Department, University of Texas at Austin

Lecture 4. MOS Transistor Theory

Jacob Abraham, September 8, 2020 15,

15 / 31

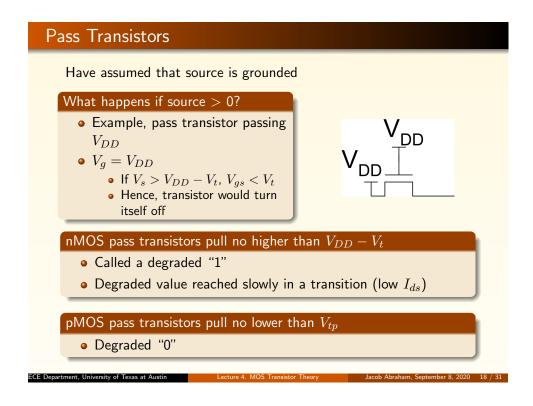

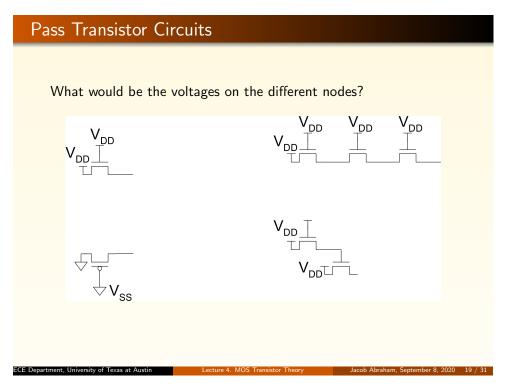

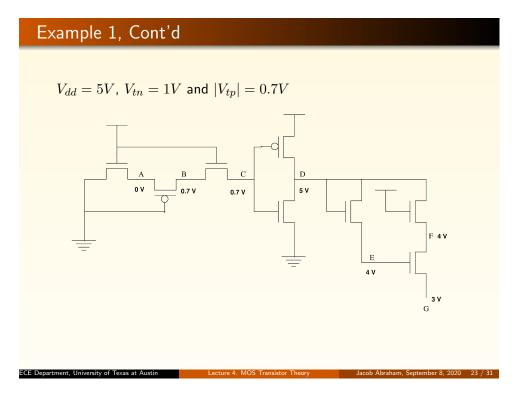

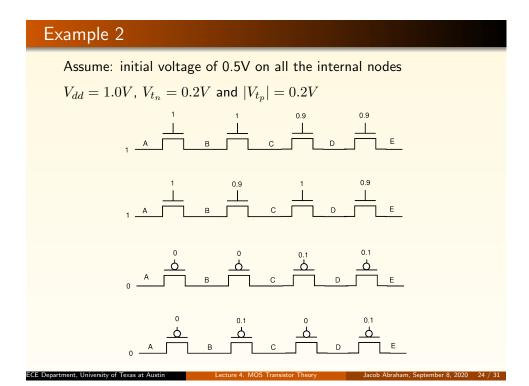

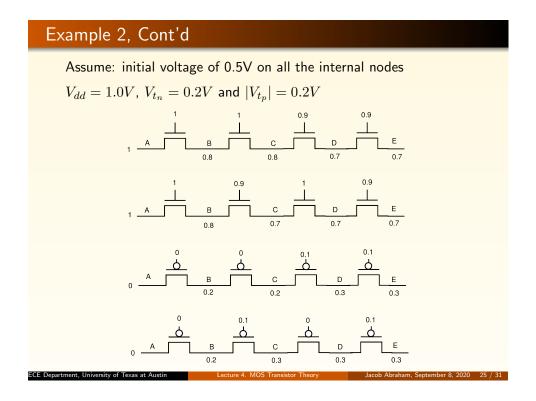

### Pass Transistor Circuits

What would be the voltages on the different nodes?

$$V_{DD}$$

ECE Department, University of Texas at Austin

Lecture 4. MOS Transistor Theory

Jacob Abraham, September 8, 2020 20 / 3

# Pass Transistor Circuits

What would be the voltages on the different nodes?

$$V_{DD}$$

CE Department, University of Texas at Austin

Lecture 4. MOS Transistor Theory

Jacob Abraham, September 8, 2020 21 /

#### Effective Resistance

#### Resistance of a bar of uniform material

- $R = \frac{\rho \times L}{A} = \left(\frac{\rho}{t}\right) \left(\frac{L}{W}\right)$

- ullet where ho= resistivity of the material

- $\bullet$  A = cross-section of the resistor

- ullet t,W= thickness, width of the material

- The channel resistance of a MOS transistor in the linear region,  $R_c = k\left(\frac{L}{W}\right)$ ,

- where  $k=\frac{1}{\mu C_{ox}(V_{gs}-V_t)}$

#### Resistance values depend on the technology

- Obtain the information from the technology files

- Sheet resistance  $(\Omega/\Box)$

- Lowest for metal, increases for poly, active, highest for Well

- Contact (via) resistance becomes more important as processes scale down

- Channel (turned-on transistor) on the order of 1000  $\Omega/\Box$

ECE Department, University of Texas at Austin

Lecture 4. MOS Transistor Theory

Jacob Abraham, September 8, 2020 26 / 31

# Example: TSMC 0.18 \( \mu\) process http://www.europractice-ic.com/technologies\_TSMC.php Look at one process Example of SPICE simulation | Selection | Selecti

### Resistance on a Turned-On Transistor

# Circuit delay depends on resistance and capacitance – delay depends on RC

- Need to deal with the resistance of conducting transistors and interconnects

- Shockley models have limited value for obtaining resistance

- Not accurate enough for modern transistors

- Too complicated for much hand analysis

- Simplification: treat transistor as resistor

- Replace  $I_{ds}(V_{ds}, V_{qs})$  with effective resistance R

- $I_{ds} = \frac{V_{ds}}{R}$

- R averaged across switching of digital gate

- Too inaccurate to predict current at any given time, but good enough to predict RC delay

- More accurate values of delay obtained from detailed design using the tools

ECE Department, University of Texas at Austin

Lecture 4. MOS Transistor Theory

acob Abraham. September 8, 2020 28 / 3

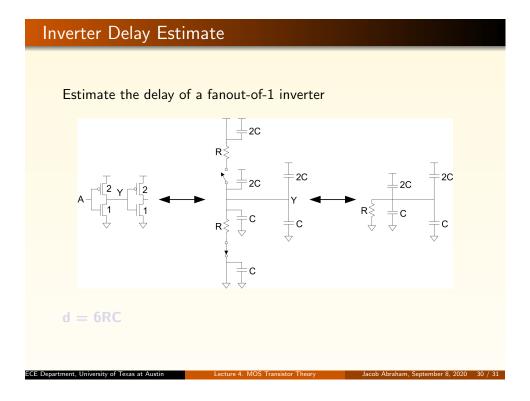

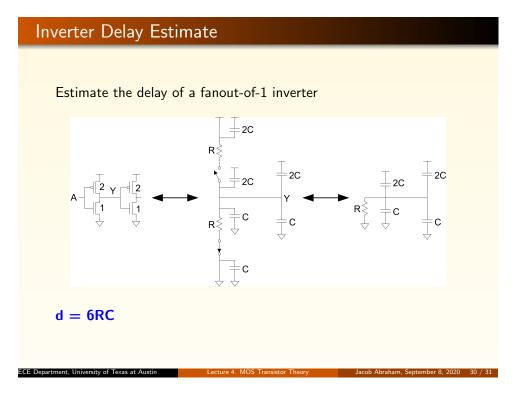

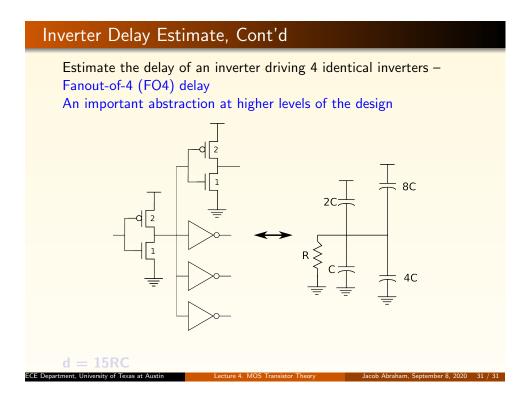

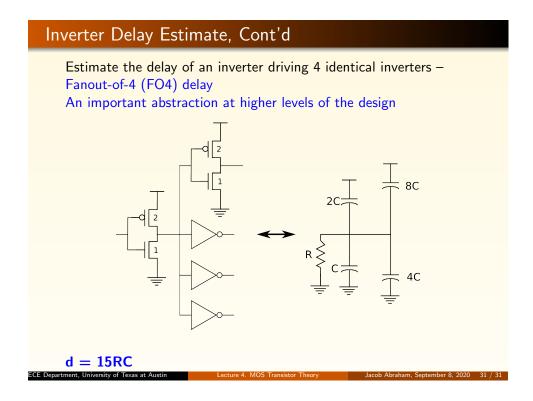

# RC Delay Model

#### Use equivalent circuits for MOS transistors

- Ideal switch + capacitance and ON resistance

- Unit nMOS has resistance R, capacitance C

- Unit pMOS has resistance 2R, capacitance C

- Capacitance proportional to width

- Resistance inversely proportional to width

CE Department, University of Texas at Austin

Lecture 4. MOS Transistor Theory

Jacob Abraham, September 8, 2020 29 / 3