Introduction

|

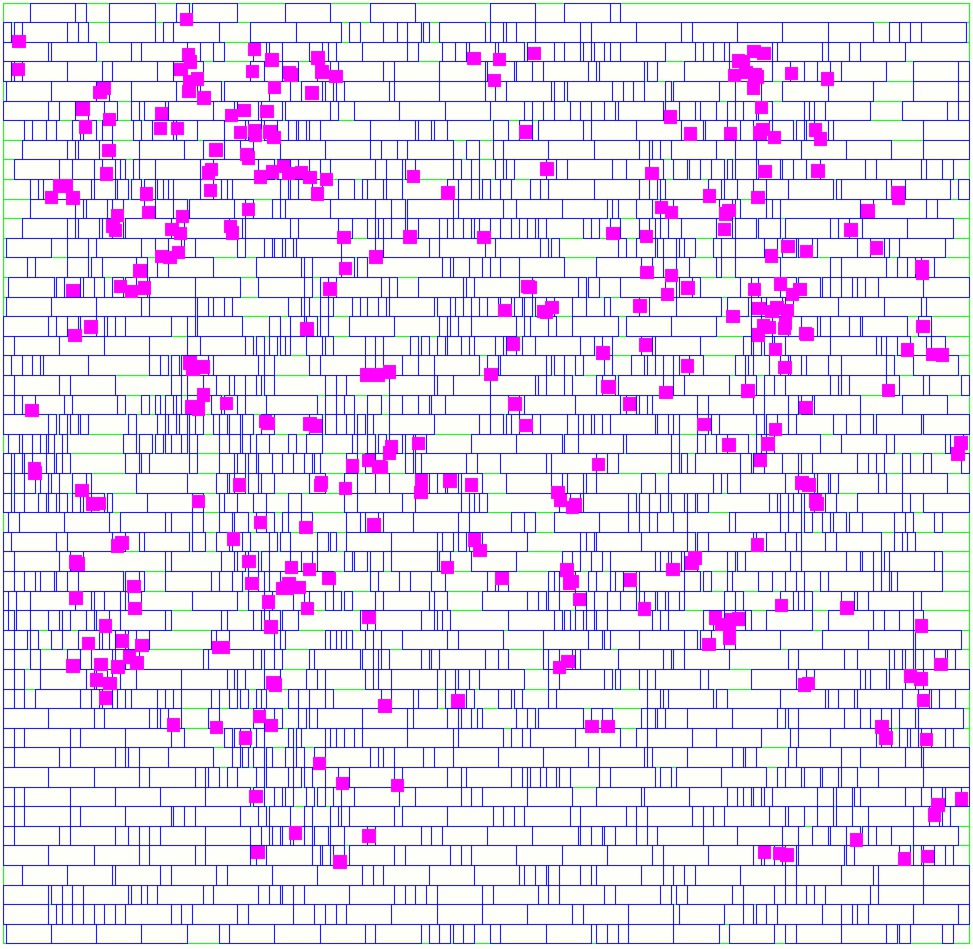

We present TPLPlace, a triple patterning lithography aware detailed placement solver. |

Benchmarks

SPARC 95 Benchmarks: ASCII format

SPARC 70/80/85/90 NanGate 15nm Benchmarks: LEF/DEF format

Publications

Yibo Lin, Bei Yu, Biying Xu and David Z. Pan, “Triple patterning aware detailed placement toward zero cross-row middle-of-line conflict”, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol.36, no.7, pp.1140–1152, 2017.

Yibo Lin, Bei Yu, Biying Xu and David Z. Pan, “Triple Patterning Aware Detailed Placement Toward Zero Cross-Row Middle-of-Line Conflict”, IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Austin, TX, Nov. 2–6, 2015.

Bei Yu, Xiaoqing Xu, Jhih-Rong Gao, Yibo Lin, Zhuo Li, Charles Alpert, and David Z. Pan, “Methodology for Standard Cell Compliance and Detailed Placement for Triple Patterning Lithography”, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol.34, no.5, pp.726–739, 2015.

Bei Yu, Xiaoqing Xu, Jhih-Rong Gao, and David Z. Pan, “Methodology for Standard Cell Compliance and Detailed Placement for Triple Patterning Lithography”, IEEE/ACM International Conference on Computer-Aided Design (ICCAD), San Jose, CA, November 18–21, 2013. (William J. McCalla Best Paper Award)

Contact

TPLPlace is developed by Yibo Lin, Bei Yu, and Prof. David Z. Pan. Please contact us with any bug reports and comments.