# EE382V-ICS: System-on-a-Chip (SoC) Design

### **Lecture 8 - System Design Methodology**

with sources from: Christian Haubelt, Univ. of Erlangen-Nuremberg

#### Andreas Gerstlauer

Electrical and Computer Engineering University of Texas at Austin gerstl@ece.utexas.edu

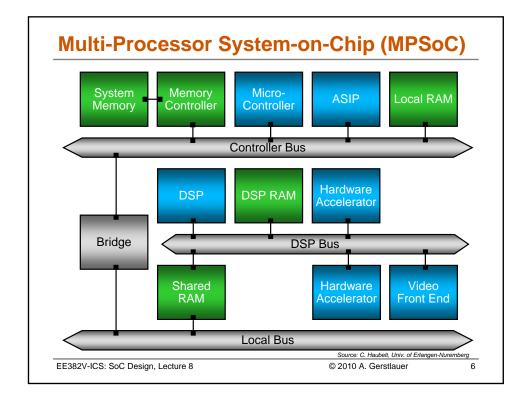

# **MPSoC Terminology**

- Multi-processor

- Heterogeneous, asymmetric multi-processing (AMP)

- · Distributed memory and operating system

- Multi-core

- Homogeneous, symmetric multi-processing (SMP)

- · Shared memory and operating system

- ➤ Multi-core processors in a multi-processor system

- Many-core

- > 10 cores per processor...

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

7

### **Lecture 8: Outline**

- ✓ Introduction

- System design methodology

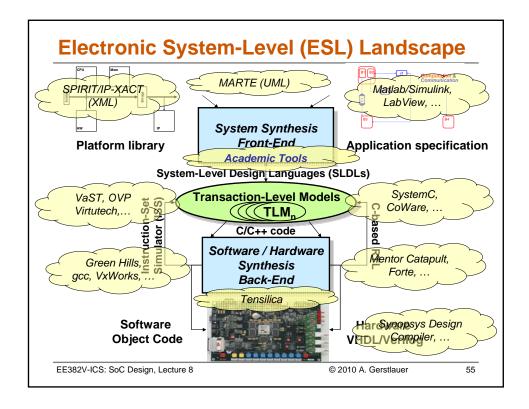

- Electronic system-level design (ESL/SLD)

- ESL design

- Modeling

- Synthesis

- Verification

- ESL landscape

- Summary and conclusions

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

9

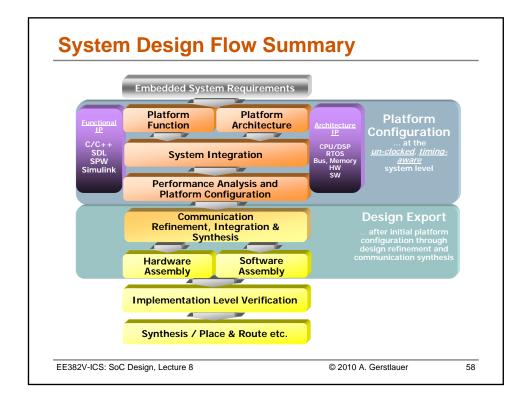

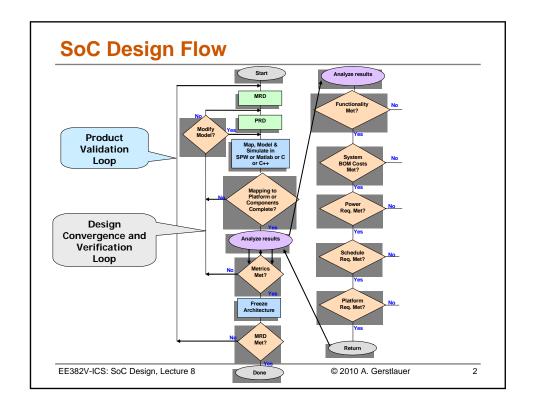

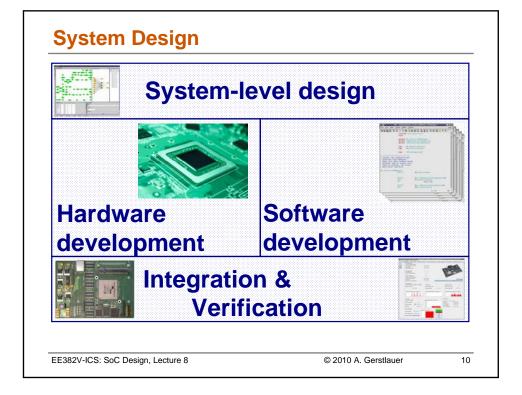

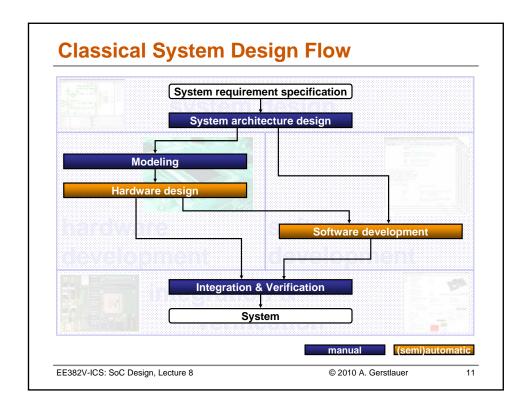

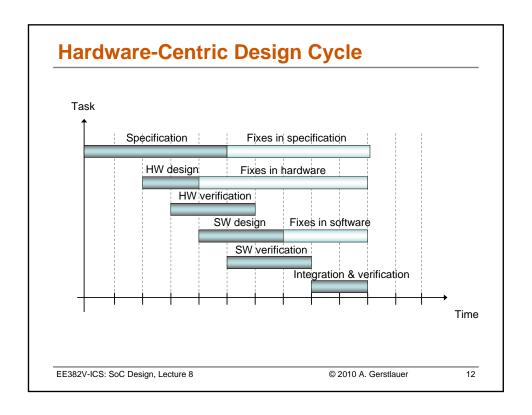

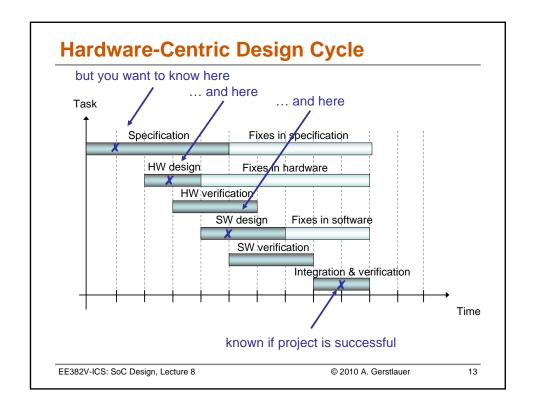

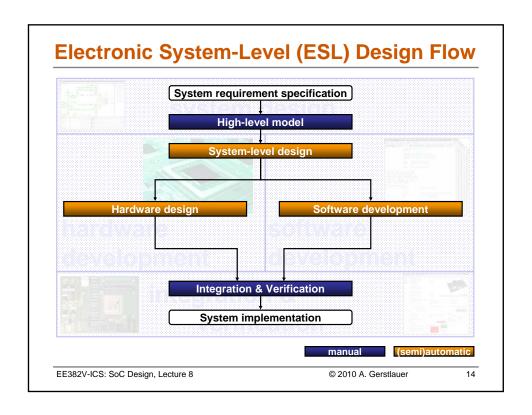

# **Design Methodologies**

### > Set of models and design steps (transformations)

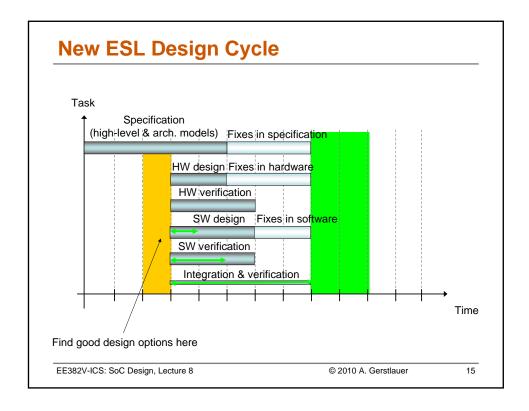

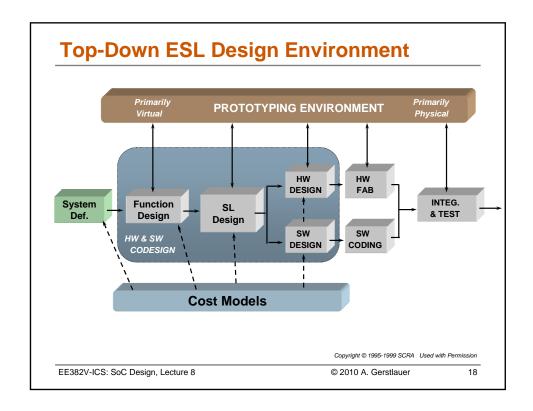

#### Top down design

- Starts with functional system specification

- Application behavior

- Models of Computation (MoC)

- Successive refinement

- Connect the hardware and software design teams earlier in the design cycle.

- Allows hardware and software to be developed concurrently

- Goes through architectural mapping

- The hardware and software parts are either manually coded or obtained by refinement from higher model

- Ends with HW-SW co-verification and System Integration

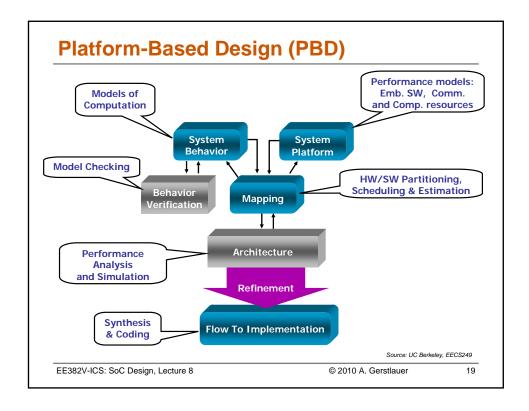

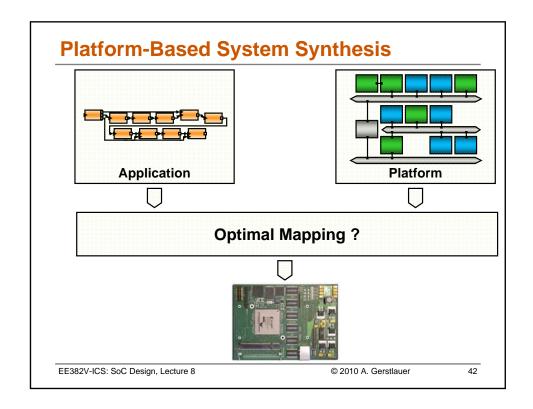

### Platform based design

- Starts with architecting a processing platform for a given vertical application space

- Semiconductor, ASSP vendors

- Enables rapid creation and verification of sophisticated SoC designs variants

- PBD uses predictable and preverified firm and hard blocks

- PBD reduces overall time-tomarket

- Shorten verification time

- Provides higher productivity through design reuse

- PBD allows derivative designs with added functionality

- Allows the user to focus on the part that differentiate his design

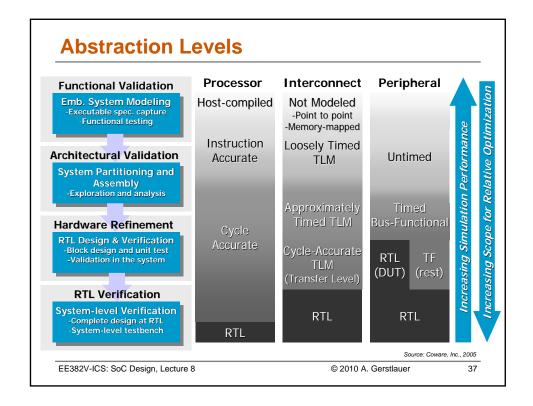

Source: Coware, Inc., 2005

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

17

# **System Design Languages**

- Netlists

- Structure only: components and connectivity

- ➤ Gate-level [EDIF], system-level [SPIRIT/XML]

- Hardware description languages (HDLs)

- Event-driven behavior: signals/wires, clocks

- Register-transfer level (RTL): boolean logic

- ➤ Discrete event [VHDL, Verilog]

- System-level design languages (SLDLs)

- Software behavior: sequential functionality/programs

- > C-based [SpecC, SystemC, SystemVerilog]

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

20

### **Lecture 8: Outline**

- **✓** Introduction

- √ System design flow

- ESL design

- Modeling

- Synthesis

- Verification

- ESL landscape

- Summary and conclusions

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

21

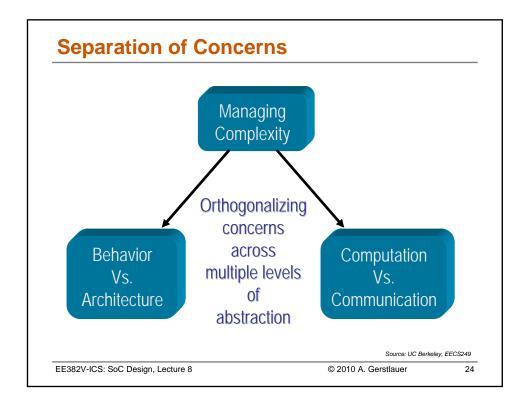

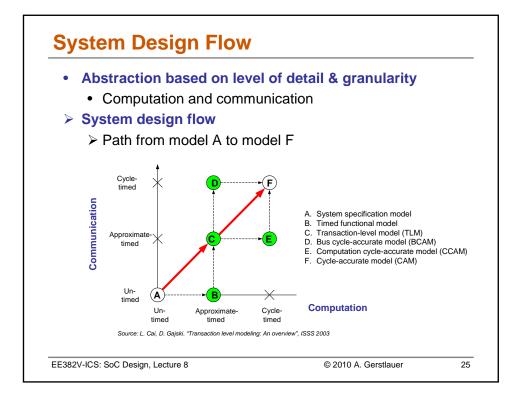

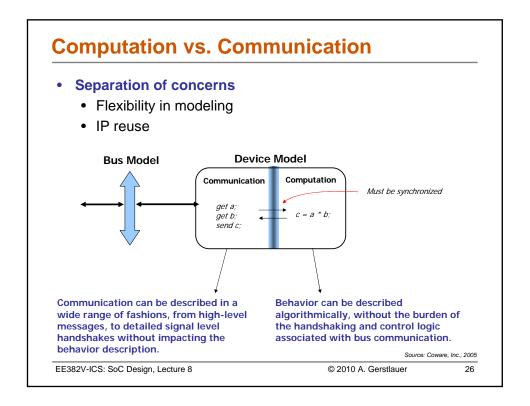

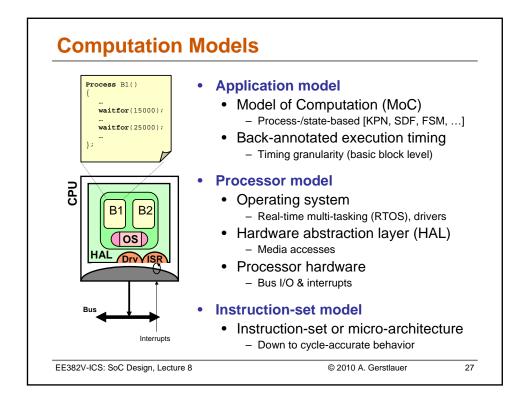

# **System Modeling**

- Design models as abstraction of a design instance

- · Representation for validation and analysis

- Specification for further implementation

- > Documentation & specification

- Systematic modeling flow and methodology

- · Set of models

- · Set of design steps

- > From specification to implementation

- Well-defined, rigorous system-level semantics

- · Unambiguous, explicit abstractions, models

- Objects and composition rules

- > Synthesis and verification

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

22

### **Modeling Guidelines**

- A model should capture exactly the aspects required by the system, and no more.

- There is not one model/algorithm/tool that fits all.

- Being formal is a prerequisite for algorithmic analysis.

- Formality means having a mathematical definition (semantics) for the properties of interest.

- Being compositional is a prerequisite for scalability.

- Compositionality is the ability of breaking a task about A||B into two subtasks about A and B, respectively.

Source: UC Berkeley, EECS249

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

23

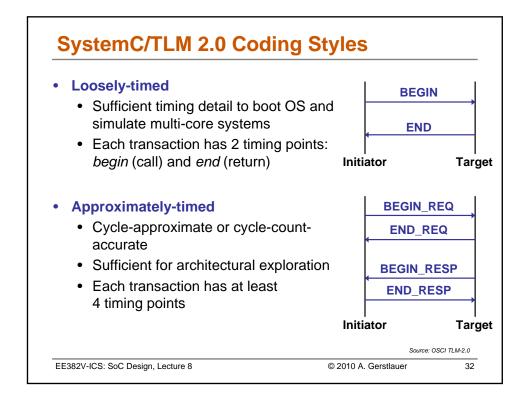

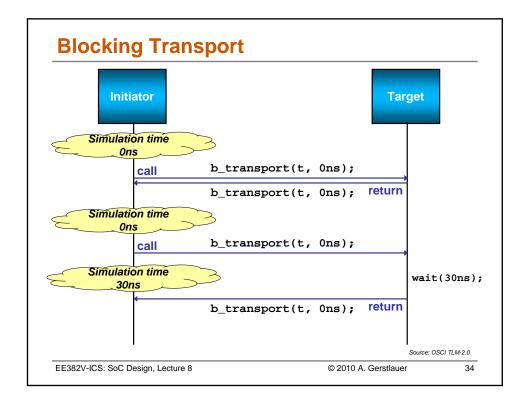

# **Blocking and Non-Blocking Transports**

- Blocking transport interface

- Typically used with loosely-timed coding style

- tlm\_blocking\_transport\_if

void b\_transport(TRANS&, sc\_time&);

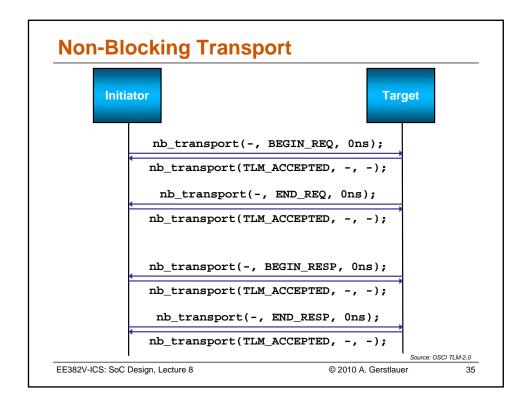

- Non-blocking transport interface

- Typically used with approximately-timed coding style

- Includes transaction phases

- tlm\_fw\_nonblocking\_transport\_if

tlm\_sync\_enum nb\_transport\_fw(TRANS&, PHASE&, sc\_time&);

- tlm\_bw\_nonblocking\_transport\_if tlm\_sync\_enum nb\_transport\_bw(TRANS&, PHASE&, sc\_time&);

Source: OSCI TLM-2.0

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

33

# **Lecture 8: Outline**

- **✓** Introduction

- ✓ System design methodology

- ESL design

- ✓ Modeling

- Synthesis

- Verification

- ESL landscape

- Summary and conclusions

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

39

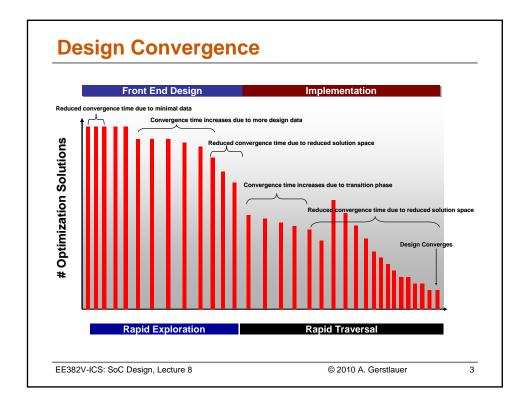

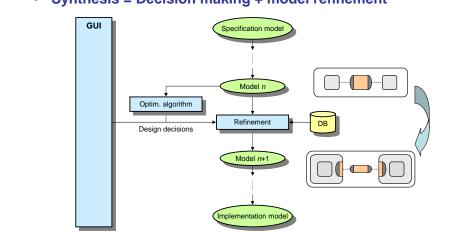

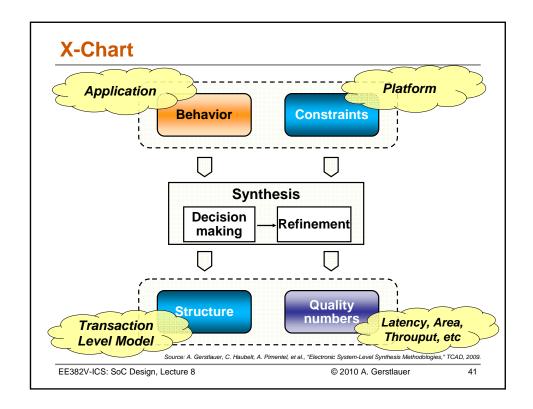

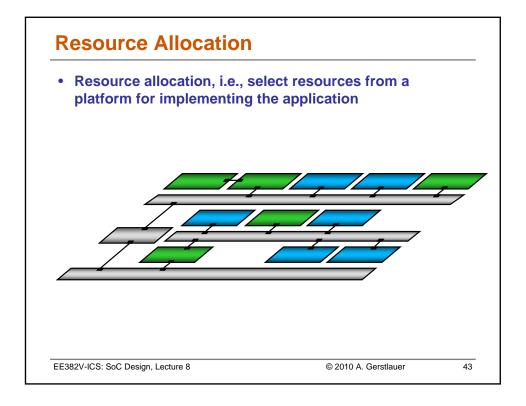

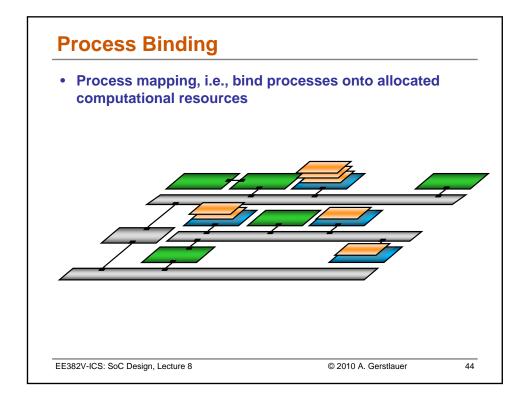

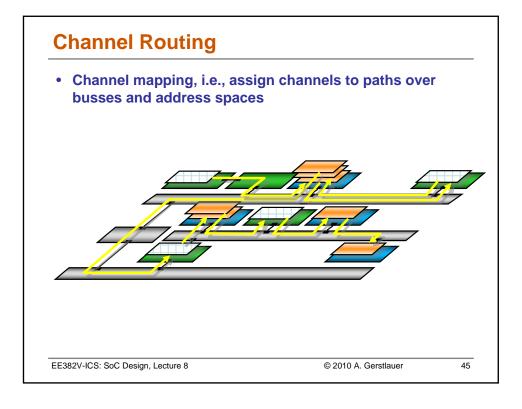

# • Synthesis = Decision m

• Synthesis = Decision making + model refinement

- > Successive, stepwise model refinement

- > Layers of implementation detail

EE382V-ICS: SoC Design, Lecture 8 © 2010 A. Gerstlauer

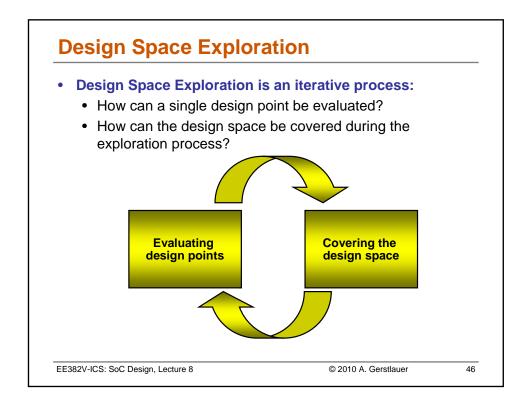

### **Optimization Approaches**

- Exact methods

- Enumeration, (Integer) Linear Programs

- Heuristics

- Constructive

- Random mapping, hierarchical clustering

- Iterative

- Random search, simulated annealing, min-cut (Kernighan-Lin)

- Set-based ("intelligent" randomized search)

- Evolutionary Algorithms (EA),

Particle Swarm Optimization (PSO),

Ant Colony Optimization (ACO)

- > Exact, constructive & iterative methods are prohibitive

- > Large design space, multiple objectives, dynamic behavior

- > Set-based approaches

- > Randomized, problem independent (black box), Pareto set

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

47

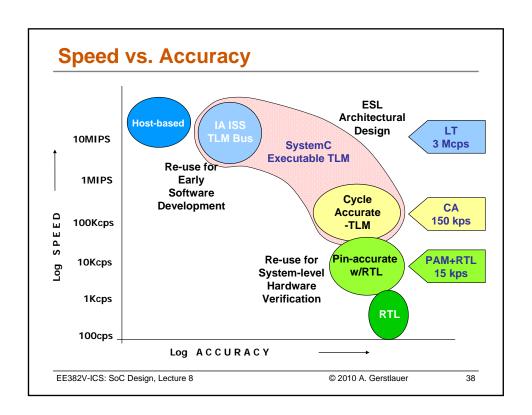

# **Evaluation Approaches**

- Dynamic simulation

- Profiling, ISS/RTL co-simulation

- Long simulation times, corner cases

- Static analysis

- Component-level estimation [Worst-Case Execution Time (WCET)]

- System-level cost functions, real-time calculus [Modular Performance Analysis (MPA)]

- Inaccurate bounds, manual interference (false paths)

- Combinations

- Host-compiled simulation

- Trace-driven simulation

- Tradeoff between accuracy and speed

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

48

### **Lecture 8: Outline**

- **✓** Introduction

- √ System design methodology

- ESL design

- √ Modeling

- √ Synthesis

- Verification

- ESL landscape

- Summary and conclusions

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

49

# **Design Verification Methods**

- Simulation based methods

- · Specify input test vector, output test vector pair

- Run simulation and compare output against expected output

- Formal Methods

- Check equivalence of design models or parts of models

- · Check specified properties on models

- Semi-formal Methods

- Specify inputs and outputs as symbolic expressions

- Check simulation output against expected expression

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

50

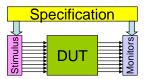

### **Simulation**

- · Create test vectors and simulate model

- Simulation, debugging and visualization tools [Synopsys VCS, Mentor ModelSim, Cadence NC-Sim]

- Inputs

- Specification

- Used to create interesting stimuli and monitors

- Model of DUT

- Typically written in HDL or C or both

- Output

- · Failed test vectors

- Pointed out in different design representations by debugging tools

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

51

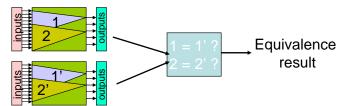

# **Equivalence Checking**

LEC uses boolean algebra to check for logic equivalence

SEC uses FSMs to check for sequential equivalence

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

52

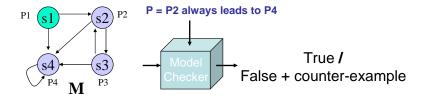

# **Model Checking**

- Model M satisfies property P? [Clarke, Emerson '81]

- Inputs

- State transition system representation of M

- Temporal property P as formula of state properties

- Output

- True (property holds)

- False + counter-example (property does not hold)

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

53

# **Lecture 8: Outline**

- ✓ Introduction

- √ System design methodology

- √ ESL design

- ESL landscape

- Commercial tools

- Academic tools

- Summary and conclusions

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

54

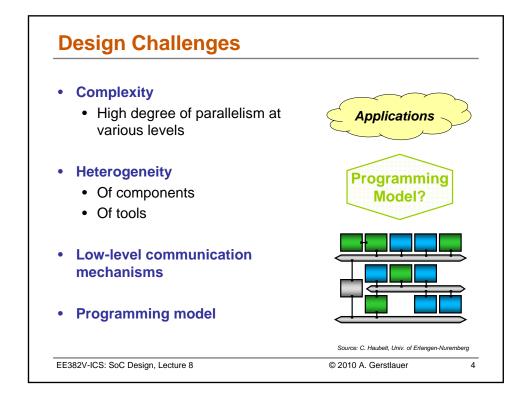

### **ESL Tools**

- Electronic System-Level (ESL) terminology

- Often single hardware unit only

- C-to-RTL high-level synthesis (HLS) [Mentor Catapult, Forte Cynthesizer]

- System-level across hardware and software boundaries

- System-level frontend

- Hardware and software synthesis backend

- > Commercial tools for modeling and simulation

- Algorithmic modeling (MoC) [UML, Matlab/Simulink, Labview]

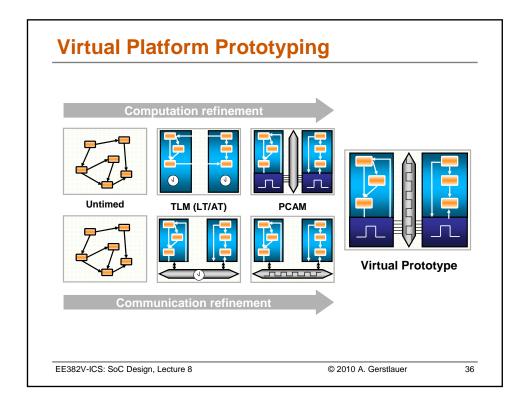

- Virtual system prototyping (TLM) [Coware, VaST, Virtutech]

- > Only horizontal integration across models / components

- > Academic tools for synthesis and verification

- MPSoC synthesis [SCE, Metropolis, SCD, PeaCE, Deadalus]

- Vertical integration for path to implementation

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

56

# **Academic MPSoC Design Tools**

| Approach         | DSE | Comp. decision | Comm. decision | Comp. refine | Comm. refine |

|------------------|-----|----------------|----------------|--------------|--------------|

| Daedalus         | •   | •              | 0              | •            | 0            |

| Koski            | •   | •              | 0              | •            | 0            |

| Metropolis       |     | 0              |                | 0            |              |

| PeaCE/HoPES      | 0   | 0              |                | •            | 0            |

| SCE              |     |                |                | •            | •            |

| SystemCoDesigner | •   | •              | •              | 0            |              |

Source: A. Gerstlauer, C. Haubelt, A. Pimentel, et al., "Electronic System-Level Synthesis Methodologies," TCAD, 2009.

EE382V-ICS: SoC Design, Lecture 8

© 2010 A. Gerstlauer

57