# New Directions in Manufacturing Test

Jacob A. Abraham

Computer Engineering Research Center

The University of Texas at Austin

Shanghai Jiao Tong University

July 19, 2005

July 19, 2005

J. A. Abraham

### Research Areas

- Manufacturing test

- Dealing with faults in sub 100 nm circuits

- -System-on-a-chip test issues

- Design verification

- Formal approaches for property checking

- Abstractions to deal with complexity

- Fault tolerance

- Dealing with soft errors

- Application-level techniques

July 19, 2005

J. A. Abraham

2

## **Outline**

- Manufacturing Test

- Trends in Silicon defects

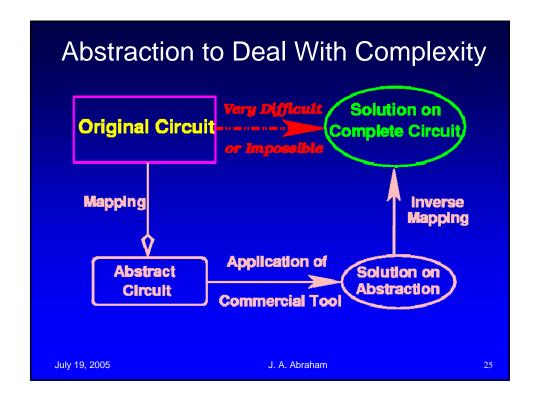

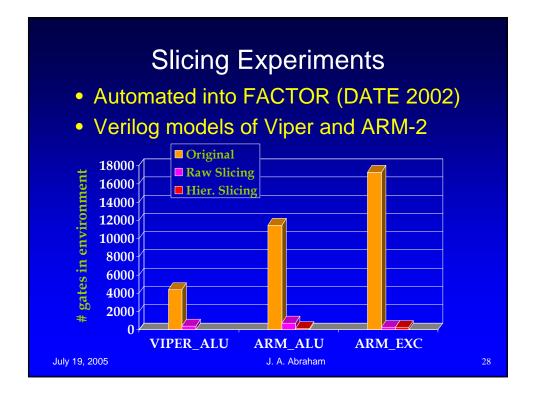

- Hierarchy and abstractions to deal with test generation complexity

- Native-Mode Built-In Self-Test

- Application to testing processors

- Test of A/D and D/A converters

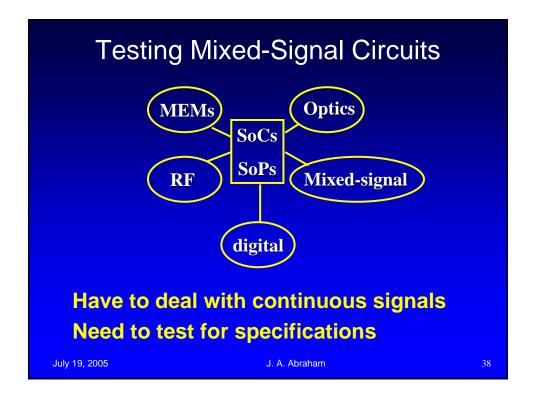

- Testing of mixed-signal circuits

- Future Directions

July 19, 2005 J. A. Abraham

**Dealing with Faults** Physical Logical Manufacturing Design Operation Operation Wearout Processing Software "bug" Operator mistake Environmental Hardware disturbance design fault Marginal Manufacturing faults, field failures: testing, design for testability Design faults: simulation and emulation, formal techniques Operational faults: concurrent error detection and fault tolerance July 19, 2005

# Manufacturing Test

- A speck of dust on a wafer is sufficient to kill chip

- Yield of any chip is < 100%</li>

- Must test chips after manufacturing before delivery to customers to only ship good parts

- Manufacturing testers are very expensive

- Minimize time on tester

- Careful selection of test vectors

tester feet head

July 19, 2005

J. A. Abraham

**Test Generation** Apply test Observe sequences to output pins input pins Detect defects Defect Level Test quality A test for a defect will produce an output response which is different from the output when there is no defect Test quality is high if the set of tests will detect a very high fraction of defects Defect level is the percentage of bad parts shipped to customers Yield is the percentage of defect-free chips manufactured July 19, 2005 J. A. Abraham

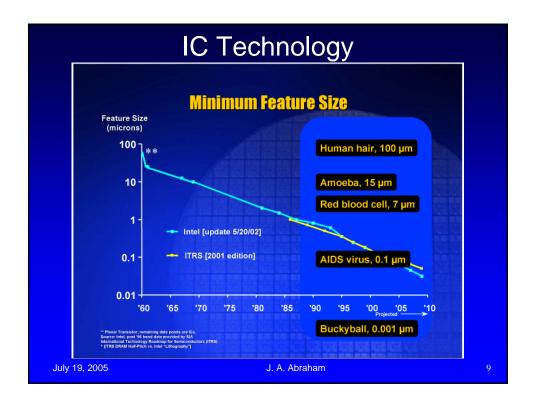

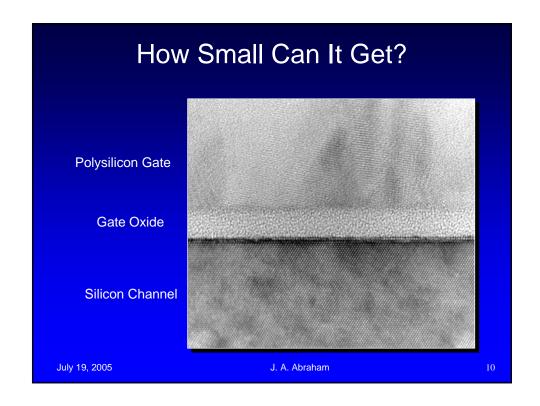

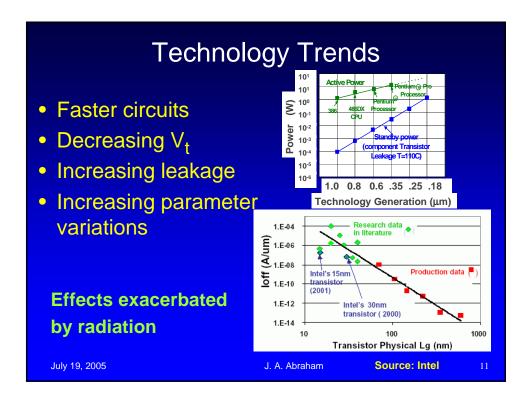

## What About the Future

- Are existing test solutions sufficient to deal with the defects which may exist in emerging technologies?

- Look at some of the technology trends

- Examine industry experience in new types of defects and test problems

July 19, 2005 J. A. Abraham 8

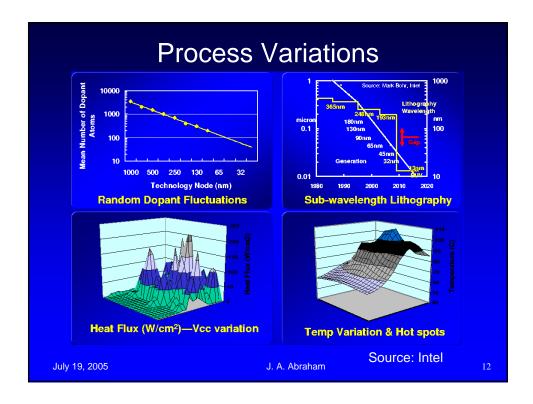

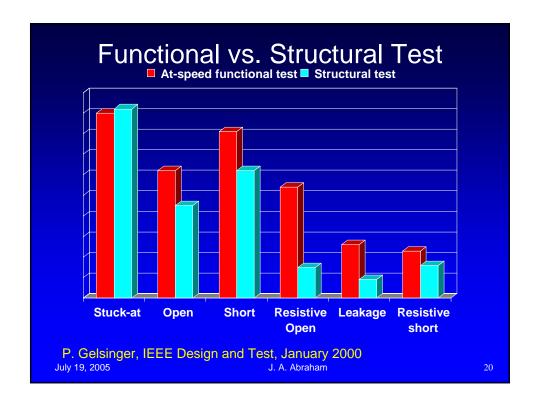

## Defects in Emerging Technologies

- Resistive opens comprise the bulk of test escapes in one production line

- Likely in copper interconnect cause delay faults

- Delay faults identified as the cause of most test escapes on another line

- Speed differences of up to a factor of 1.5 can exist between fast and slow devices - problems with "speed binning"

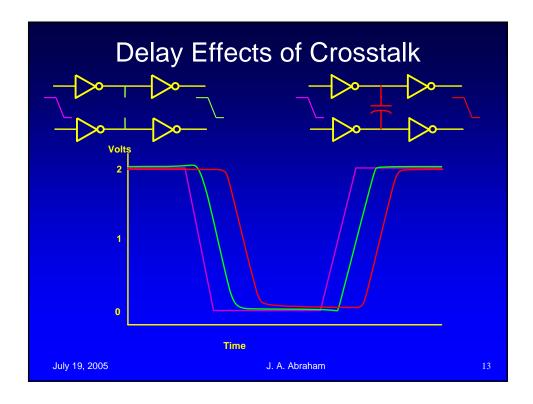

- Increasing possibility of shorts and crosstalk

- Defects appearing as delays or soft failures

July 19, 2005 J. A. Abraham 1

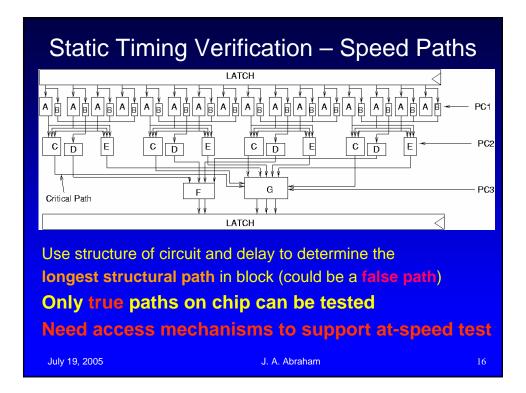

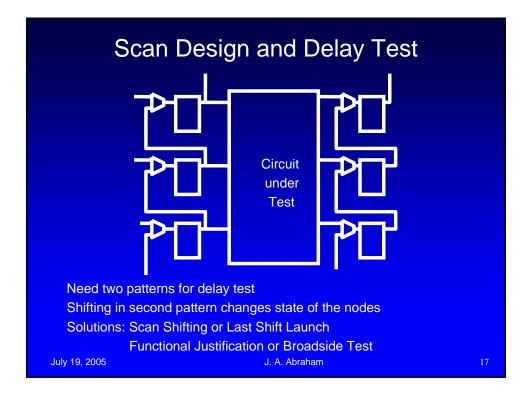

## Impact on Test

- Existing Design for Test (DFT) structures are geared to "stuck" faults

- Not easy to apply two-pattern tests necessary to check for path delays

- Performance optimizations result in a large number of paths close to the critical delay values

- Designs using statistical timing models would require the circuits to be also tested for paths close to the critical delay

July 19, 2005 J. A. Abraham 1:

# Dealing With the Entire Design

- Interest in chip-level (functional) tests

- Delay tests generated at the block level may be too conservative

- "Long" paths at the block level may be false at the next level

- Problem of dealing with the entire design:

- Design with around 300 memory elements has more states than the number of protons in the universe!

July 19, 2005 J. A. Abraham 2

## Dealing With the Entire Design

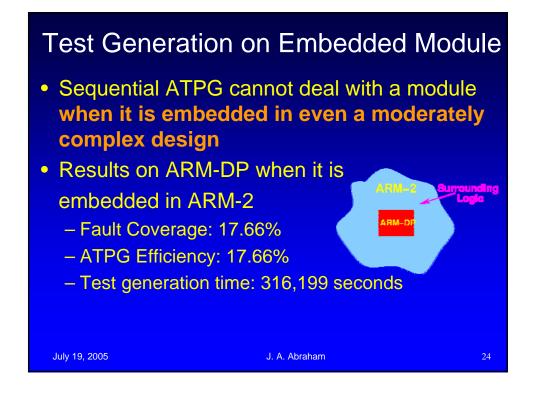

- Experiments on benchmark processors (target embedded module in processor)

- 1. Tests for faults in module under test (MUT) by itself

2. Tests for MUT faults when embedded in processor

|               | Comb. Gates | Seq. Elems.   | Pls | POs | Faults |

|---------------|-------------|---------------|-----|-----|--------|

| ARM-2         | 16029       | 1270          | 63  | 67  | 99198  |

| ARM-DP        | 8893        | 295           | 199 | 161 | 51824  |

| July 19, 2005 |             | J. A. Abraham |     |     | 22     |

# Test Generation on Module Sequential ATPG can easily deal with a module Example: ARM-DP by itself Results using commercial ATPG tool (on HPUX-715, 125 MHz processor) Fault Coverage: 99.70% ATPG Efficiency: 99.93% Test generation time: 33.1 seconds Test length: 822 cycles

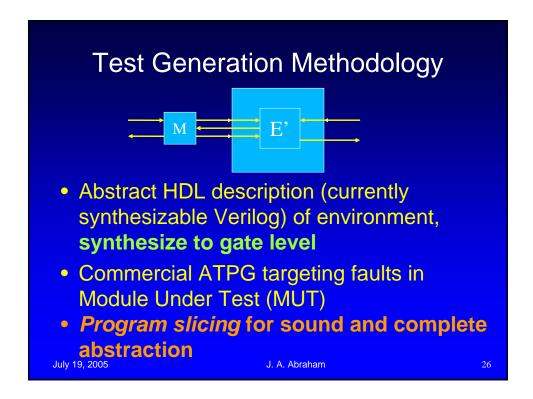

# **Key Theory**

- Lemma 1: Union of constraint slices provides abstracted environment

- Lemma 2: Process trace for signals defined in a MUT preserved

- Theorem 1: Valid set of patterns for the MUT using constraint slices

- Theorem 2: Hierarchical composition yields the desired constraint slice

July 19, 2005 J. A. Abraham 2

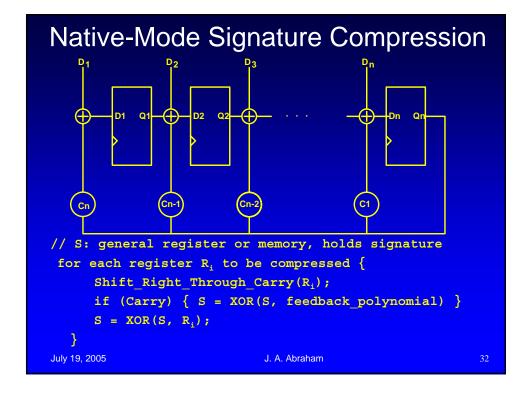

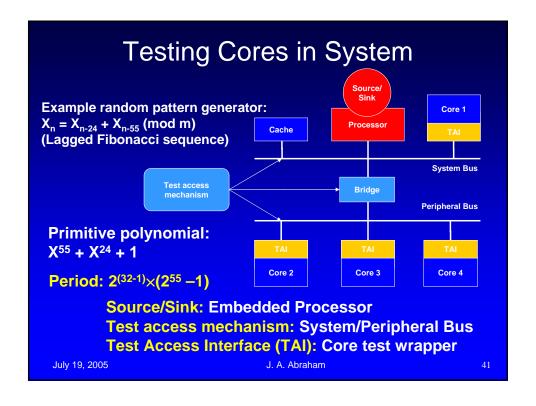

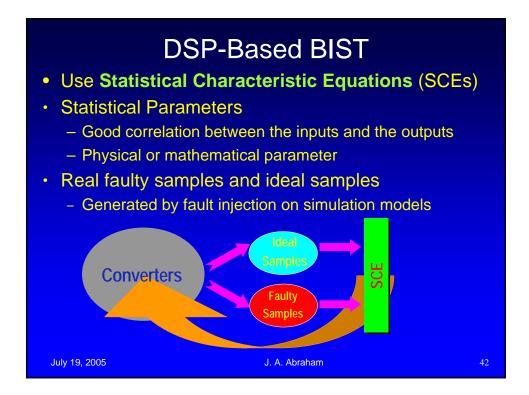

## Native-Mode Built-In Self Test

- Functional capabilities of processors can be used to replace BIST hardware – (Shen and Abraham, ITC 1998)

- Application to self-test of processors at Intel FRITS method applied to Pentium 4, Itanium (ITC 2002)

- Embedded processor can be used to test other modules in a System-on-a-Chip (research at Texas, Santa Barbara, San Diego)

- Extend approach to test embedded analog and mixed-signal modules

July 19, 2005 J. A. Abraham 3

## Intel Functional BIST

- Functional tests have good "collateral coverage" for detecting unmodeled defects

- Technique of Functional Random Instruction Testing at Speed (FRITS) applied to Itanium processor family and Pentium 4 line

- Parvathala et al., Int'l Test Conference, 2002

- Tests (kernels) are instruction sequences

- Kernels loaded into cache and executed in real time during test application

- They generate and execute pseudo-random or directed sequences of machine code

July 19, 2005 J. A. Abraham 3

## **FRITS Results**

- On Pentium 4, full chip-level coverage of single-stuck faults was ≈ 70% with FRITS

- Added 5% unique coverage to manually generated tests

- Helped reduce test "holes"

- Screen 10%–15% of chips which passed wafer sort/package tests by failed system tests

- Enables low cost testers

- 40% increase in defect screening on structural tester

- Kernels execute 20 loops in ≈ 8 mSecs

July 19, 2005

J. A. Abraham

4

# Automatic Mapping of Module Tests to Instruction Sequences

- Functional and directed random tests provide good fault coverage (95% – 96%) in highperformance microprocessors

- Need to develop tests for the remaining, hardto-detect faults

- Able to generate tests for these faults at the module level

- Developing new techniques for mapping module-level tests to instruction sequences

July 19, 2005 J. A. Abraham 3

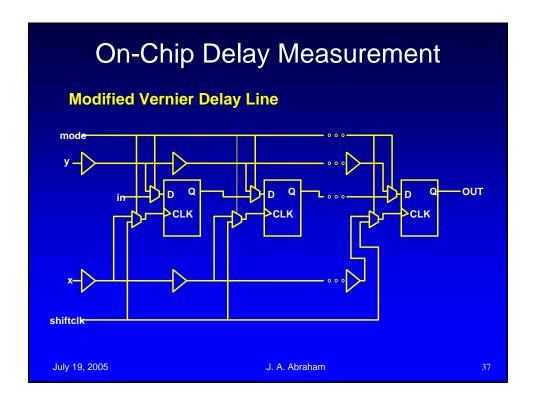

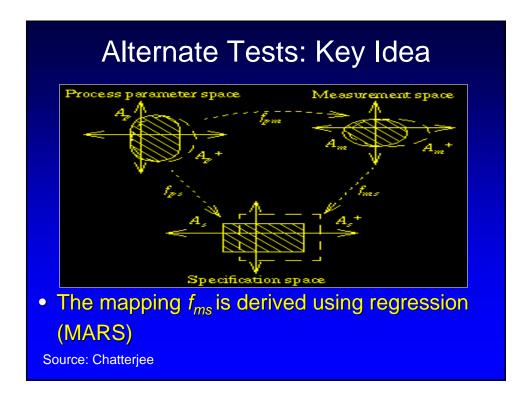

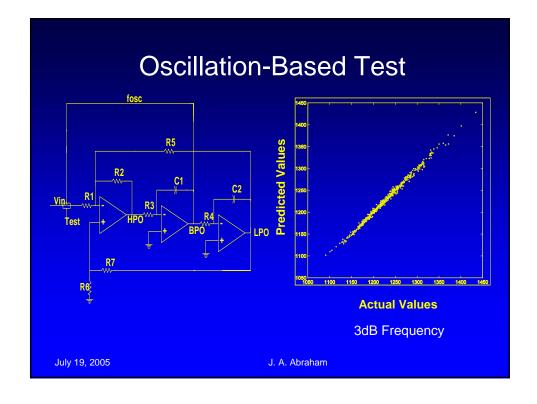

# Change in Test Requirements

- Analog and mixed-signal circuits need to be tested for conformance with specifications

- Delay tests (speed binning) for digital circuits are also specification-based tests

- Designing for process variations will require sophisticated tests to screen for parts falling outside the acceptance limits

July 19, 2005 J. A. Abraham 36

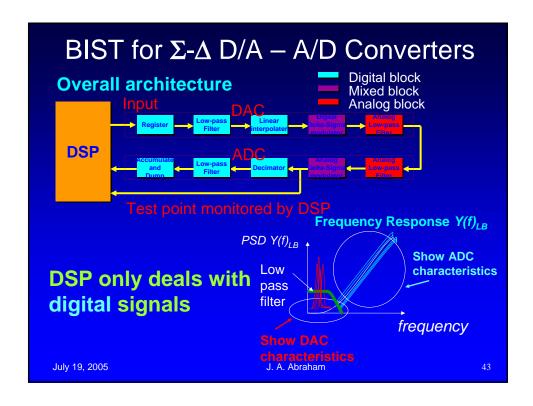

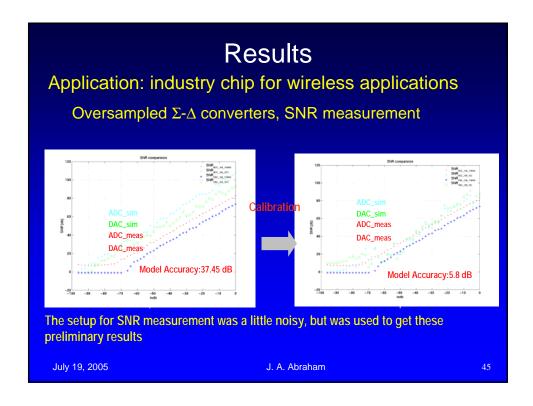

# Implementation • Applied BIST technique to industry chip for wireless applications - Oversampling Δ-Σ converters - Analog loop-back - SNR measurement

# Ongoing Work in Test

- New approaches for dealing with process variations and sub-100 nm defects

- Testability features for improved DSP-based BIST

- Applications to high-frequency designs (PLLs, RF, etc)

- Algorithms for mapping module-level tests to instructions

- Improved abstraction techniques to speed up test for complex designs

July 19, 2005 J. A. Abraham 46