Jacob Abraham

Department of Electrical and Computer Engineering The University of Texas at Austin

> Verification of Digital Systems Spring 2020

> > February 13, 2020

re 8. Verifying Analog/Mixed-Signal Sys

Jacob Abraham, February 13, 2020 1 / 27

Jacob Abraham, February 13, 2020 1 / 27

### Acknowledgements

ECE Department, University of Texas at Au

- Graduate students: A. Balivada, N. Nagi, Y. Hoskote

- U. C. Berkeley: K. Aadithya, R. Brayton, A. Mishchenko, P. Nuzzo, S. Ray, J. Roychowdhury, B. Sterin

- Univ. of Illinois: S. Ahmadyan; S. Vasudevan

ECE Department, University of Texas at Austin Lecture 8. Verifying Analog/Mixe

• Georgia Tech: A. Chatterjee, S. Deyati, B. Muldrey

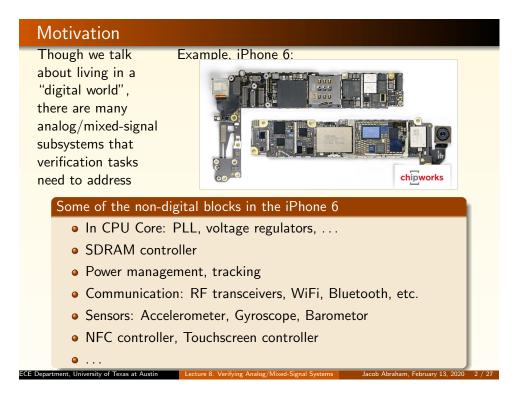

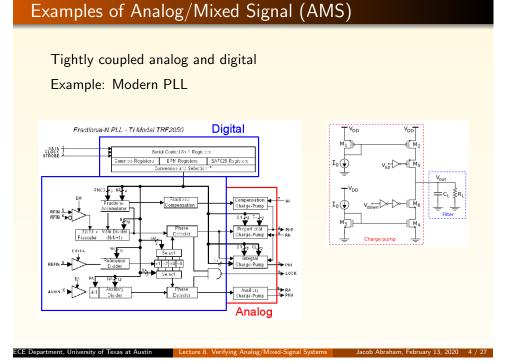

# What is Analog/Mixed-Signal?

ECE Department, University of Texas at Austin

<text><list-item><list-item><list-item>Circuits dealing with non-binary, or a mixture of binary and<br/>non-binary values• interconnects (on chip, I/O channels, power supplies, ...)• op-amps, comparators, mixers, charge pumps, ....• digital circuits driven at high speeds rightary analog effects• when timing delays are important<math>fightary effect of the constraint of the cons

Jacob Abraham, February 13, 2020 3 / 27

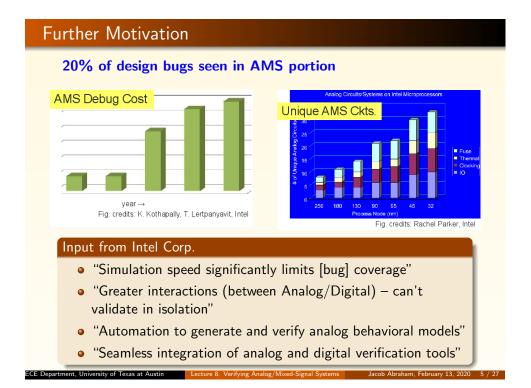

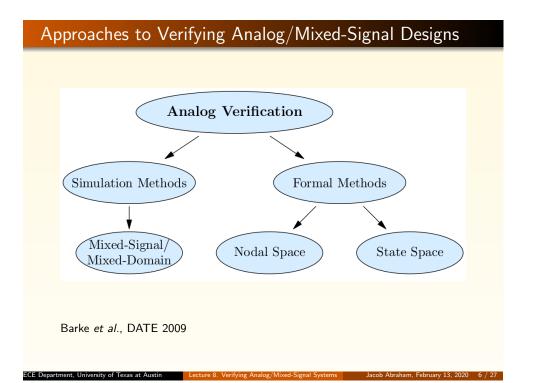

## Correctness in Analog Verification

#### Digital designs

- Results are direct for logic output values should be correct during every clock cycle

- Timing or power-related bugs also result in either the correct or incorrect logic values in storage elements

### Analog subsystems

ECE Department, University of Texas at Austin

- Analog value at some output may be different from expected, but it is not so simple to determine whether it is correct

- Analog subsystems must meet specifications

For example, signal to noise ratio, linearity, etc.

- This problem has not been solved in research to date in analog verification

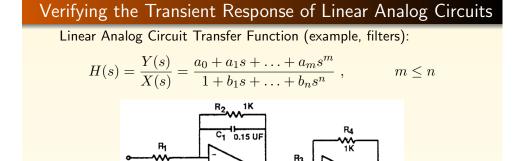

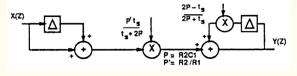

1/s

•1/R Ç

-R4/R3

X 1(s)

Y(s)

Jacob Abraham, February 13, 2020 10 / 27

Jacob Abraham, February 13, 2020 11 / 27

Low pass filter and its signal flow graph Balivada, VTS 1995

-1/R-C1

U(s)

Verification Process

ECE Department, University of Texas at Austin

ECE Department, University of Texas at Au

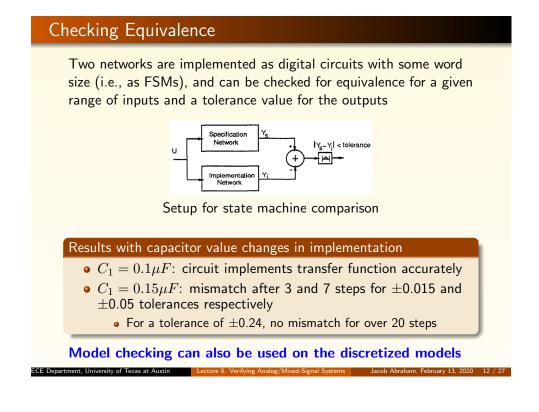

Both specification and implementation are discretized using a bilinear transformation

Discrete realization of transfer function (specification)

Discrete realization of filter implementation

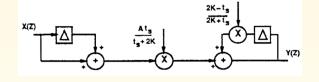

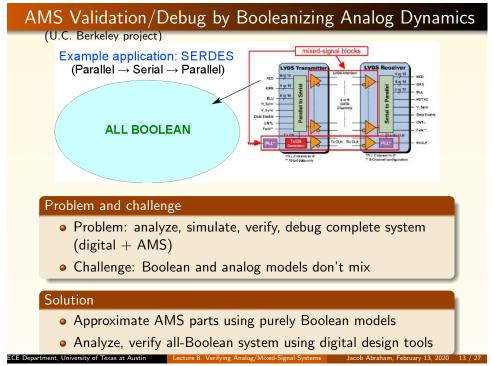

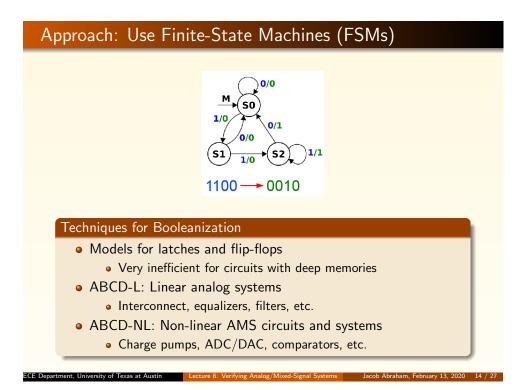

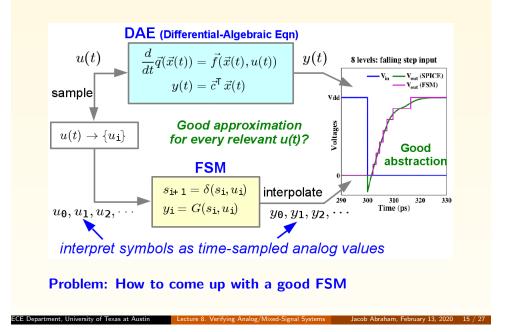

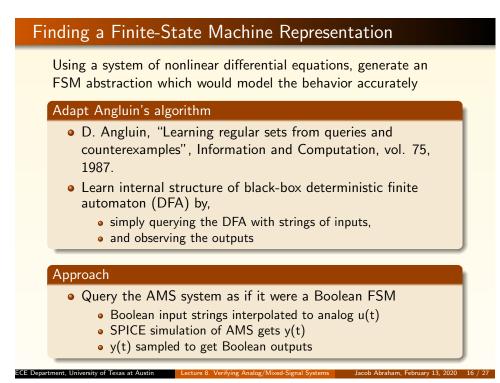

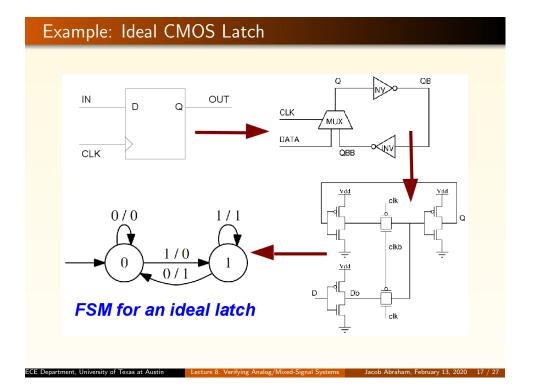

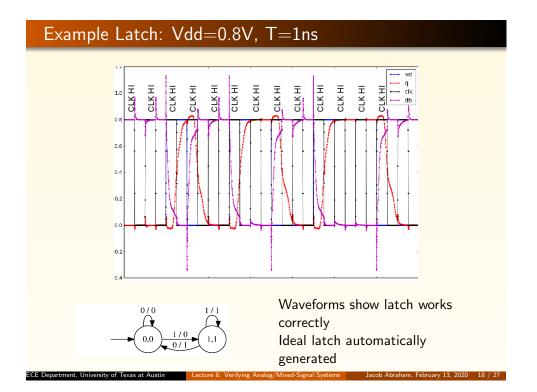

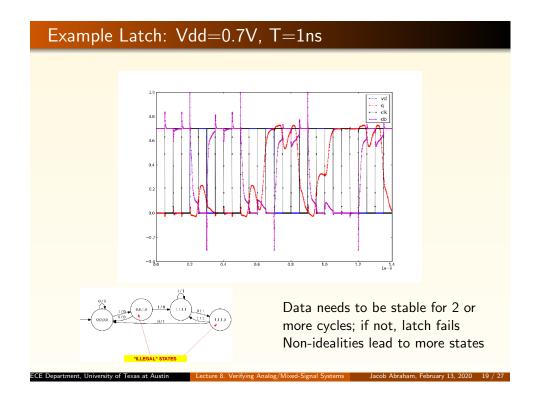

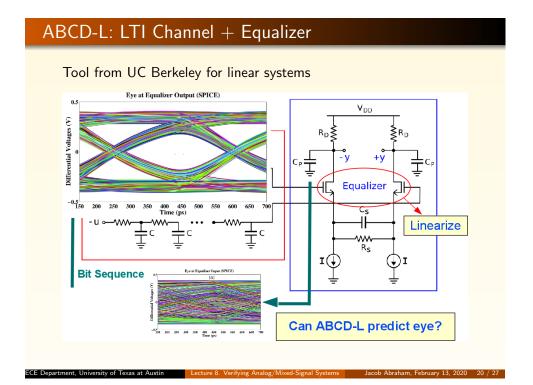

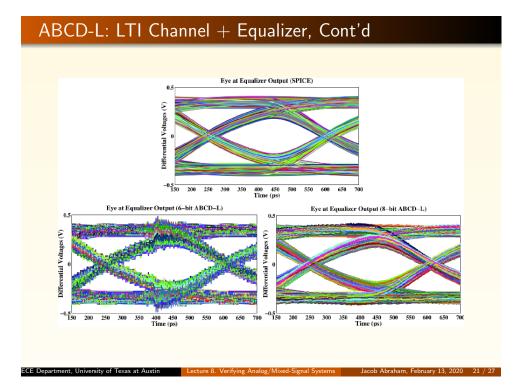

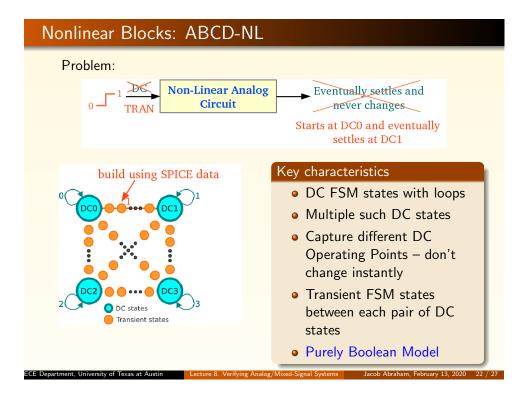

### Equivalent FSMs for AMS systems

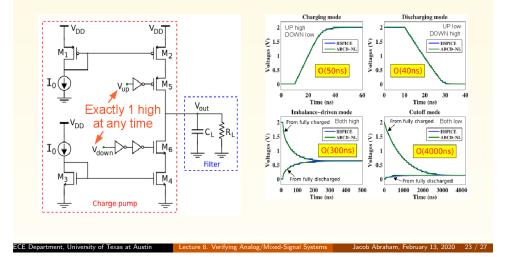

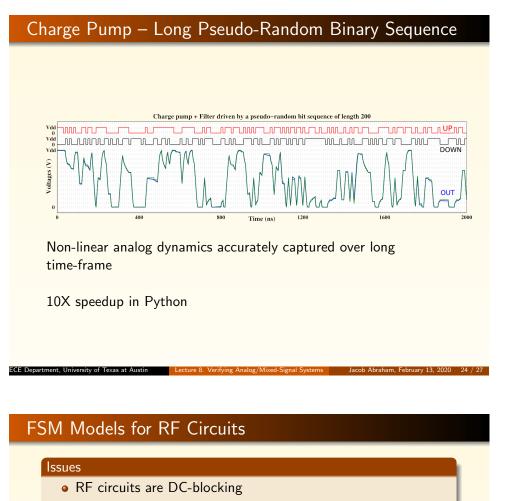

# Example: Charge Pump + Filter

Discretize Vup, Vdown using 1 bit each, Vout using 5 bits Booleanize using ABCD, Simulate Boolean model

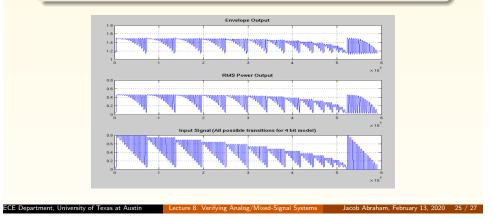

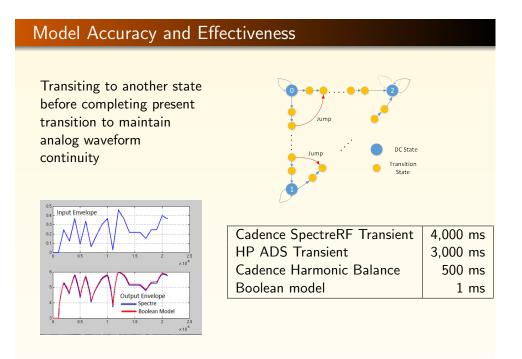

- Need to model carrier envelopes

- Memory effects in RF circuits must be incorporated

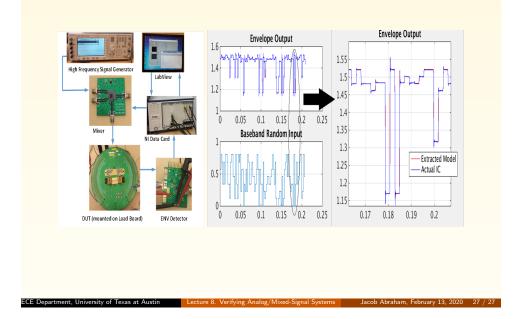

- Direct model extraction from hardware?

### Model Extraction from Hardware

ECE Department, University of Texas at A

Jacob Abraham, February 13, 2020 26 / 27