### Automatic Test Pattern Generation (ATPG)

• Map defects to (higher level) faults, and develop fault models (example logic-level "stuck-at" faults, or "path delay" faults)

#### Steps in Test Generation

ECE Department, University of Texas at Austin

- Activate fault (produce error at fault site)

- "Sensitize" path from fault to output (propagate error to output)

- "Justify" internal signals to primary inputs

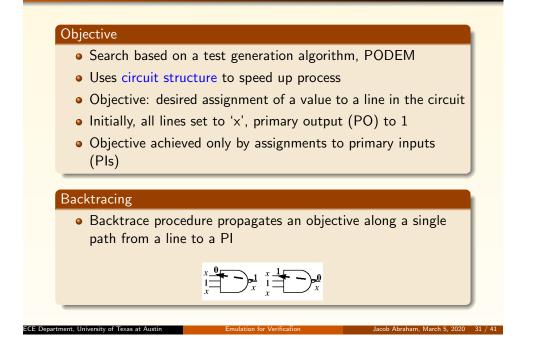

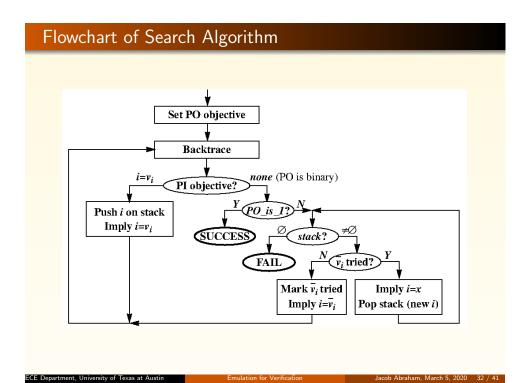

- Choices may exist during sensitization and justification: if conflicts arise, need to **backtrack**

- If no test exists, fault is **redundant**

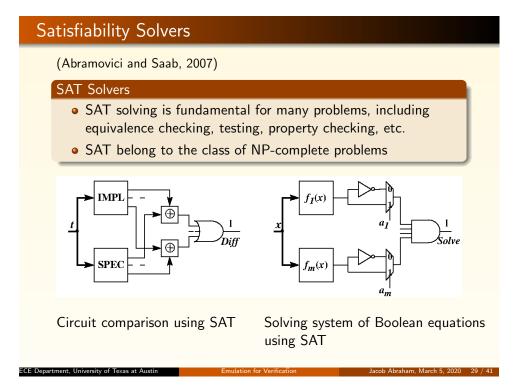

SAT solvers have been applied to generating tests for combinational blocks

Propagation of the error is not necessary for verification (any node can be monitored in simulation)

## **Observability and Controllability**

ECE Department, University of Texas at Austin

- **Controllability**: ease of forcing a node to 0 or 1 by driving input pins of the chip

- Combinational logic is usually easier to observe and control

Still, NP-complete problem

- Finite state machines can be very difficult, requiring many cycles to enter desired state

- Especially if state transition diagram is not known to the test engineer, or is too large

Jacob Abraham, March 5, 2020 5 / 41

- Verifying the high-level design: no guarantee that refinements will not introduce errors

- Abstractions to reduce complexity: may mask bugs

- Verify design at the lowest level possible: example, ATPG level

Jacob Abraham, March 5, 2020 7 / 41

• Can then deal with tri-states, multiple clocks, etc.

ECE Department, University of Texas at Austin

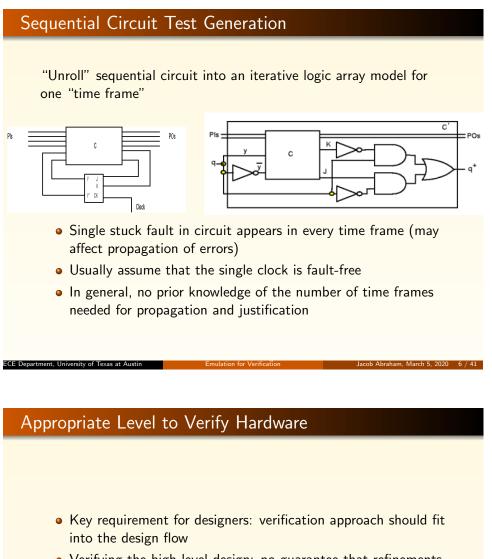

## Test Generation Algorithms for Verification

#### Testing and verification constraints

- Limited observability inside a chip during manufacturing test

- Pre-silicon verification can take advantage of a high degree of observability (not necessary to propagate errors to chip outputs or scan flip-flops during verification)

#### Testing versus verification

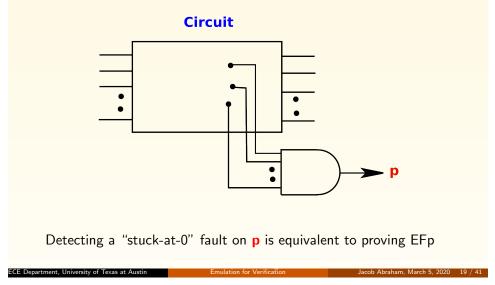

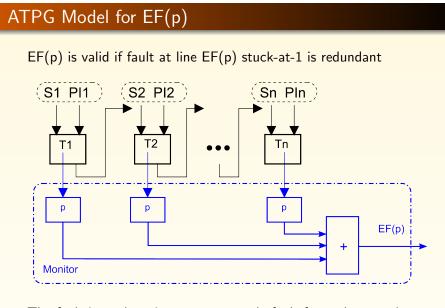

- Activating a test for a fault on a node (say x stuck-at-0) means that a test sequence should result in a 1 on x

- This sequence is a witness to the property *Fx*

- To find a sequence which will prove that a state  $s_i$  is eventually reached (i.e.,  $Fs_i$ ), we test for a stuck-at-0 on an AND gate with the appropriate state variable inputs

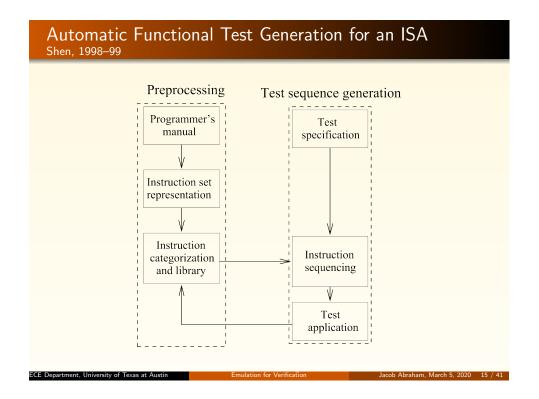

### **Functional Test Generation**

ECE Department, University of Texas at

ECE Department, University of Texas at Austin

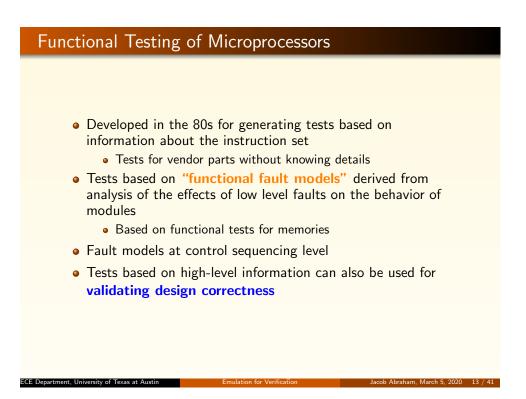

- Useful for verification and speed tests

- Requirement for successful functional test:

- Check for unintended functions in addition to the correct one

- Physical failures can cause spurious operations while performing the desired function correctly

- Ad-hoc functional tests typically do not check for such behavior

- Applied to generating tests for memories, microprocessors

March 5, 2020 8 / 41

Jacob Abraham, March 5, 2020 9 / 41

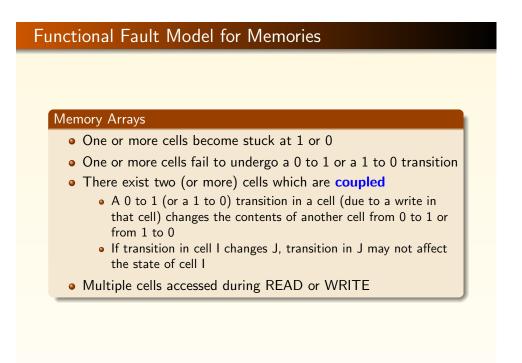

## Memory Fault Model, Cont'd

#### Decoders

ECE Department, University of Texas at Austin

ECE Department, University of Texas at Au

- The decoder will not access the addressed cell, and in addition may access non-addressed cells

- The decoder will access multiple cells, including the addressed cell

- Assumption that the combinational logic of the decoder will not be transformed into sequential logic

- Decoder faults look like memory cell array faults

- Fault model can be validated by simulating effects of faults at the transistor level

bb Abraham, March 5, 2020 10 / 41

Jacob Abraham, March 5, 2020 11 / 41

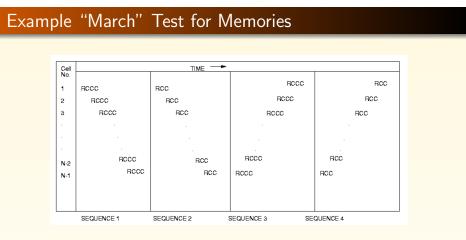

- R: Read cell and verify

- C: Complement cell

ECE Department, University of Texas at

Complexity of Test: 14N (N cells)

This test will verify that writing any location will not disturb any other location

March 5, 2020 12 / 41

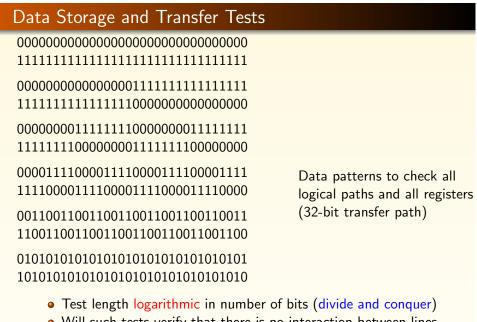

Will such tests verify that there is no interaction between lines in a data path?

Abraham, March 5, 2020 14 / 41

ECE Department, University of Texas at Austin

#### Improving Tests Through Genetic Learning Saab, 1994

#### Approach

- Partition circuit

- Depth first search

- Run tests

- Pick regions with very low activity

- Create activity

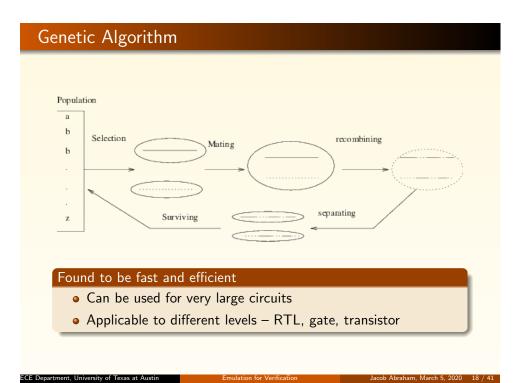

#### Approach – Genetic Algorithm

- Reproduction (copying potentially useful candidate vectors and sequences)

- Mutation (flipping bits in a vector).

- Splicing (producing a new vector using substrings from two other vectors)

- Splicing (producing a new sequence using subsequence from two sequences)

ECE Department, University of Texas at Austin

ECE Department, University of Texas at Austin

ECE Department, University of Texas at Austin

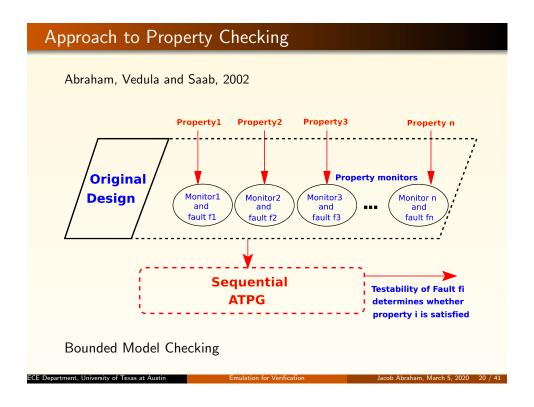

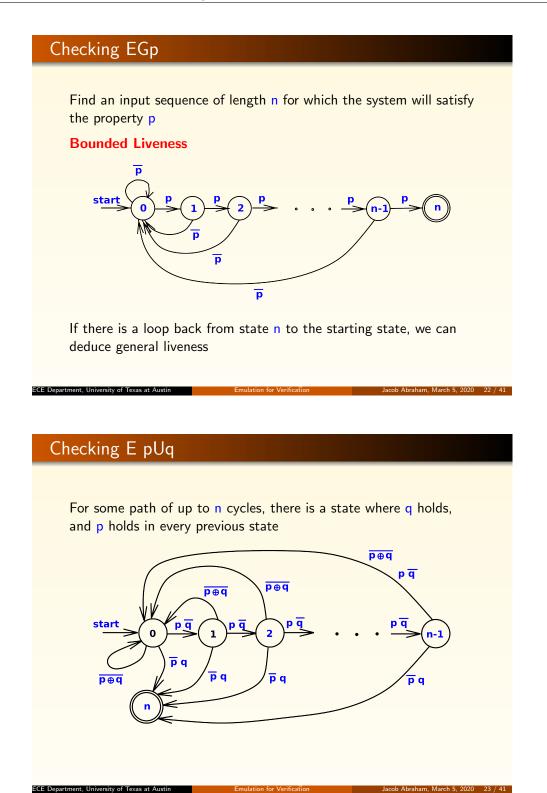

# Verifying Properties Using Sequential ATPG

Prior work in checking *safety properties*; required custom ATPG or modifications to existing ATPG tools

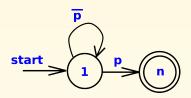

### Monitor State Machine for EXp

The monitor machine moves to an accepting state if p is true

This is combined with the design, and the ATPG tool asked to find an input sequence to reach the state "n"

The result would be one of

ECE Department, University of Texas at Austin

- ATPG finds an input sequence EXp is proved, and the sequence would be a *witness* to the property

- ATPG returns the result that a "test" is not possible EXp is false

acob Abraham, March 5, 2020 21 / 41

• ATPG *aborts* – the design was too complex to be analyzed

## Results on ISCAS89 Benchmark Circuits

- ATPG: commercial tool (Mentor *flextest*)

- BMC: Cadence research tool (SMV) with zchaff SAT solver

- s838.1 36 inputs, 1 output, 446 gates, 32 flops

- Property: output is 1 for a sequence of n clocks (n=5, 10, 15)

- Result: true for n = 5, 10 (false for n = 15)

CPU seconds to check property (SUN UltraSparc, dual 450MHz, 1 GByte)

| ſ | Bou  | nd: 5 | Bour | nd: 10 | Bour | nd: 15 |

|---|------|-------|------|--------|------|--------|

|   | BMC  | ATPG  | BMC  | ATPG   | BMC  | ATPG   |

|   | 1.57 | 0.1   | 2.0  | 0.2    | 2.88 | 0.3    |

### **Checking Properties of GL85**

ECE Department, University of Texas at /

ECE Department, University of Texas at Austin

- Clone of Intel 8085 designed by Alex Miczo (not pin-compatible)

- 10,084 gates, 238 flip-flops

- Properties (dealing with system reset)

- ROIA: Reset on Interrupt Acknowledge

- RORW: Reset on Read-Write

- ROTF: Reset on Tstates Flow

- ROIE: Reset on Interrupt Enable

- TOPE: Trap on Priority Encoding

- RWIO: Reset While Interrupt On

Example:  $G((TRAP = 1 \& TRAPFF = 1) \implies (P5/PIE(2:0) = 000B))$

b Abraham, March 5, 2020 24 / 41

Jacob Abraham, March 5, 2020 25 / 41

| CPU secon<br>Bound = 2 |       | N UltraS | parc, dual             | 450MH | z, 1 GByte                   |

|------------------------|-------|----------|------------------------|-------|------------------------------|

| Property               | BMC   | ATPG     |                        |       |                              |

| RORW                   | 7209  | 12.1     |                        |       |                              |

| ROTF                   | 4373  | 12.4     |                        |       |                              |

| ROIA                   | 6589  | 12.8     |                        |       |                              |

| ROIE                   | 7072  | 13.8     |                        |       |                              |

| TOPE                   | 10156 | 13.2     |                        |       |                              |

| RWIO                   | 6669  | 12.3     |                        |       |                              |

| ent, University of Tex |       |          | ulation for Verificati |       | Jacob Abraham, March 5, 2020 |

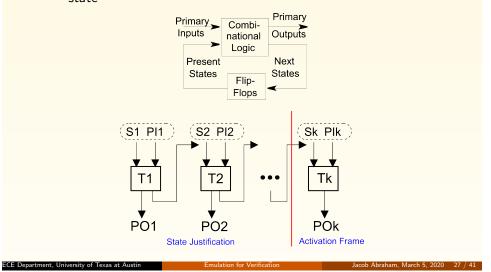

- ATPG activates the monitor faults in the last time frame

- Justify the activation state from unknown on known initial state

The fault is at the primary output; only fault-free values need to be justified

ECE Department, University of Texas at A

b Abraham, March 5, 2020 28 / 41

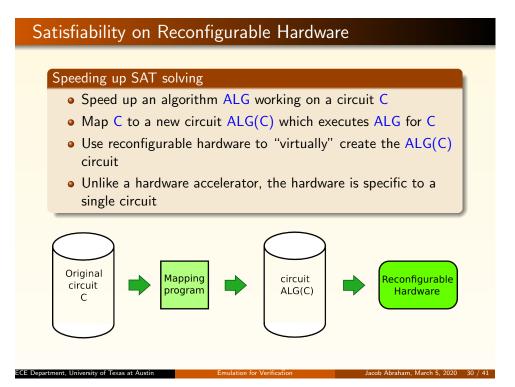

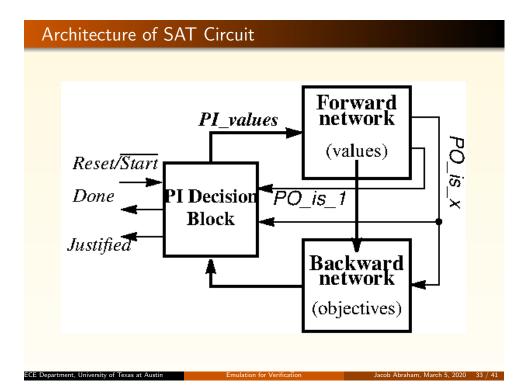

## Circuit for SAT search

| Results |       |         |        |       |    |           |         |         |  |  |  |

|---------|-------|---------|--------|-------|----|-----------|---------|---------|--|--|--|

|         |       |         |        |       |    |           |         |         |  |  |  |

| Circuit | Gates | Pls/POs | SAT    | Size  | SA | SAT       | CPU     | Speedup |  |  |  |

|         |       |         | Gates  | Incr. | Τ? | Clocks    | (sec)   |         |  |  |  |

| C432A   | 160   | 36/7    | 2,285  | 14.3  | Υ  | 5         | 0.1     | 20,000  |  |  |  |

| C499A   | 202   | 41/32   | 3,003  | 14.9  | Υ  | 49        | 0.1     | 2,041   |  |  |  |

| C880A   | 383   | 60/26   | 4,137  | 10.8  | Ν  | 21        | 0.2     | 9,524   |  |  |  |

| C1355A  | 546   | 41/32   | 5,231  | 9.6   | Υ  | 476,676   | 226.0   | 474     |  |  |  |

| C1908A  | 880   | 33/25   | 6,706  | 7.6   | Υ  | 5,021     | 2.0     | 398     |  |  |  |

| C2670A  | 1,193 | 233/140 | 13,180 | 11.0  | Ν  | 180,606   | 43.0    | 238     |  |  |  |

| C3540A  | 1,669 | 50/22   | 12,365 | 7.4   | Ν  | 132,204   | 188.9   | 1,429   |  |  |  |

| C5315A  | 2,307 | 178/123 | 21,276 | 9.2   | Ν  | 252       | 0.7     | 2,778   |  |  |  |

| C6288A  | 2,416 | 32/32   | 22,174 | 9.2   | Ν  | 1,601,943 | 2,782.6 | 1,737   |  |  |  |

| C7552A  | 3,512 | 207/108 | 28,277 | 8.1   | Ν  | 10,824    | 8.5     | 785     |  |  |  |

Benchmark outputs were ANDed together to produce a single output

CPU for software SAT was a 110 MHz processor, 1 MHz clock assumed for FPGA

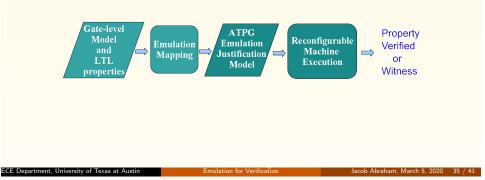

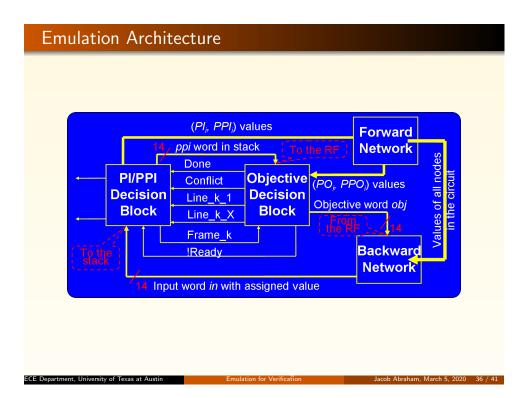

## Emulation Model for Bounded Model Checking Using Sequential ATPG

Qiang et al., 2005

ECE Department, University of Texas at Austi

- Input consists of gate-level circuit and set of properties

- Develop an emulation model that verifies the property

- ATPG Justification part specialized for circuit and properties

ob Abraham, March 5, 2020 34 / 41

## Model Sizes of ISCAS89 Circuits

ECE Department, University of Texas at Austin

|         | Original Model |     |      |       | ATPG Model |          |  |

|---------|----------------|-----|------|-------|------------|----------|--|

| Circuit | Pls            | POs | PPIs | Gates | Gates      | Increase |  |

| s1238   | 14             | 14  | 18   | 508   | 16011      | 30.5     |  |

| s1423   | 17             | 5   | 74   | 657   | 17690      | 25.9     |  |

| s1488   | 8              | 19  | 6    | 653   | 16327      | 24.0     |  |

| s1494   | 8              | 19  | 6    | 647   | 16365      | 24.3     |  |

| s5378   | 35             | 49  | 179  | 2779  | 30862      | 10.1     |  |

| s9234   | 36             | 39  | 211  | 5597  | 42430      | 6.6      |  |

| s13207  | 62             | 152 | 638  | 7951  | 63437      | 7.0      |  |

| s15850  | 77             | 150 | 534  | 9772  | 67855      | 5.9      |  |

| s35932  | 35             | 320 | 1728 | 16065 | 162415     | 9.1      |  |

| s38417  | 28             | 106 | 1636 | 22179 | 143977     | 5.5      |  |

| s38584  | 38             | 304 | 1426 | 19253 | 159249     | 7.3      |  |

$2-3 \mbox{ orders of magnitude speedup over software by using emulation hardware$

acob Abraham, March 5, 2020 37 / 41