# <section-header> Neural Network *"Black Magic Box"*Input vector X Output vector Y guess nonlinear function Dearning: Provide (X,Y) and have the box learn internal variables such that for a given X it has as output the respective Y Use: Provide new X and read the Y Keras: <a href="https://keras.io/">https://keras.io/</a>

# CONTENTS

- 1. Practical ML info

- 2. An Example

- 3. General View

- 4. More Examples

EE 382M-11, Verification of Digital Systems, Spring 2020 Department of Electrical and Computer Engineering The University of Texas at Austin

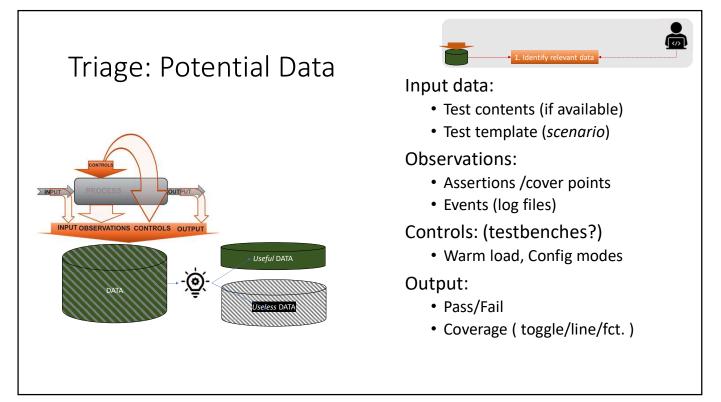

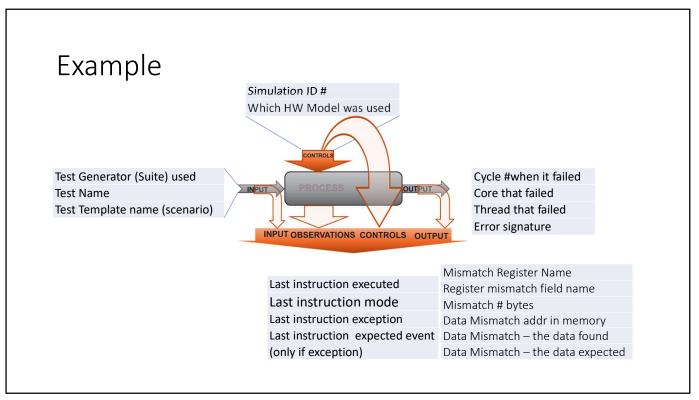

| Test Generator (Suite) used    |                  |            | Ľ                | Data         | Pro             | cess       | sing:         |                      |

|--------------------------------|------------------|------------|------------------|--------------|-----------------|------------|---------------|----------------------|

| Test Name                      |                  |            |                  |              |                 |            | 0             | •                    |

| Test Template name (scenario)  |                  |            | E                | XCIU         | lae             | & CI       | hang          | e                    |

| Simulation ID #                |                  |            |                  |              |                 |            |               |                      |

| Which HW Model was used        |                  |            |                  |              |                 |            |               |                      |

| Last instruction executed      |                  | AD: OP: N  | MOV [EAX],0x     | 000C0045     |                 | - MOVE     |               |                      |

| Last instruction mode          |                  | Mode befo  | ore / Mode afte  | er ( same or | different ) . e | x. PmSVG64 | , Cm32,       |                      |

| Last instruction exception     |                  | Exception  | ID – hierarchica | al info      |                 |            |               |                      |

| Last instruction expected ever | t                |            |                  |              |                 |            |               |                      |

| (only if exception)            |                  |            |                  |              |                 |            |               |                      |

| Cycle #when it failed          | → X < th1; th1 < | x < th2; x | > th2            |              |                 |            |               |                      |

| Core that failed               |                  |            |                  |              |                 |            |               |                      |

| Thread that failed             |                  |            |                  |              |                 |            |               | See.e                |

| Error signature                |                  | -          |                  |              | -               | -          | ter mismatch) | 50° 88°              |

| Mismatch Register Name         |                  | R1         | R2               | R3           | R4              | R5         | R6            | TO WIT               |

| Register mismatch field name   |                  | 1          | 0                | 0            | 1               | 1          | 0             | on the               |

| Mismatch # bytes               |                  |            |                  |              |                 |            |               | at set               |

| Data Mismatch addr in memor    | +                |            |                  |              |                 |            |               | Noil et              |

| Data Mismatch – the data four  | <del>d</del>     |            |                  |              |                 |            |               | Main connor sonse de |

| Data Mismatch - the data expe  | cted             |            |                  |              |                 |            |               |                      |

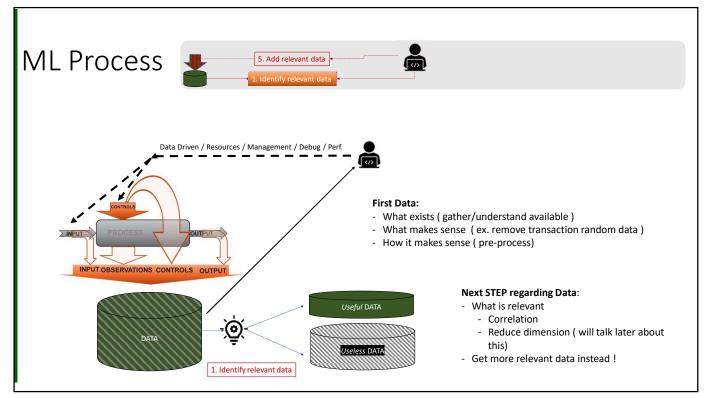

# Why Data Pre-processing

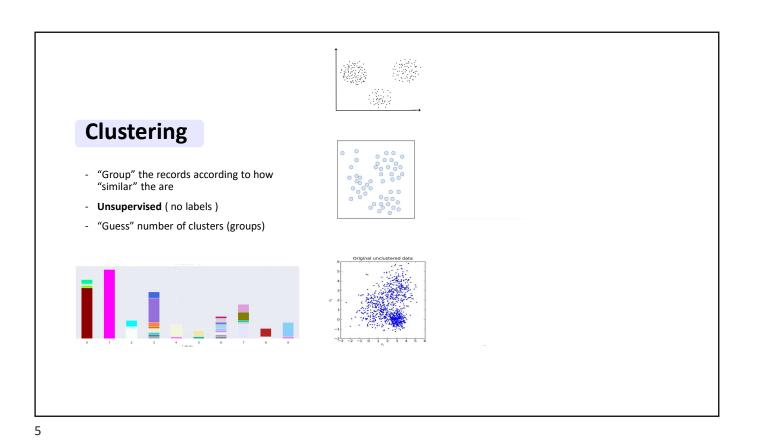

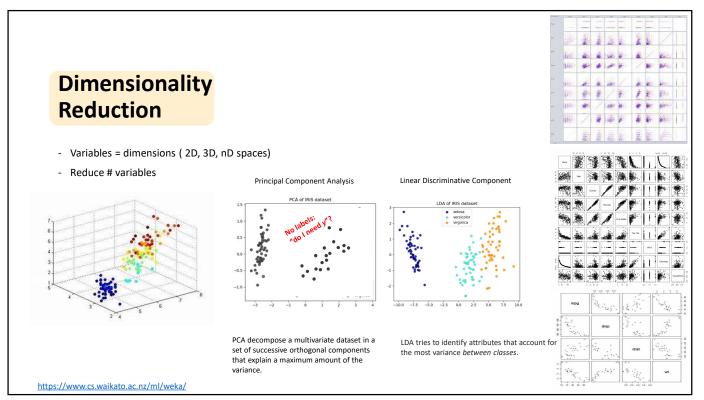

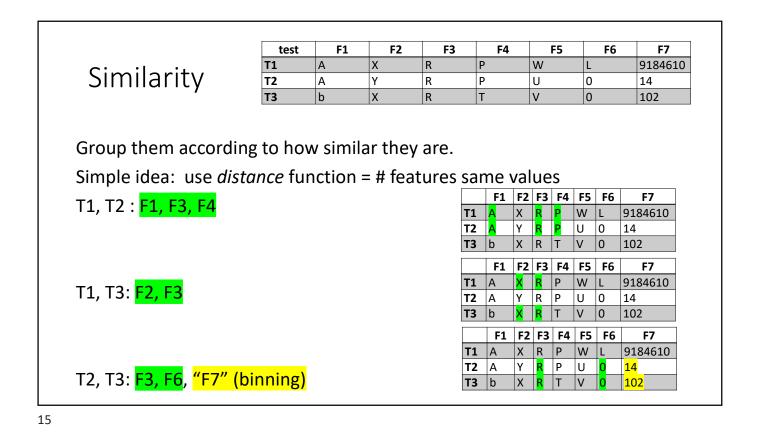

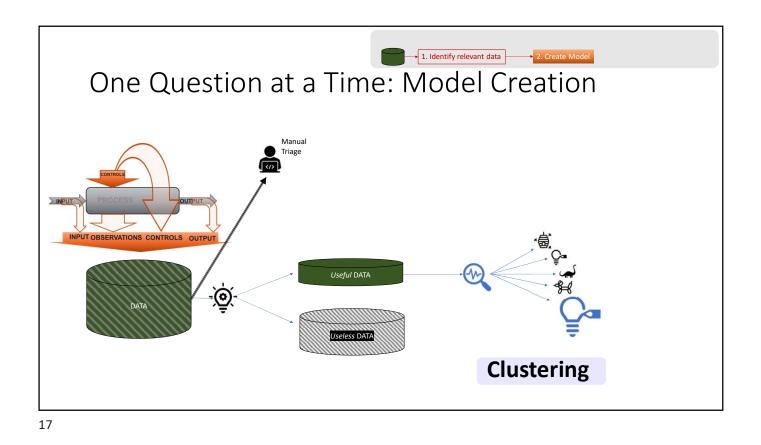

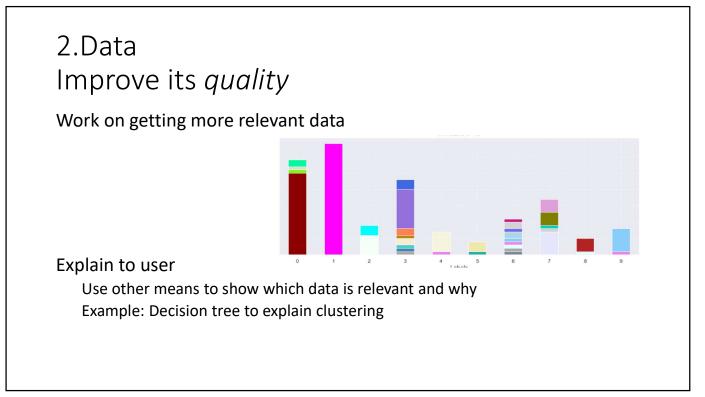

Grouping according to similarity, data can *help*, *harm* or be just *useless*.

| test | F1 | F2 | F3 | F4 | F5 | F6 | F7      |

|------|----|----|----|----|----|----|---------|

| T1   | А  | Х  | R  | Р  | W  | L  | 9184610 |

| T2   | А  | Υ  | R  | Р  | U  | 0  | 14      |

| ТЗ   | b  | Х  | R  | Т  | V  | 0  | 102     |

Useless:

- F3: all tests have same value. F3 doesn't help and it doesn't hurt. It simply doesn't provide information (and clogs the system).

- F5: each test has a different value. F5 doesn't help and doesn't hurt. It simply doesn't provide information.

### Help:

- F1: T1 and T2 "score" a similarity. T3 is not similar to T1, nor T2

- F2: T2 and T3 "score" a similarity. T2 doesn't.

- F4: Again, T1 and T2 "score" a similarity.

- ⇒ {T1, T2} score more similar features than {T1, T3} or {T2,T3} therefore (!) it is more likely for T1 and T2 to fail due to the same bug

### Harm:

- F6: the lack of information (NaN) is perceived as '0' here and it counts as if T2 and T3 'score' a similarity.

- F7: randomly generated data is generally binned and because T2 and T3 have small values, they will end up in the same "bin" and here is another wrongly perceived similarity between T2 and T3. (random is not uniformly distributed, and even if, binning would still create information from where there's none)

The two harmful => misinformation => {T2, T3} seem closer to each other ( wrong!)

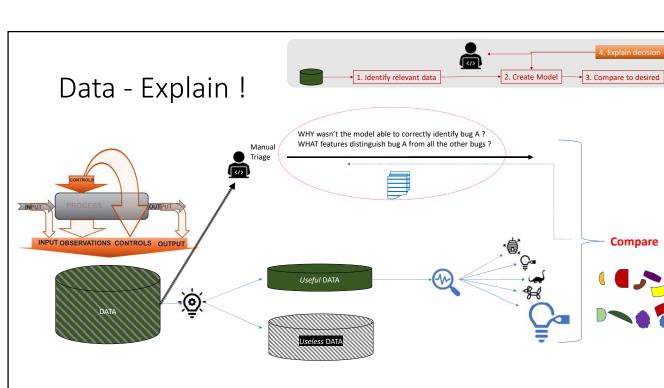

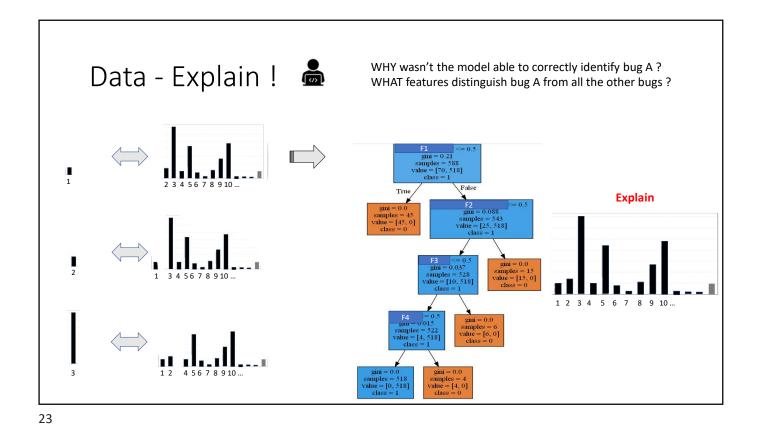

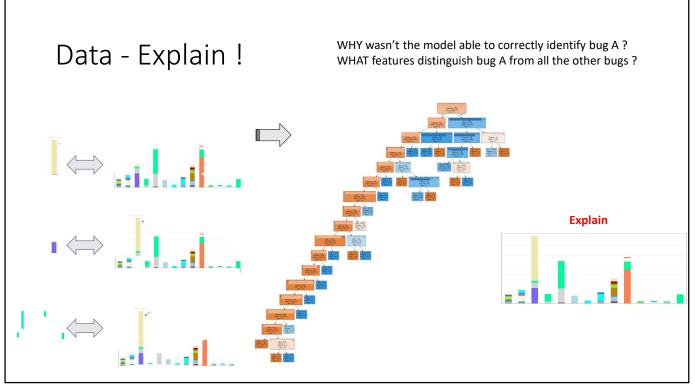

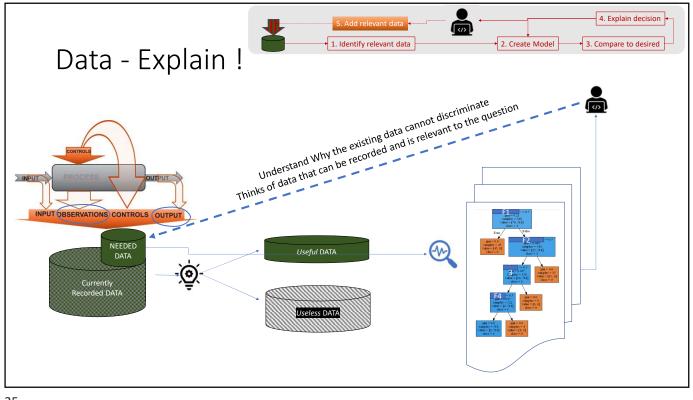

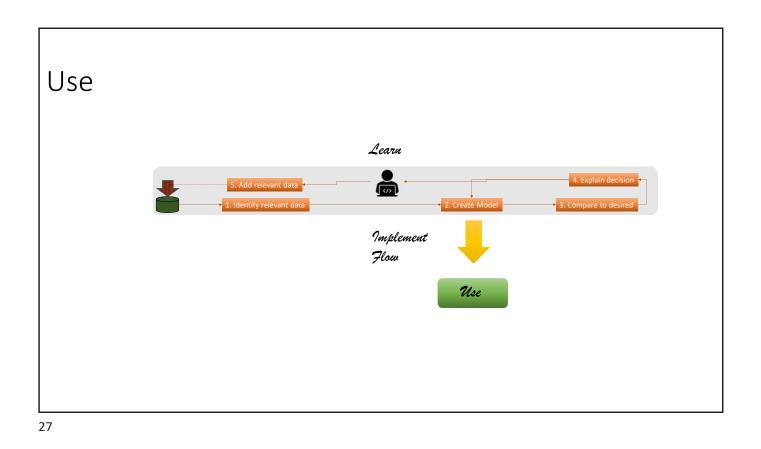

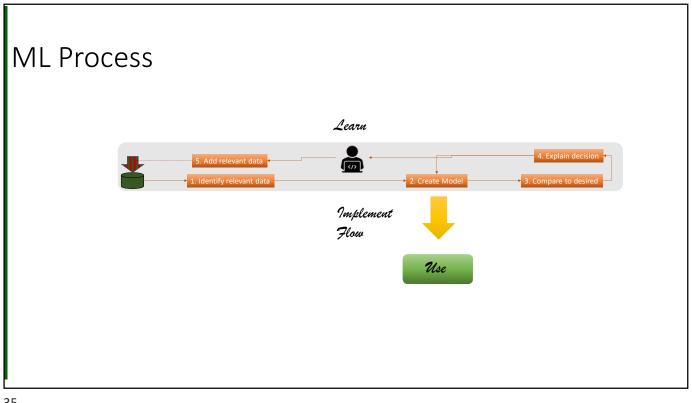

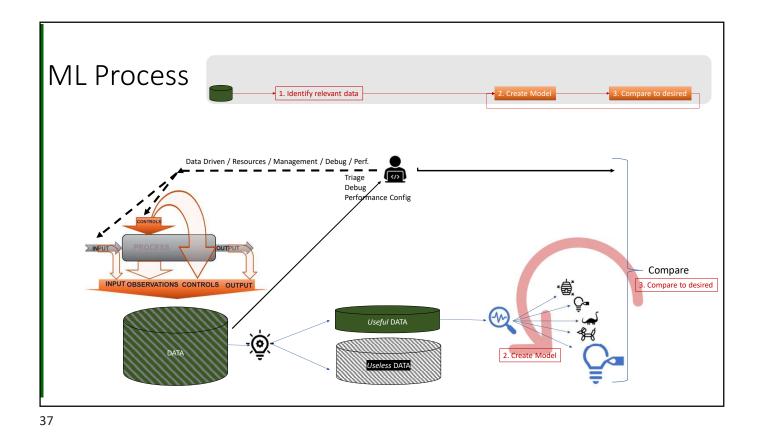

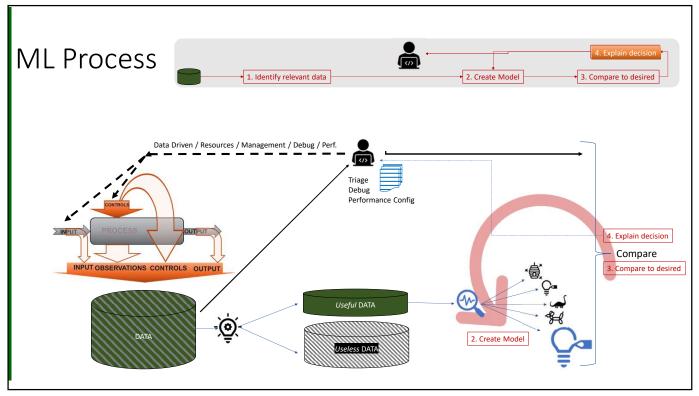

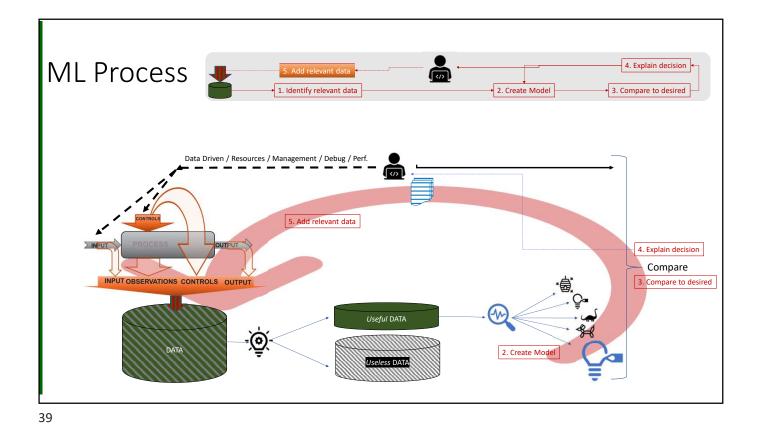

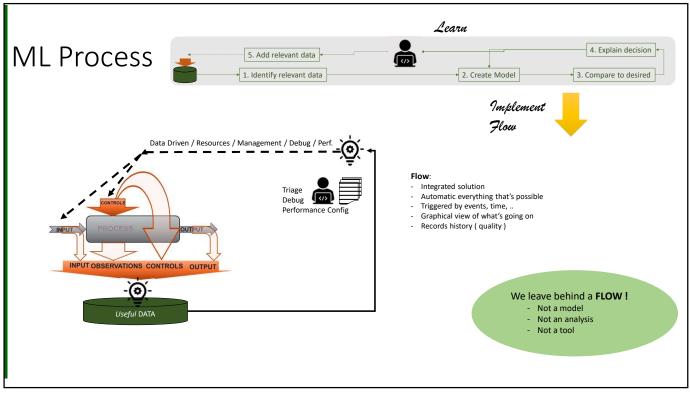

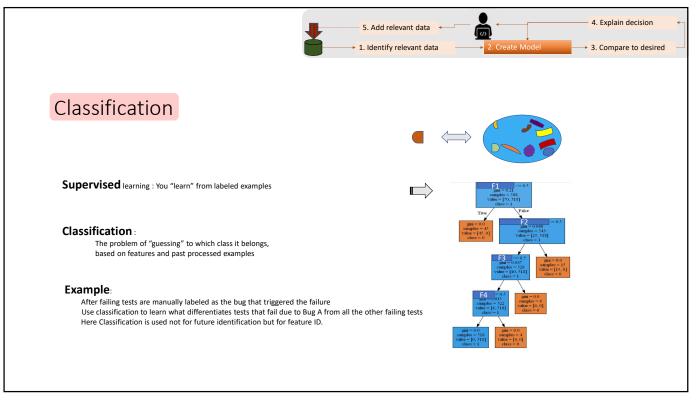

Explain decis

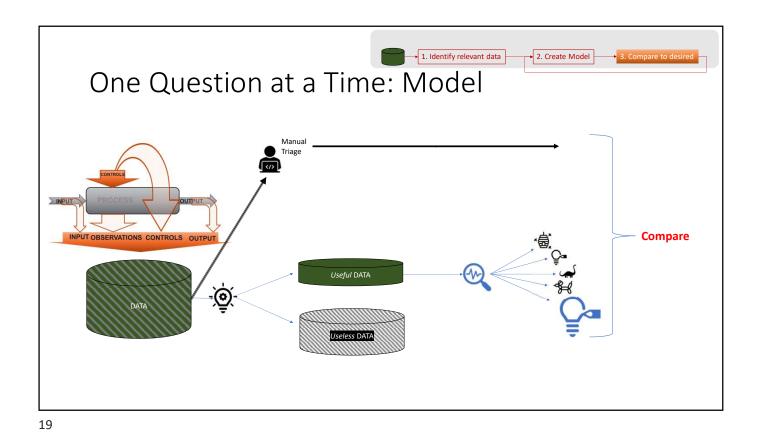

Compare

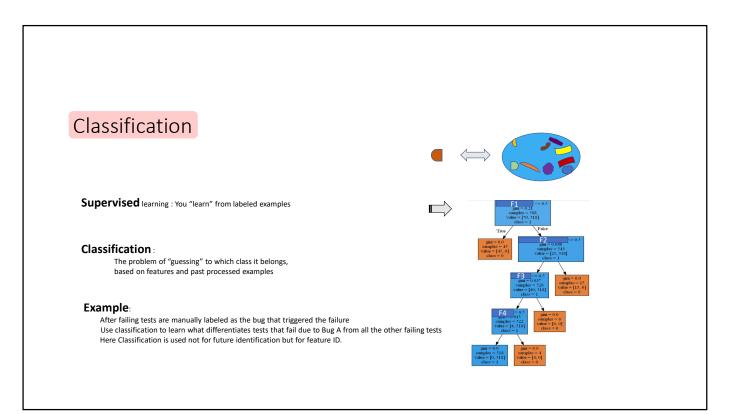

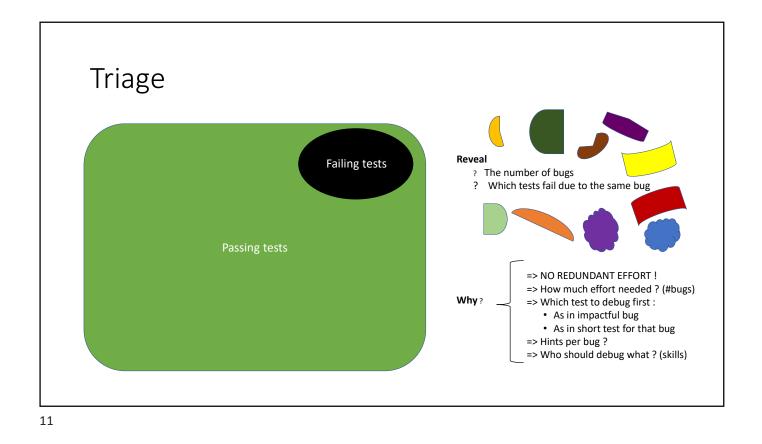

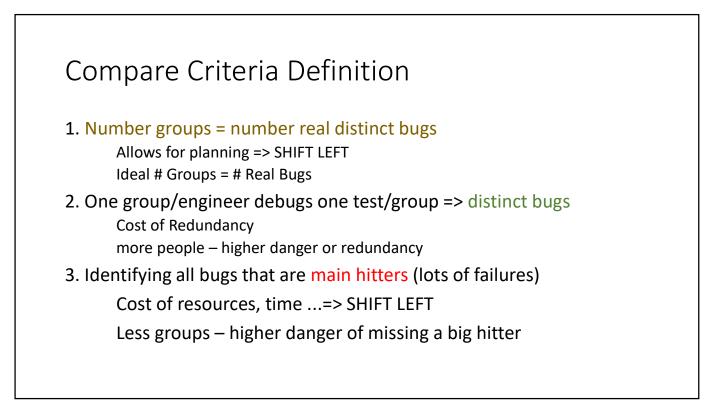

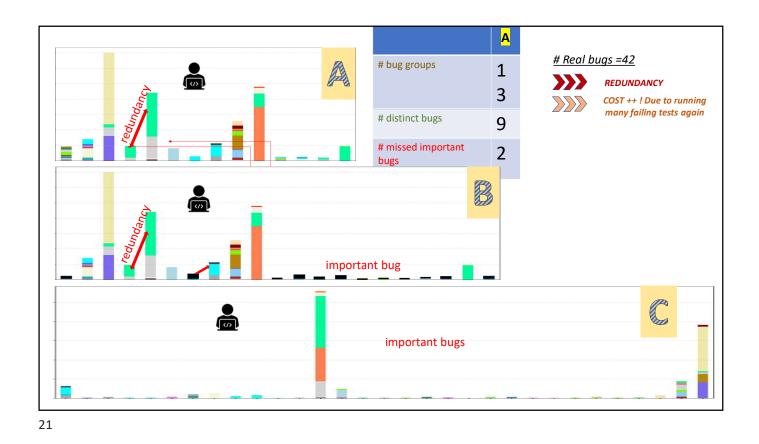

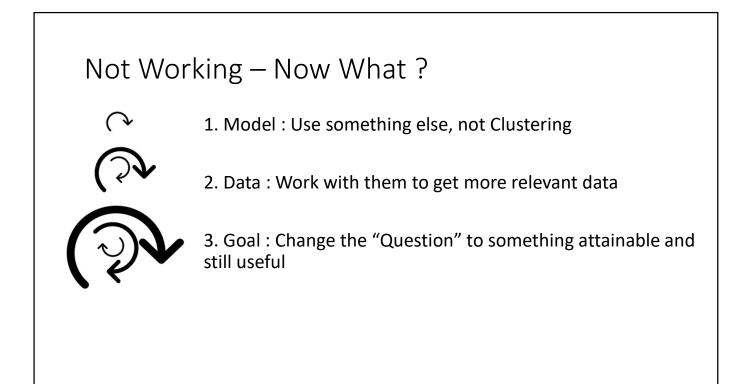

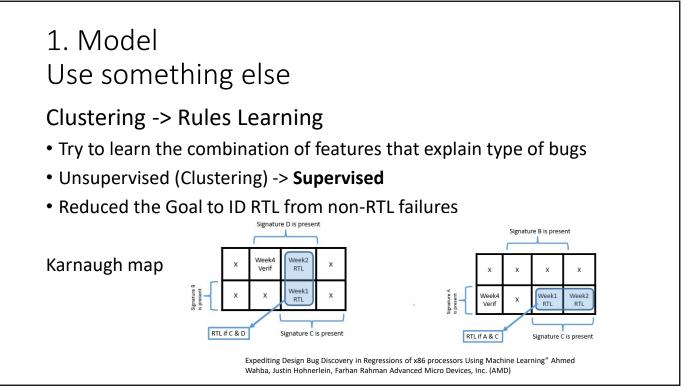

# 3. Goal Change it to something attainable

- 1. Triage by initial definition

- Divide the failed tests into groups such that each group of tests failed due to the same **unique** bug.

- 2. Min Overlap

- Divide the failing tests into as many groups as available verification engineers, with the condition that the likelihood of two of them debugging the same bug is minimized.

- 3. RTL vs. non-RTL

- <u>Learn</u> from the past what combination of features points to RTL respectively non-RTL bugs and use it in the next iteration. Update rules every time you get a new batch.

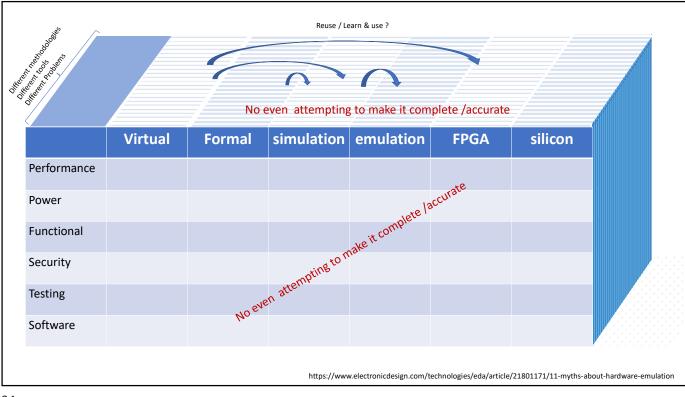

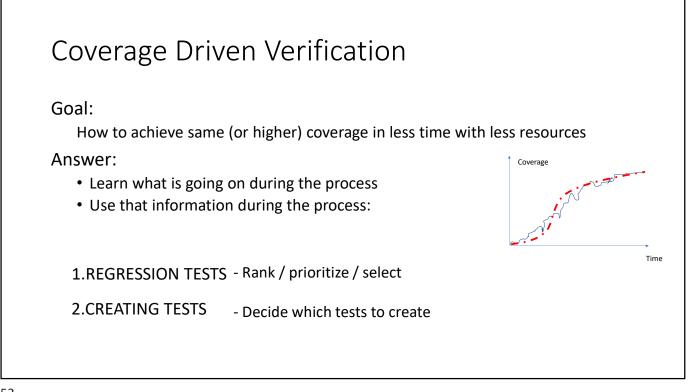

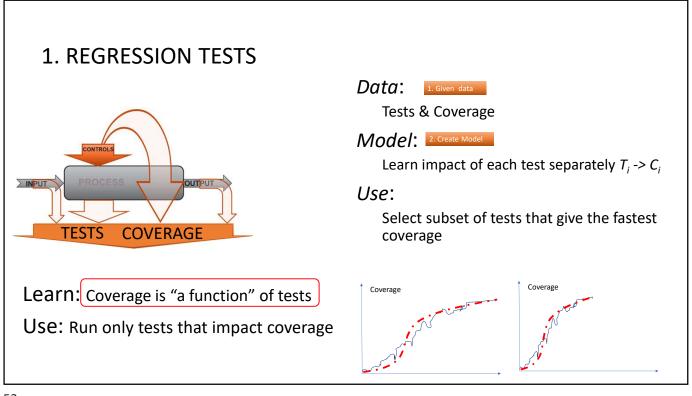

|                         | What types of problems we can solve                                                                                         |  |  |  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

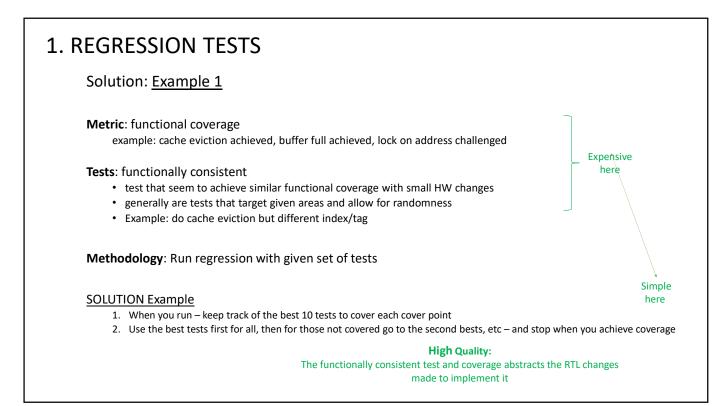

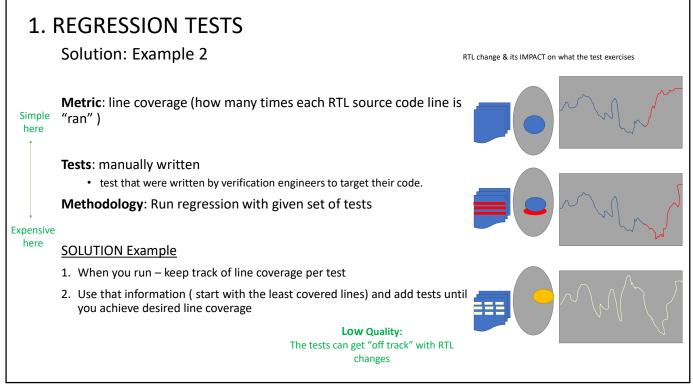

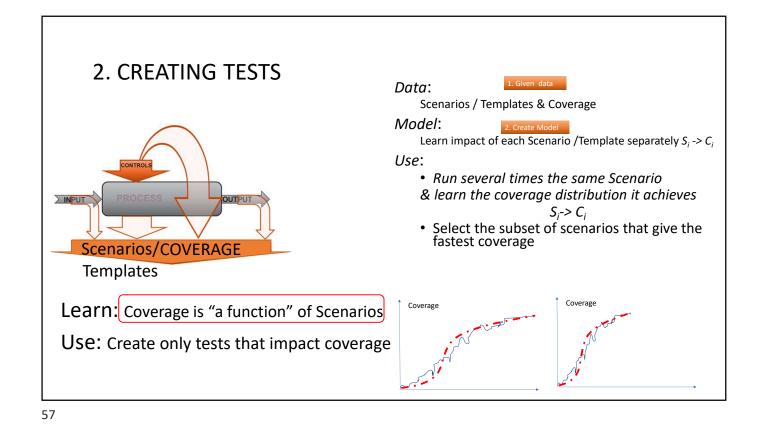

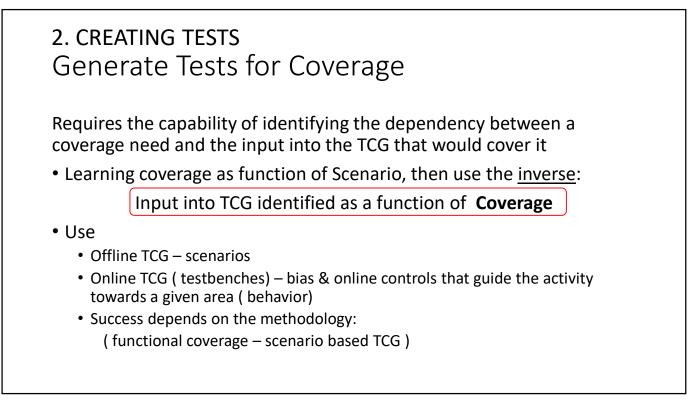

| Functional verification | <ul> <li>Which (existing) tests to run to achieve coverage faster</li> </ul>                                                |  |  |  |  |  |

|                         | <ul> <li>What type of test to create to verify (given/all) area</li> </ul>                                                  |  |  |  |  |  |

| Debugging               | <ul> <li>Which tests failed due to the same bug</li> </ul>                                                                  |  |  |  |  |  |

|                         | How many distinct bugs are in there                                                                                         |  |  |  |  |  |

|                         | <ul> <li>What characteristics do the tests failing (presumably same bug) have</li> </ul>                                    |  |  |  |  |  |

|                         | <ul> <li>How is the behavior of <u>one</u> failing test different than the behavior of similar<br/>passing tests</li> </ul> |  |  |  |  |  |

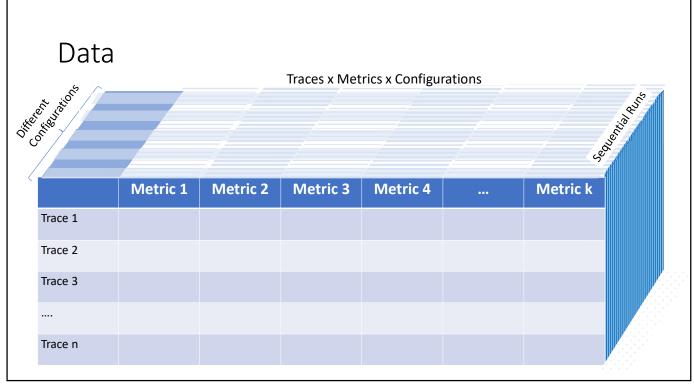

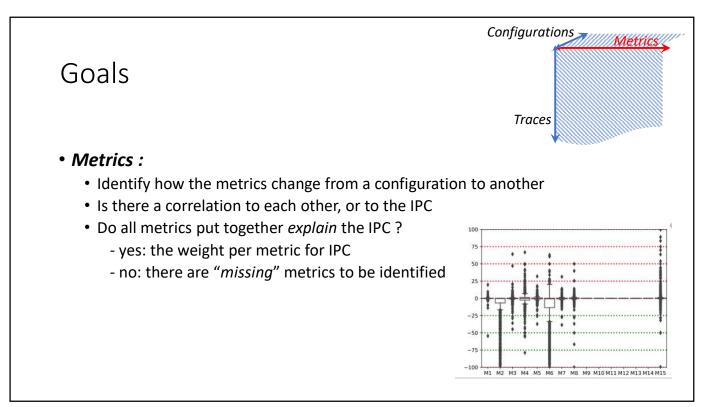

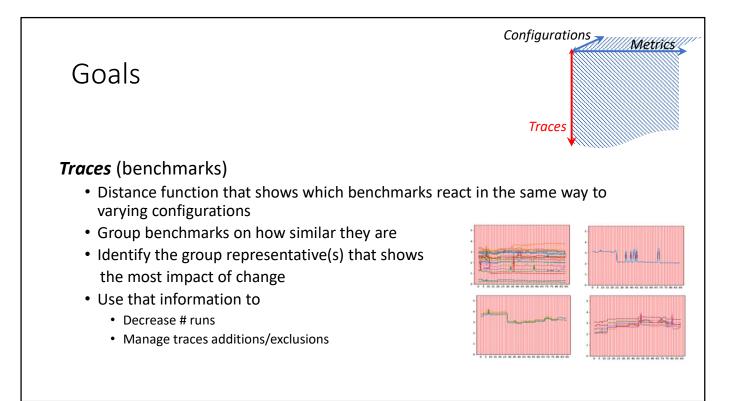

| Performance             | <ul> <li>Which benchmark to run (as in keep/replace/remove)</li> </ul>                                                      |  |  |  |  |  |

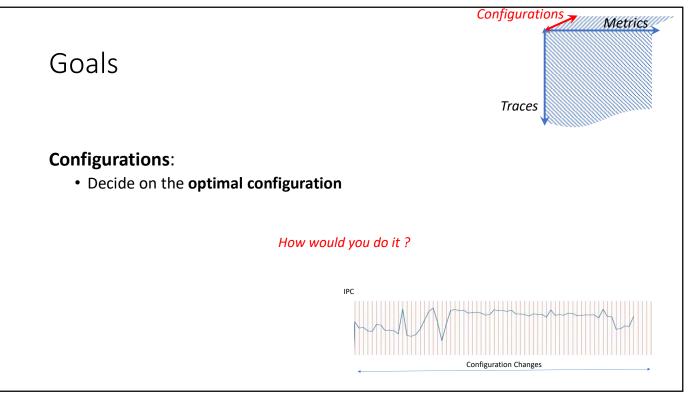

|                         | <ul> <li>What configuration ( as in modes) is optimal for performance</li> </ul>                                            |  |  |  |  |  |

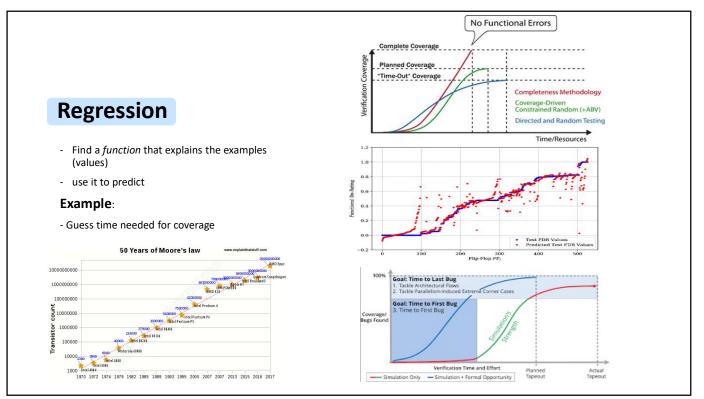

| Management              | <ul> <li>How close am I to finish ? (coverage curve)</li> </ul>                                                             |  |  |  |  |  |

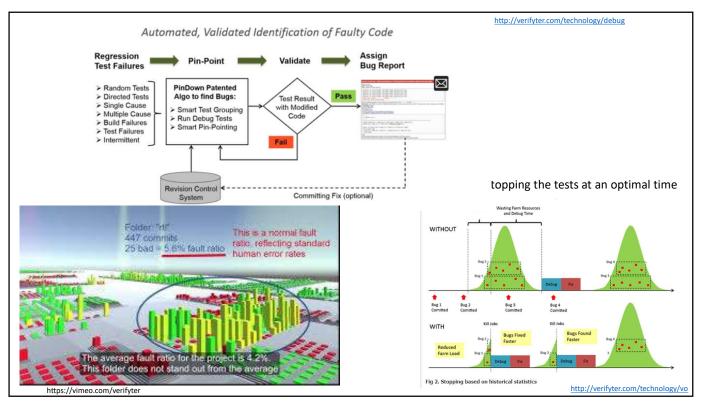

|                         | <ul> <li>Who inserted the bug, in which version of which file</li> </ul>                                                    |  |  |  |  |  |

|                         | Which files should be rewritten                                                                                             |  |  |  |  |  |

| Resources               | <ul> <li>What resource (processing power + memory) is needed by this run ( simulation<br/>– run attributes)</li> </ul>      |  |  |  |  |  |

|                         | <ul> <li>Which engine / heuristics is best (as in formal)</li> </ul>                                                        |  |  |  |  |  |

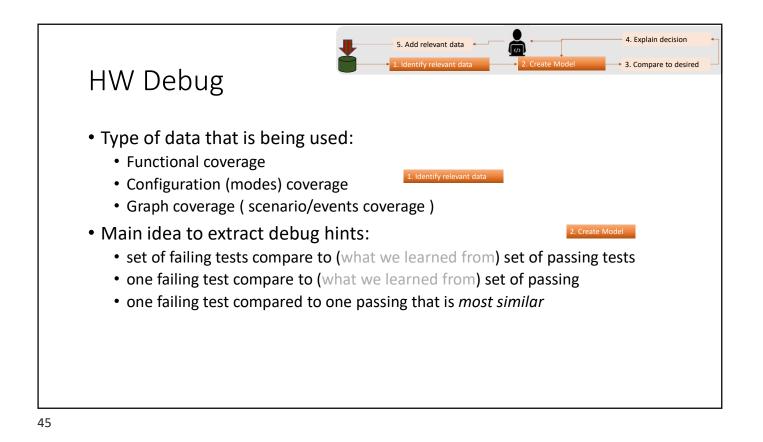

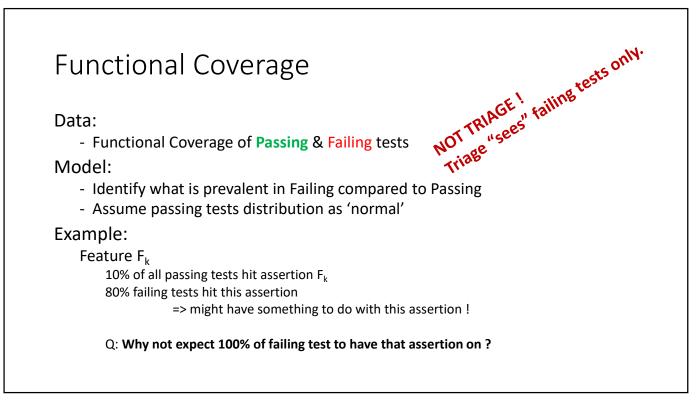

# Register Configurations (Modes)

## Data:

- Configuration (Modes) of passing & failing tests

Model:

- Identify what is prevalent in Failing compared to Passing

- Assume passing tests distribution as 'normal'

Example: identify all the register configurations  $C_k$  that seem to be correlated with the failing tests

Feature C<sub>k</sub>

10% of all passing tests have configuration  $C_k$ 80% failing tests have configuration  $C_k$ => might have something to do with this configuration !

# Metric Driven Verification

Coverage & Other - Driven Verification

# Formal

Goal: Which heuristics are best for a given type of problem

Data:

- problem (type)

- heuristic (used)

- resources (time/ processing power/ memory size)

Model:

• Learn resource = function (problem, heuristic)

Use:

• Heuristic = function ( problem)

69

# Processing Power Goal: What resources to allocate per simulation request Data: Project for which we run the simulation Model requested Team requesting it Test case name (family) Allocated resources Used resources = function ( project/model/team/testname) Use: Allocate resources accordingly, with a likelihood of being wrong and still save

# Management

## 71

# Project Management

- Complex systems intended to control a project's management

- Use a variety of sources

- Have a variety of goals

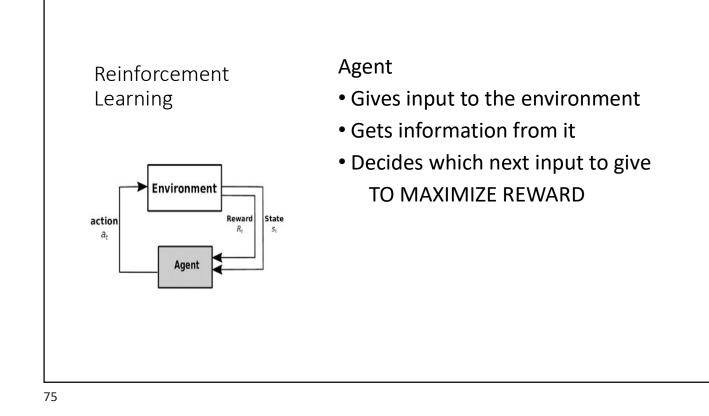

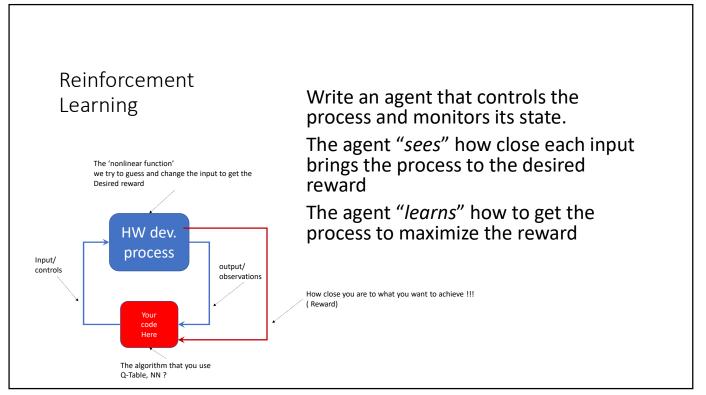

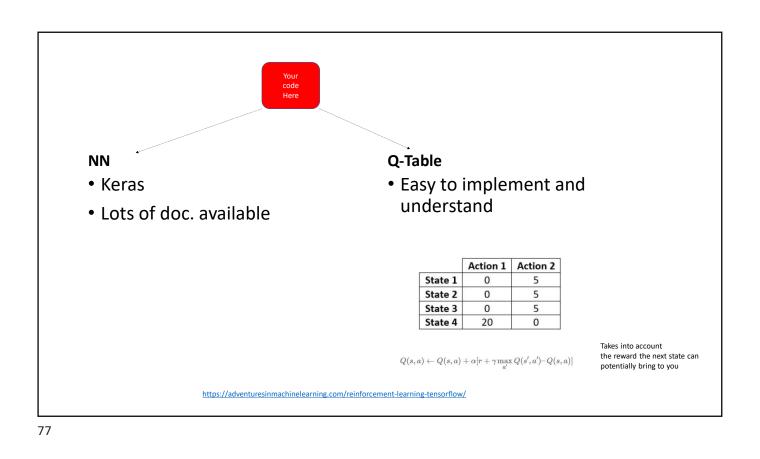

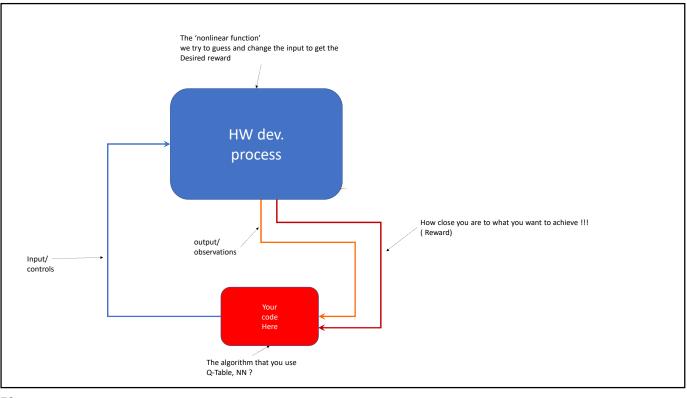

# Conditions for success

- Fast process

- Takes a lot of steps to learn the input needed to maximize reward

- Not useful if each step takes a long time and is expensive

- Reward measurement

- The reward is a value that shows how well the system did considering the input. Difficult to define and to measure. ( distance function from some desired state)

- Process Uncertainty

- Works best if I/O without internal memory

- Processes have internal memories more difficult to learn