## Goals of This Course

ECE Department, University of Texas at Austin

#### Learn the principles of VLSI design

- Learn to design and implement state-of-the-art digital Very Large Scale Integrated (VLSI) chips using CMOS technology

- Understand the complete design flow

- Be able to design state-of-the-art CMOS chips in industry

#### Employ hierarchical design methods

- Use integrated circuit cells as building blocks

- Understand design issues at the layout, transistor, logic and register-transfer levels

Jacob Abraham, August 27, 2020 1 / 47

• Use Commercial Design Software in the lab

## Early Ideas Leading to the Transistor

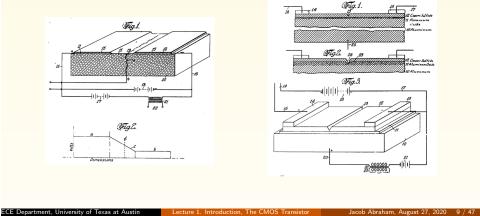

## J. W. Lilienfelds patents

1930: "Method and apparatus for controlling electric currents," U.S. Patent 1,745,175 1933: "Device for controlling electric current," U. S. Patent 1,900,018

- 1940: Ohl develops the PN Junction

- 1945: Shockley's laboratory established

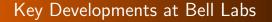

- 1947: Bardeen and Brattain create point contact transistor (U.S. Patent 2,524,035)

## Developments at Bell Labs, Contd

ECE Department, University of Texas at Au

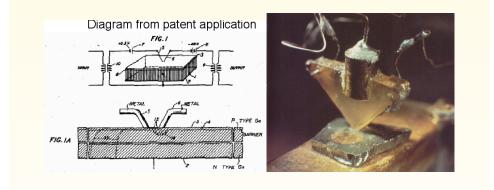

• 1951: Shockley develops a junction transistor manufacturable in quantity (U.S. Patent 2,623,105)

The CMOS Transist

im, August 27, 2020 10 / 47

Jacob Abraha

# 1950s Silicon Valley

- 1950s: Shockley in Silicon Valley

- 1955: Noyce joins Shockley Laboratories

- 1954: The first transistor radio

- 1957: Noyce leaves Shockley Labs to form Fairchild with Jean Hoerni and Gordon Moore

- 1958: Hoerni invents technique for diffusing impurities into Si to build planar transistors using a SiO<sub>2</sub> insulator

- 1959: Noyce develops first true IC using planar transistors, back-to-back PN junctions for isolation, diode-isolated Si resistors and SiO<sub>2</sub> insulation with evaporated metal wiring on top

I. Introduction, The CMOS Transist

Jacob Abraham, August 27, 2020 12 / 47

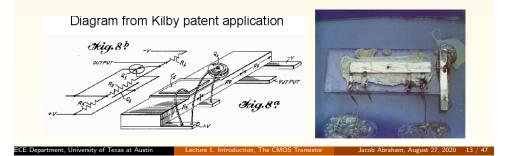

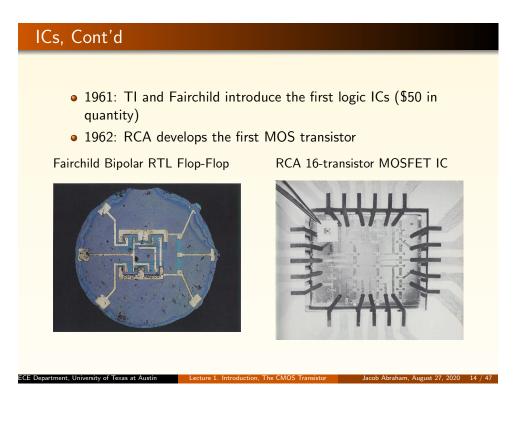

### The Integrated Circuit (IC)

ECE Department, University of Texas at Aus

- 1958: Jack Kilby, working at TI, dreams up the idea of a monolithic "integrated circuit" (IC)

- Components connected by hand-soldered wires and isolated by shaping, PN-diodes used as resistors (U.S. Patent 3,138,743)

- 1959: Robert Noyce, at Fairchild, independently develops the IC, solving many practical problems

- 2000: Kilby receives Nobel Prize in Physics (Noyce was no longer alive)

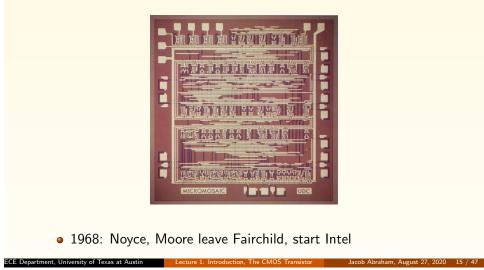

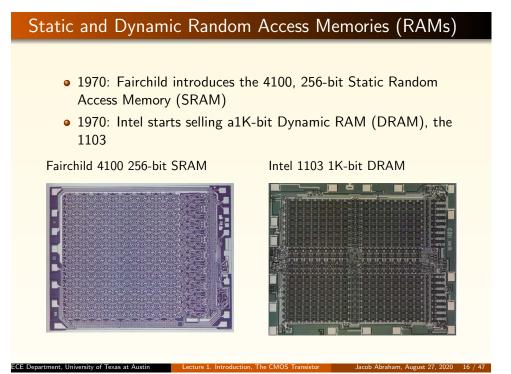

## Computer-Aided Design (CAD)

- 1967: Fairchild develops the Micromosaic IC using CAD

- Final Al layer of interconnect could be customized for different application

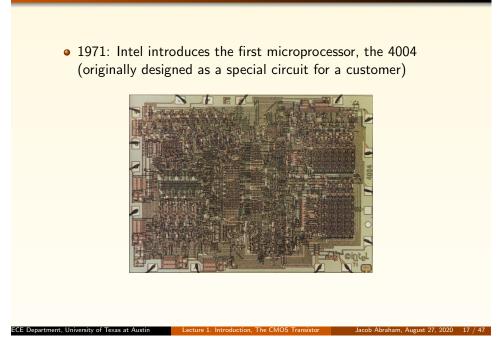

### The Microprocessor!

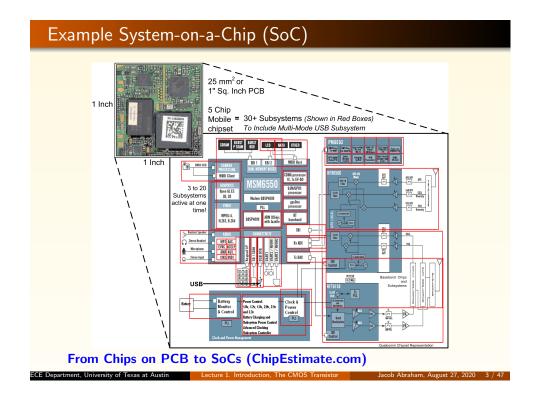

## VLSI Design – The Big Picture

Department of Electrical and Computer Engineering, The University of Texas at Austin J. A. Abraham, August 27, 2020

#### Work in the Course

#### Lectures

- Read sections in text and slides before class

- Homework problems

- Solve related problems posted every week

- Laboratory exercises

- Three major exercises dealing with various aspects of VLSI design

- Complete each section before the deadline

- Project (EE 382M)

- Your opportunity to design a chip of interest to you

- Design could be completed to the point where it could be fabricated by following process covered this course

- Course involves a large amount of work throughout the semester

re 1. Introduction, The CMOS Transistor

Jacob Abraham, August 27, 2020 20 / 47

Jacob Abraham, August 27, 2020 21 / 47

### Types of Integrated Circuit (IC) Designs

IC Designs can be Digital (covered in this course), Analog, RF or mixed-signal

#### Digital designs

ECE Department, University of Texas at Austi

- Full Custom

- Every transistor designed and laid out by hand

- Used for memories, datapaths in high performance processors, etc.

- ASIC (Application-Specific Integrated Circuits)

- Designs synthesized automatically from a high-level language description

- Semi-Custom

ECE Department, University of Texas at Austin

• Mixture of custom and synthesized modules

This course will cover all these design techniques

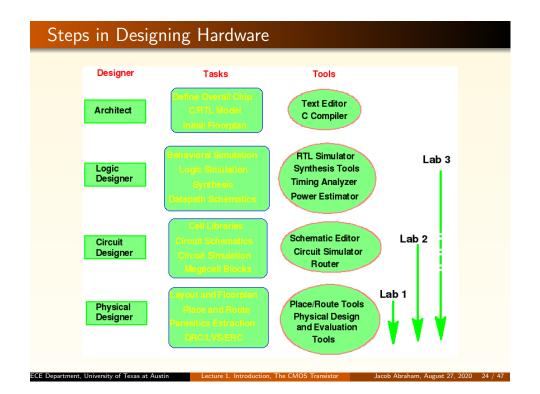

## Laboratory Exercises

ECE Department, University of Texas at Austin

Exercise 1: Design, layout and evaluation of a register file

• Use Cadence layout software, HSpice simulation

Exercise 2: Design and evaluation of an ALU with standard cell libraries

• Cadence schematic editor, Synopsys static timing analysis, Cadence place-and-route

#### Exercise 3: RT-level design and evaluation of bus controller

- Synopsys simulation, Synopsys synthesis, Cadence place-and-route

- We will use an academic 45 nm standard cell library for the lab exercises

Jacob Abraham, August 27, 2020 23 / 47

uction, The CMOS Transistor

### Term Project (Graduate Students)

- Form 2 3 person teams

- Pick project

ECE Department, University of Texas at Austin

- Based on something of interest to you

- Discuss thoughts with me

- Look at list of suggestions

- Complete design

- Evaluate design (for performance, power, etc.)

- Demonstrate operation

- Write report

ECE Department, University of Texas at Austin

Meet published deadlines

Jacob Abraham, August 27, 2020 26 / 47

Jacob Abraham, August 27, 2020 27 / 47

Lecture 1. Introduction, The CMOS Transistor

### Exams, Homework and Project

- Two exams, in class, open book and notes

- Final Exam (Undergraduates)

- Term project (Graduates)

- Penalty for late submission in labs: 5% per working day, maximum 25% (no submissions accepted after 5 working days)

- Bonus (for labs), early submission: 5% per working day (maximum 10%)

- Homework: work in teams

- Homework due one week after it is posted (upload your work to Canvas

- Submit one homework per "team", note all names on the sheet

- Solutions will be posted on Canvas one week after problem set posted

e 1. Introduction, The CMOS Transistor

## **Grading Policy**

ECE Department, University of Texas at Austin

ECE Department, University of Texas at Austir

#### Grades will be absolute

- Grades based on demonstration of your knowledge of VLSI design

- Knowledge of fundamentals: homework, exams

- Practical application: laboratory exercises, project

#### Graduate Students

| Homework       | 10% |

|----------------|-----|

| Exams I and II | 30% |

| Laboratory     | 45% |

| Term Project   | 15% |

#### Undergraduate Students

Jacob Abraham, August 27, 2020 28 / 47

| Homework       | 10% |

|----------------|-----|

| Exams I and II | 25% |

| Laboratory     | 45% |

| Final Exam     | 20% |

Jacob Abraham, August 27, 2020 29 / 47

### What Will You Learn?

ECE Department, University of Texas at Austin

- How integrated circuits work

- How to design chips with millions of transistors

- Ways of managing the complexity

- Use of tools to speed up the design process

- Identifying performance bottlenecks

- Ways of speeding up circuits

- Making sure the designs are correct

- Making the chips testable after manufacture

- Other issues: effect of technologies, reducing power consumption, etc.

Jacob Abraham, August 27, 2020 31 / 47

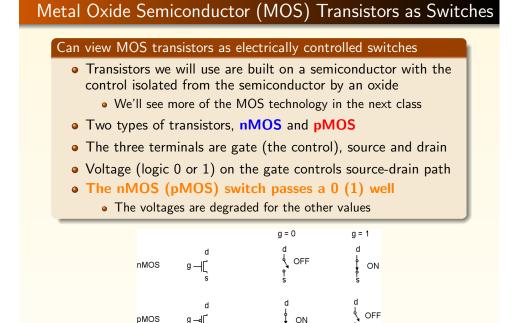

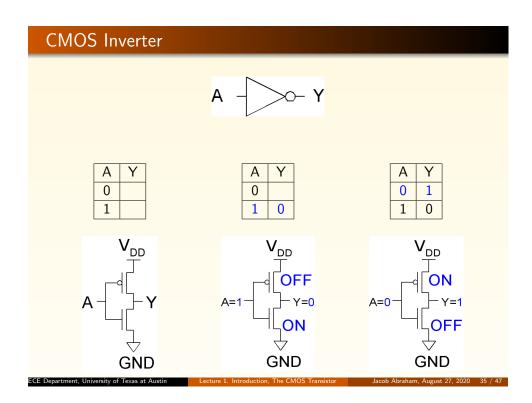

### Voltages and Logic Levels

Represent logic levels with different voltages

- Ground (GND,  $V_{SS}$ ) = 0V can represent logic 0

- Power supply  $(V_{DD})$  can represent logic 1

#### Decreasing voltages

ECE Department, University of Texas at Austin

- In 1980s,  $V_{DD} = 5V$

- V<sub>DD</sub> has been decreasing in modern processes

- High  $V_{DD}$  would damage modern tiny transistors

Jacob Abraham, August 27, 2020 33 / 47

- Lower  $V_{DD}$  saves power

- $V_{DD} = 3.3, 2.5, 1.8, 1.5, 1.2, 1.0, 0.9, \dots$

ECE Department. Univ

August 27, 2020 34 / 47

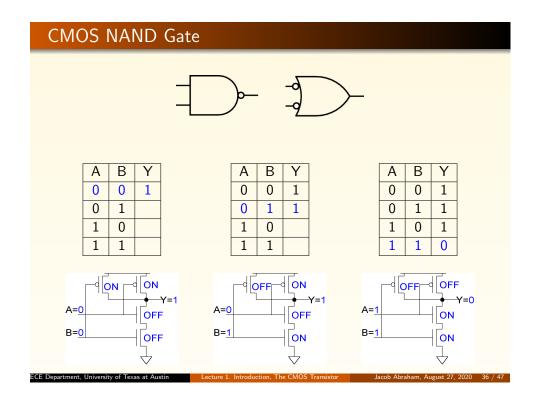

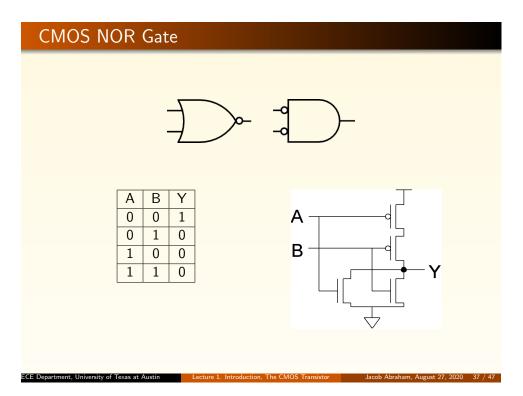

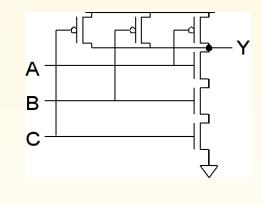

## 3-Input NAND Gate

- Y pulls low if ALL inputs are 1

- Y pulls high if ANY input is 0

# Characteristics of CMOS Gates

ECE Department, University of Texas at A

#### In general, when the circuit is stable

- There is a path from one supply  $(V_{DD} \text{ or } V_{SS})$  to the output (low static power dissipation)

- There is NEVER a path from one supply to another

#### When circuit is switching

ECE Department, University of Texas at Austin

- There is a momentary drain of current when a gate switches from one state to the other

- Dynamic power dissipation

If a node has no path to power or ground, the previous value is retained due to the capacitance of the node

• Sometimes used as for dynamic storage

August 27, 2020 38 / 47

Jacob Abraham, August 27, 2020 39 / 47

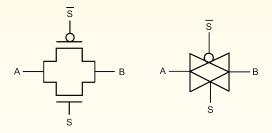

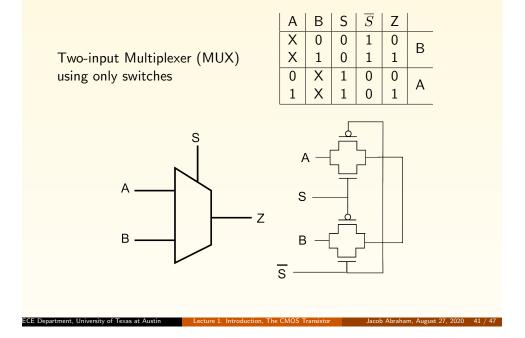

### Complementary Switch (Transmission Gate)

Switch which does not degrade logic values

- Remember, the nMOS (pMOS) switch degrades a 1 (0)

- We'll analyze the electrical characteristics and see the reason for this next week

- Combine n- and p-channel switches in parallel to get a switch which passes both '1' and '0' well

#### Multiplexer

ECE Department, University of Texas at Au

ust 27, 2020 40 / 47

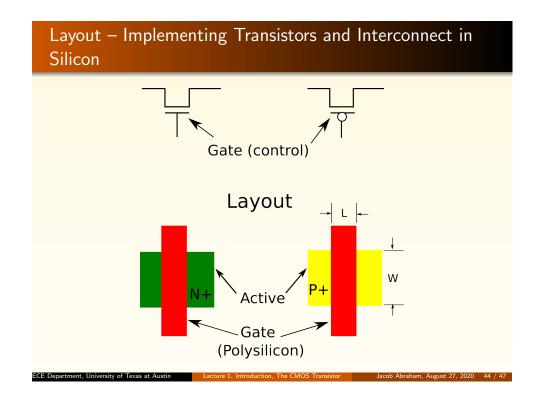

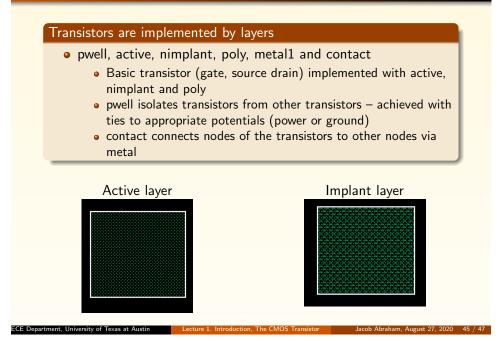

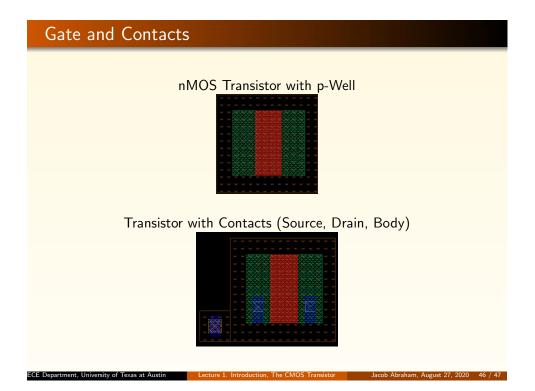

## Laying Out an nMOS Transistor in Cadence

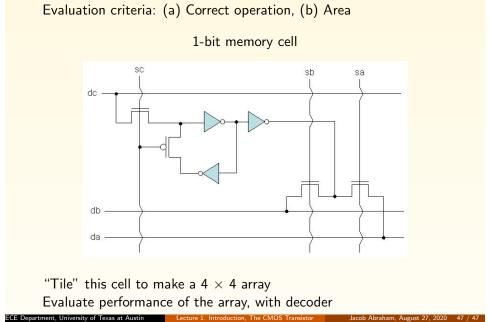

Lab. 1 – 1-bit SRAM, 4  $\times$  4 Array