## Sequencing, Cont'd

- If tokens moved through pipeline at constant speed, no sequencing elements would be necessary

- Example, fiber-optic cable

- Light pulses (tokens) are sent down cable

- Next pulse sent before first reaches end of cable

- No need for hardware to separate pulses

- But dispersion sets min time between pulses

- This is called wave pipelining in circuits

- In most circuits, dispersion is high

- Delay fast tokens so they don't catch slow ones

ECE Department, University of Texas at Austin

Lecture 11. Sequential Elements

Jacob Abraham, October 6, 2020 2 / 3

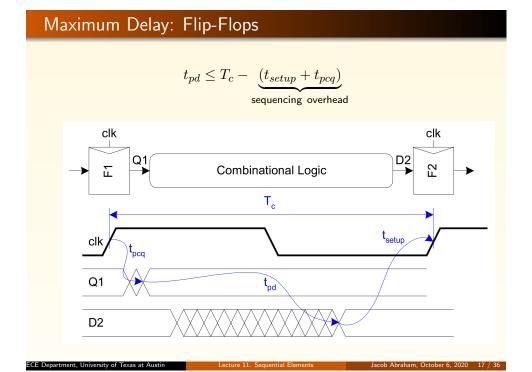

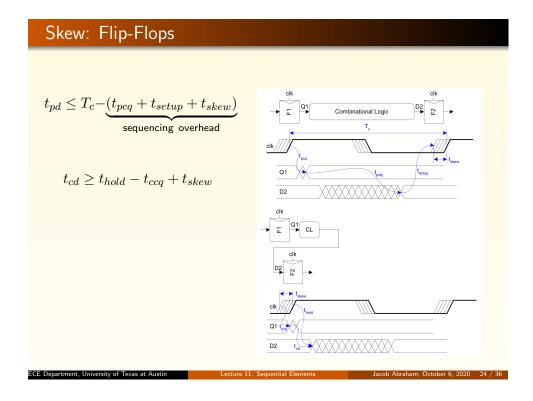

# Sequencing Overhead

- Use flip-flops to delay fast tokens so they move through exactly one stage each cycle

- Inevitably adds some delay to the slow tokens

- Makes circuit slower than just the logic delay

- Called sequencing overhead

- Some people call this clocking overhead

- But it applies to asynchronous circuits too

- Inevitable side effect of maintaining sequence

ECE Department, University of Texas at Austin

Lecture 11. Sequential Elements

Jacob Abraham, October 6, 2020

3 / 36

#

# Example: "Pulsed" Flip-Flop

Inverters in the flip-flop have rise and fall delays of 50 pS NAND gate has a rise delay of 100 pS and a fall delay of 150 pS Assume switching time for transistors is very small

Max. propagation time from D to stable data at latch input,  $t_{Dp}=ps$  Shortest propagation time from D to possibly affecting latch,  $t_{Dc}=ps$  Time from CLK to latch enabled  $=t_{C1}=ps$  Time from CLK to latch disabled  $=t_{C0}=ps$  Setup Time  $=t_{Dp}-t_{c1}=ps$ ; Hold Time  $=t_{C0}-t_{Dc}=ps$  Clock-to-Q  $=t_{C1}$  + delay to output =ps

ECE Department, University of Texas at Austin

Lecture 11. Sequential Elements

cob Abraham. October 6, 2020 16 / 36

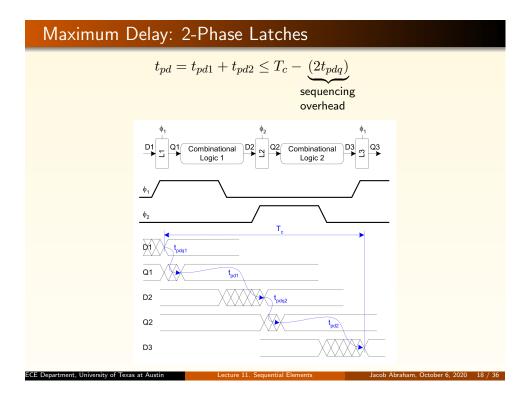

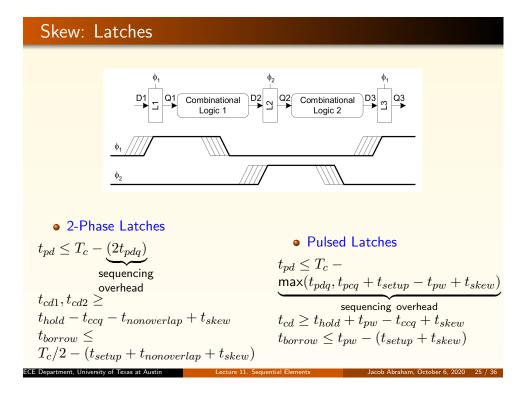

# Two-Phase Clocking

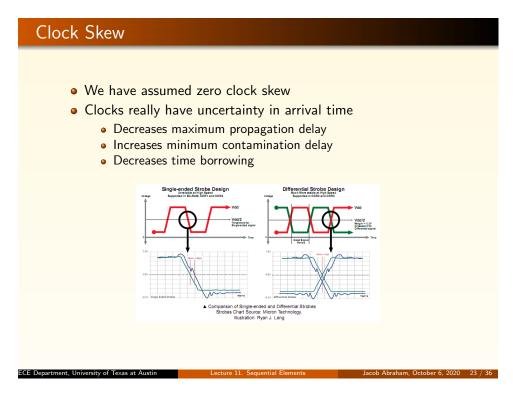

- If setup times are violated, reduce clock speed

- If hold times are violated, chip fails at any speed

- Use tools to analyze clock skew

- Easy way to guarantee hold times: use 2-phase latches with big non-overlap times (used in academic designs)

- Call these clocks  $\phi_1$ ,  $\phi_2$  (ph1, ph2)

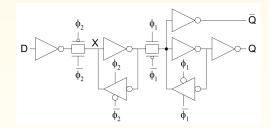

#### Safe Flip-Flop

- Flip-Flop with non-overlapping clocks

- Very slow nonoverlap adds to setup time, but no hold time problem

- Use timing analysis and add buffers to slow signals if hold time is at risk

ECE Department, University of Texas at Austin

Lecture 11. Sequential Elements

cob Abraham, October 6, 2020 26 / 3

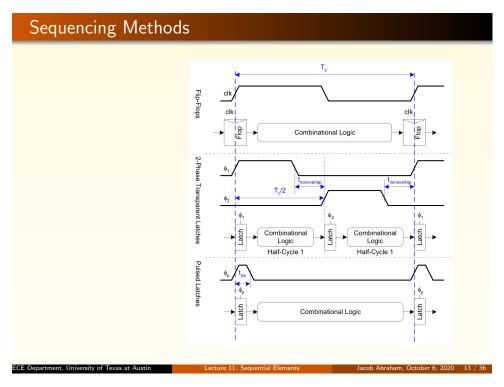

## Summary

- Flip-Flops

- Very easy to use, supported by all tools

- 2-Phase Transparent Latches

- Lost of skew tolerance and time borrowing

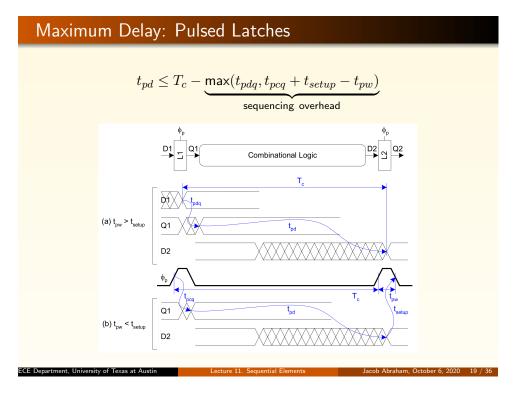

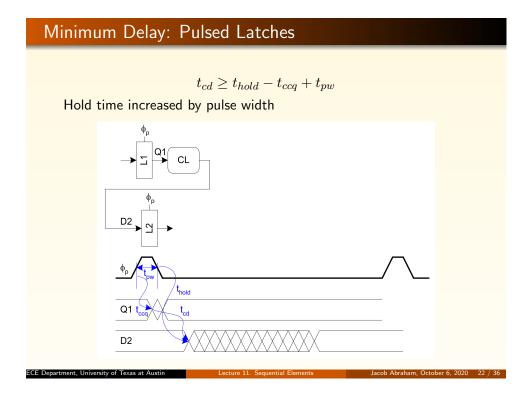

- Pulsed Latches

- Fast, some skew tolerance and borrowing, hold time risk

|                                    | Sequencing overhead $(T_c - t_{pd})$                                                    | Minimum logic delay $(t_{cd})$                                        | Time borrowing $(t_{borrow})$                             |

|------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------|

| Flip-flops                         | $t_{pcq} + t_{setup} + t_{skew}$                                                        | $t_{hold} - t_{ccq} + t_{skew}$                                       | 0                                                         |

| Two-phase trans-<br>parent latches | $2t_{pdq}$                                                                              | $t_{hold} - t_{ccq} - \ t_{nonoverlap} + t_{skew}$ in each half-cycle | $\frac{T_c}{2} - (t_{setup} + t_{nonoverlap} + t_{skew})$ |

| Pulsed latches                     | $egin{aligned} max(t_{pdq}, & t_{pcq} + \ t_{setup} - t_{pw} + t_{skew}) \end{aligned}$ | $t_{hold} - t_{ccq} + t_{pw} + t_{skew}$                              | $t_{pw} - (t_{setup} + t_{skew})$                         |

CE Department, University of Texas at Austin

Lecture 11. Sequential Elements

Jacob Abraham, October 6, 2020 27 / 3

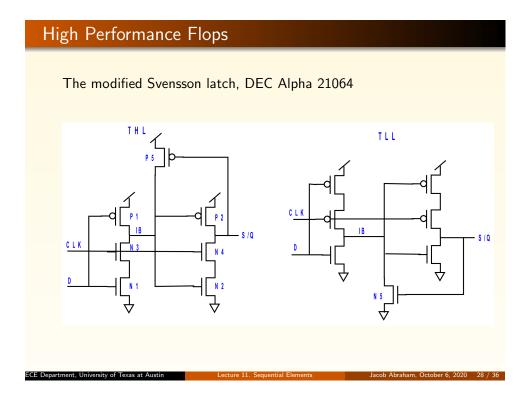

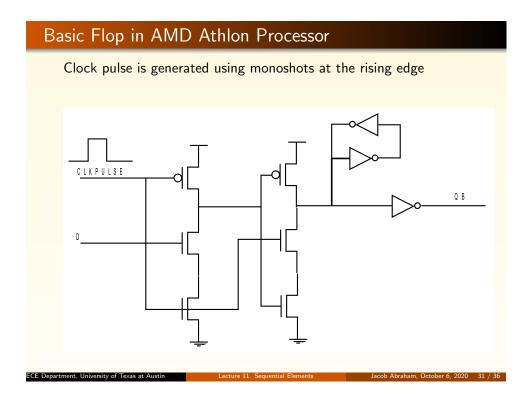

# The hybrid latch flip-flop of AMD K6 The hybrid latch flip-flop of AMD K6 Leture 11. Sequential Elements Jacob Abraham, October 6, 2020 30 / 36

# Fixing Hold-Time Violations

- Measure all hold times with respect to the main clock

- Adjust the hold time if the flop is receiving a delayed clock

- Compute the shortest path delay from the rising edge of the clock

- Check to see if there are any hold time failures

ECE Department, University of Texas at Austin

Lecture 11. Sequential Elements

Jacob Abraham, October 6, 2020 34

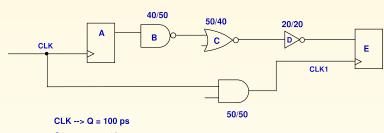

**Example: Fixing Hold-Time Violations**

Setup = 10 ps

Hold = 200 ps (A large hold time is used to illustrate the problem)

Shortest path delay from A  $\rightarrow$  E = 100 + 40 + 40 + 20 = 200 ps Delay between CLK1 and CLK = 50 ps

Adjusted hold time = 200 + 50 = 250 ps

Hold Slack = (Path Delay) - (Adjusted Hold Time) = 200 - 250= -50 ps

$\Rightarrow$  FAIL (Hold slack should be  $\geq$  0)

ECE Department, University of Texas at Austin

Lecture 11. Sequential Elements

Jacob Abraham, October 6, 2020 35 /

35 / 36

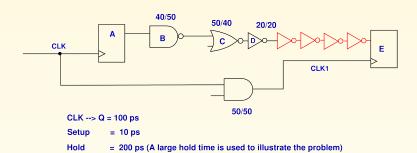

# Example: Fixing Hold-Time Violations, Cont'd

**Insert 4 inverters after D**, with each adding a 20 ps (or can insert one AND gate)

Long path (4 invs.) = 100 + 50 + 50 + 20 + 80 + 10 = 310 ps Now the minimum cycle time at which the path can operate = (Path Delay) - (CLK  $\rightarrow$  CLK1 Delay) = 310 - 50 = 260 ps

If possible, add the additional delay to fix hold time violations in the short path (without affecting the long paths)

ECE Department, University of Texas at Austin

ecture 11. Sequential Elements

acob Abraham, October 6, 2020 36 / 3