Jacob Abraham

Department of Electrical and Computer Engineering The University of Texas at Austin

> VLSI Design Fall 2020

October 8, 2020

ture 12. Dynamic CMOS Logic

Jacob Abraham, October 8, 2020 1 / 25

Jacob Abraham, October 8, 2020 1 / 25

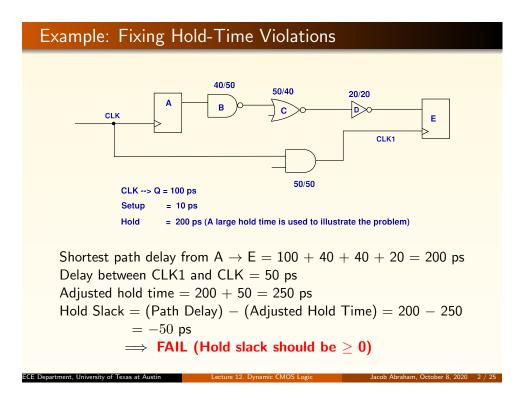

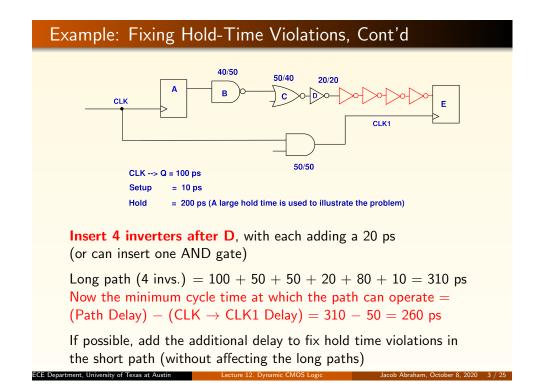

### **Review:** Fixing Hold-Time Violations

ECE Department, University of Texas at Austi

ECE Department, University of Texas at Austin

- Measure all hold times with respect to the main clock

- Adjust the hold time if the flop is receiving a delayed clock

- Compute the shortest path delay from the rising edge of the clock

Lecture 12. Dynamic CMOS Logic

• Check to see if there are any hold time failures

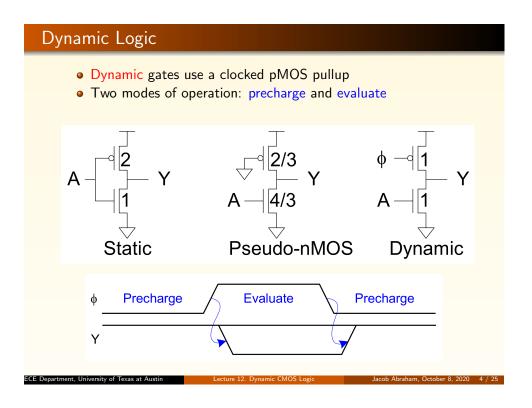

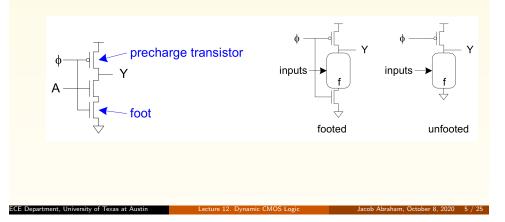

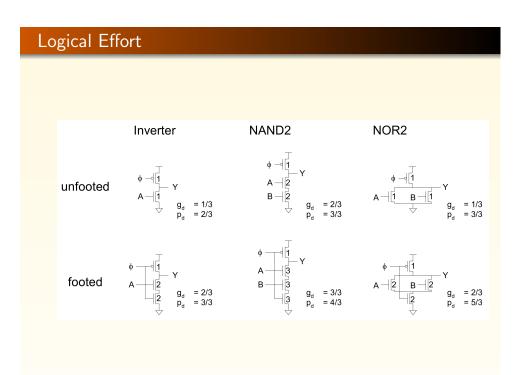

# The "Foot" Transistor What if pulldown network is ON during precharge? Use series evaluation transistor to prevent fight between pMOS and nMOS transistors

e 12. Dynamic CMOS Logi

Jacob Abraham, October 8, 2020 6 / 25

ECE Department, University of Texas at Austin

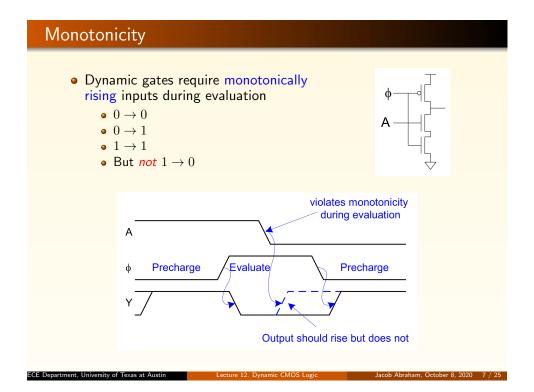

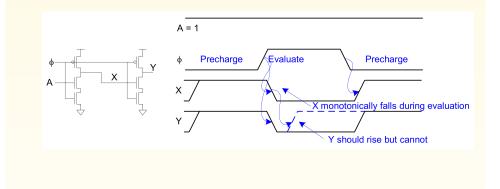

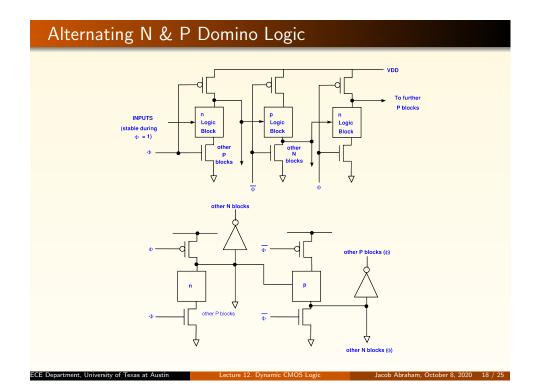

- But dynamic gates produce monotonically falling outputs during evaluation

- Illegal for one dynamic gate to drive another!

c CMOS L

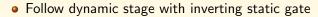

### **Domino Gates**

ECE Department, University of Texas at Au

- Dynamic/static pair is called domino gate

- Produces monotonic outputs

Jacob Abraham, October 8, 2020 8 / 25

### **Domino Optimizations**

- Each domino gate triggers next one, like a string of dominos toppling over

- Gates evaluate sequentially, precharge in parallel

- Evaluation is more critical than precharge

- HI-skewed static stages can perform logic

c CMOS I

Jacob Abraham, October 8, 2020 10 / 25

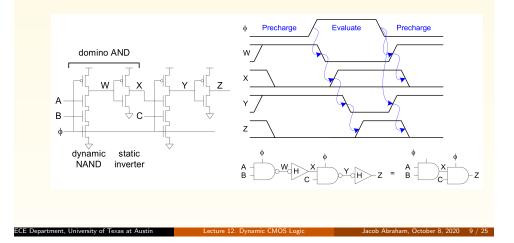

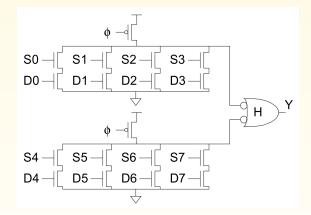

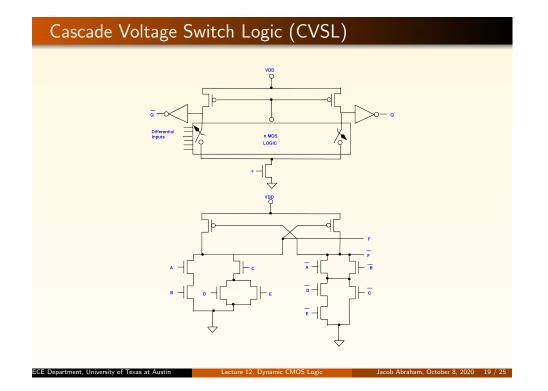

### Dual-Rail Domino

ECE Department, University of Texas at Au

- Domino only performs noninverting functions:

AND, OR but not NAND, NOR, or XOR

- Dual-rail domino solves this problem

- Takes true and complementary inputs

- Produces true and complementary outputs

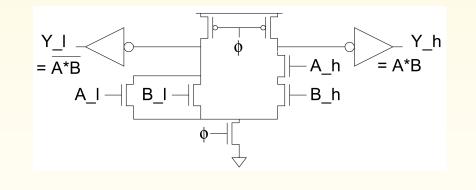

### Example: AND/NAND

- Given A\_h, A\_l, B\_h, B\_l

- Compute  $Y_h = A * B$ ,  $Y_l = \sim (A * B)$

- Pulldown networks are conduction complements

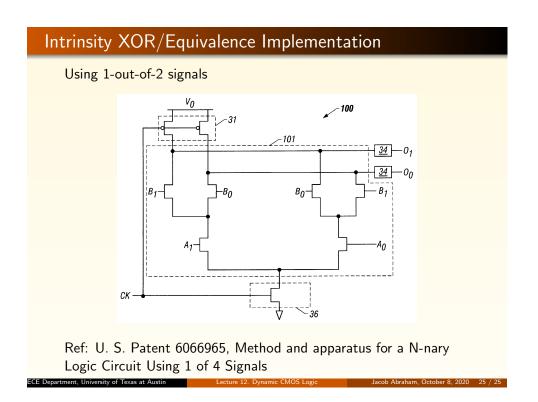

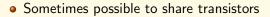

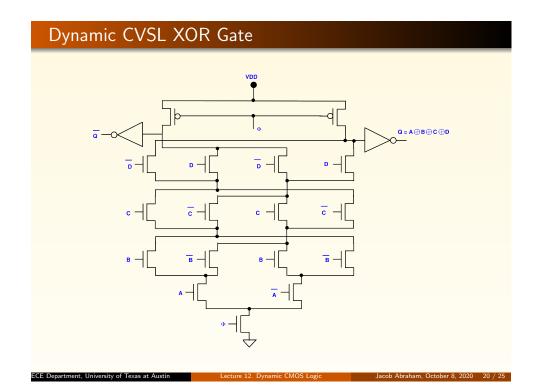

# Example: XOR/XNOR

ECE Department, University of Texas at A

• Sharing works well in implementations of symmetric functions

c CMOS L

Jacob Abraham, October 8, 2020 12 / 25

• See papers on "relay logic" published over 50 years ago

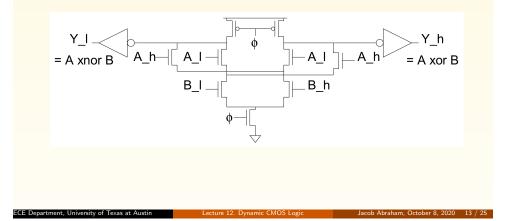

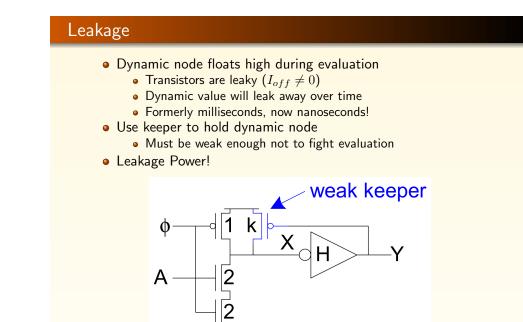

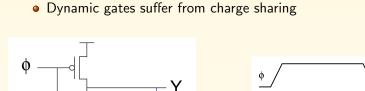

# Charge Sharing

ECE Department, University of Texas at Austin

ECE Department, University of Texas at Austi

b Abraham, October 8, 2020 14 / 25

Jacob Abraham, October 8, 2020 15 / 25

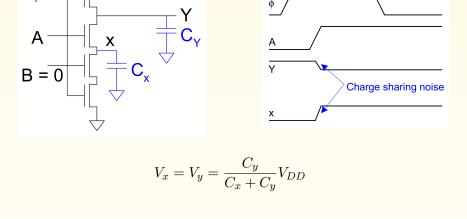

### Secondary Precharge

ECE Department, University of Texas at Austi

- Solution: add secondary precharge transistors

Typically need to precharge every other node

- Big load capacitance on Y helps as well

Abraham, October 8, 2020 16 / 25

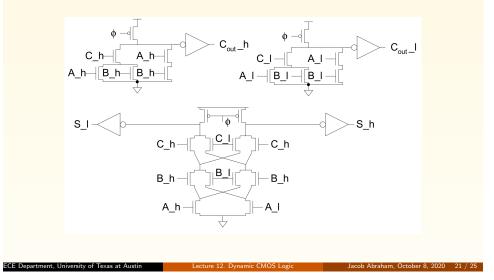

### Dual-Rail Domino Full Adder Design

- Very fast, but large and power hungry

- Used in very fast multipliers

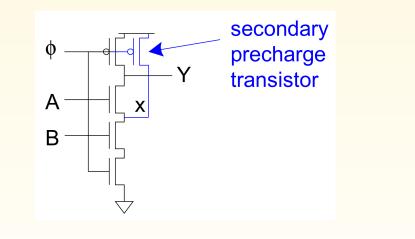

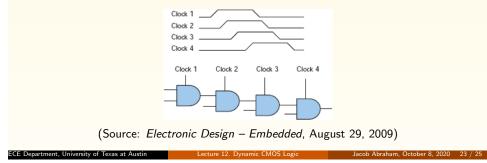

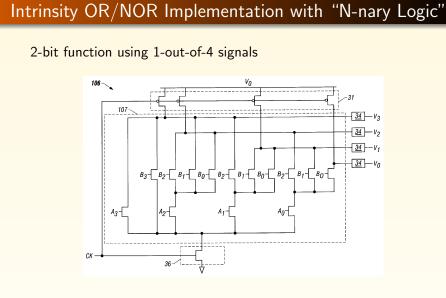

# Domino Logic in Current Designs

- Domino design from Intrinsity used in 1-GHz 0.75W ARM Cortex A8 from Samsung (Intrinsity later acquired by Apple)

- Fast Domino (called "Fast14 NDL") gates are inserted selectively into critical speed paths, with custom SRAMs and optimized synthesized logic elsewhere

- Standard power saving techniques are also used

- Domino gates are clocked by multiphase clocks

- A type of "super-pipeline" where the domino footers form the barrier for the pipeline operation

Ref: U. S. Patent 6066965, Method and apparatus for a N-nary Logic Circuit Using 1 of 4 Signals

Jacob Abraham, October 8, 2020 24 / 25

ECE Department, University of Texas at Austi