# 15. Nanoscale Design Issues

Jacob Abraham

Department of Electrical and Computer Engineering

The University of Texas at Austin

VLSI Design Fall 2020

October 20, 2020

ECE Department, University of Texas at Austin

Lecture 15. Nanoscale Design Issues

Jacob Abraham, October 20, 2020 1 /

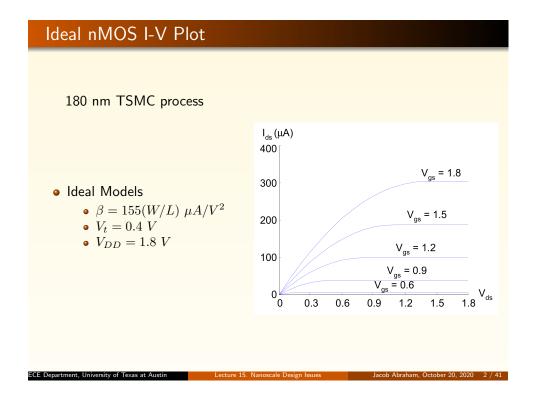

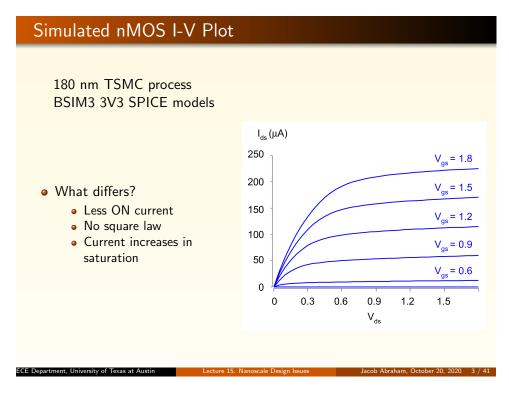

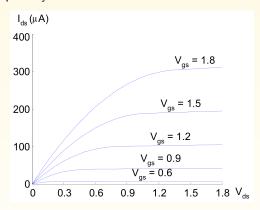

# Ideal Transistor I-V

Shockley first-order transistor models

$$I_{ds} = \begin{cases} 0 & V_{gs} < V_t & \text{cutoff} \\ \beta \left(V_{gs} - V_t - \frac{V_{ds}}{2}\right) V_{ds} & V_{ds} < V_{dsat} & \text{linear} \\ \frac{\beta}{2} (V_{gs} - V_t)^2 & V_{ds} > V_{dsat} & \text{saturation} \end{cases}$$

ECE Department, University of Texas at Austin

Lecture 15. Nanoscale Design Issues

Jacob Abraham, October 20, 2020

1 / 41

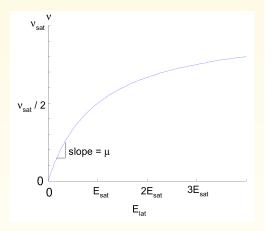

# **Velocity Saturation**

- ullet We assumed carrier velocity  $\propto$  E-field

- $\nu = \mu E_{lat} = \mu V_{ds}/L$

- Carriers scatter off atoms

- ullet Velocity reaches  $u_{sat}$

- Electrons:  $6 10 \times 10^6$  cm/s

- Holes:  $4 8 \times 10^6 \text{ cm/s}$

- Better model

$$\nu = \frac{\mu E_{lat}}{1 + \frac{E_{lat}}{E_{sat}}} \implies \nu_{sat} = \mu E_{sat}$$

ECE Department, University of Texas at Austin

Lecture 15. Nanoscale Design Issues

cob Abraham, October 20, 2020 4 / 41

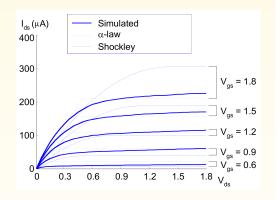

# Velocity Saturation I-V Effect

$\bullet$  Ideal transistor ON current increases with  ${\cal V}^2_{DD}$

$$I_{ds} = \mu C_{ox} \frac{W}{L} \frac{(V_{gs} - V_t)^2}{2} = \frac{\beta}{2} (V_{gs} - V_t)^2$$

$\bullet$  Velocity-saturated ON current increases with  $V_{DD}$

$$I_{ds} = C_{ox}W(V_{gs} - V_t)\nu_{max}$$

- Real transistors are partially velocity saturated

- ullet Approximate with lpha-power law model

$$I_{ds} \propto V_{DD}^{\alpha}$$

•  $1 < \alpha < 2$  determined empirically

CE Department, University of Texas at Austin

Lecture 15. Nanoscale Design Issues

Jacob Abraham, October 20, 2020 5

5 / 41

# $\alpha$ -Power Model

$$I_{ds} = \begin{cases} 0 & V_{gs} < V_t & \text{cutoff} \\ I_{dsat} \frac{V_{ds}}{V_{dsat}} & V_{ds} < V_{dsat} & \text{linear} \\ I_{dsat} & V_{ds} > V_{dsat} & \text{saturation} \end{cases}$$

$$I_{dsat} = P_c \frac{\beta}{2} (V_{gs} - V_t)^{\alpha}$$

$$V_{dsat} = P_{\nu}(V_{gs} - V_t)^{\alpha/2}$$

$\alpha$ ,  $\beta$ ,  $P_c$  and  $P_{\nu}$  are parameters determined empirically from a curve-fit of I-V characteristics

ECE Department, University of Texas at Austin

Lecture 15. Nanoscale Design Issues

cob Abraham, October 20, 2020 6 / 41

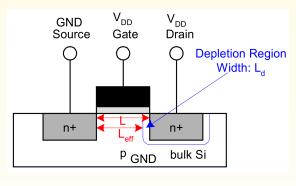

# **Channel Length Modulation**

- Reverse-biased p-n junctions form a depletion region

- Region between n and p with no carriers

- ullet Width of depletion  $L_d$  region grows with reverse bias

- $L_{eff} = L L_d$

- ullet Shorter  $L_{eff}=$  more current

- ullet  $I_{ds}$  increases with  $V_{ds}$

- Even in saturation

ECE Department, University of Texas at Austi

Lecture 15. Nanoscale Design Issues

Jacob Abraham, October 20, 2020 7

7 / 41

# Channel Length Modulation I-V

$$I_{ds} = \frac{\beta}{2}(V_{gs} - V_t)^2 (1 + \lambda V_{ds})$$

$\lambda$  = channel length modulation coefficient

- Not feature size

- Empirically fit to I-V characteristics

# **Body Effect**

- ullet  $V_t$ : gate voltage necessary to invert channel

- Increases if source voltage increases because source is connected to the channel

- Increase in  $V_t$  with  $V_s$  is called the body effect

# Body Effect Model

$$V_t = V_{t0} + \gamma \left( \sqrt{\phi_s + V_{sb}} - \sqrt{\phi_s} \right)$$

$\phi_s = {\sf surface} \ {\sf potential} \ {\sf at} \ {\sf threshold}$

$$\phi_s = 2\nu_T \ln(\frac{N_A}{n_i})$$

• Depends on doping level  $N_A$

- As well as intrinsic carrier concentration  $n_i$

$\gamma = \text{body effect coefficient}$

$$\gamma = \frac{t_{ox}}{\epsilon_{ox}} \sqrt{2q\epsilon_{Si}N_A} = \frac{\sqrt{2q\epsilon_{Si}N_A}}{C_{ox}}$$

# **OFF Transistor Behavior**

- What about current in cutoff?

- Simulated results don't match measurements

- What differs?

- Current doesn't go to 0 in cutoff

ECE Department, University of Texas at Austin

Lecture 15. Nanoscale Design Issues

cob Abraham. October 20, 2020 10 /

### 10 / 41

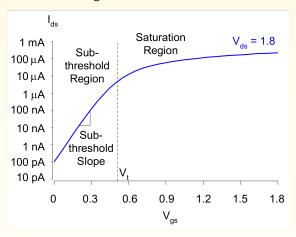

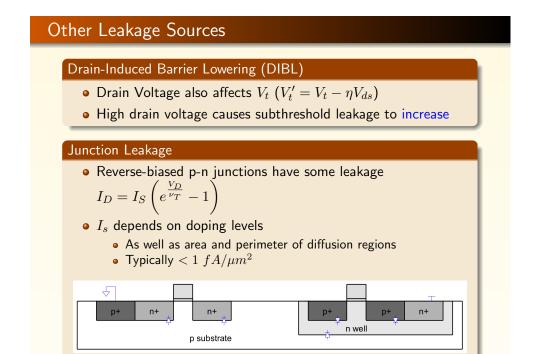

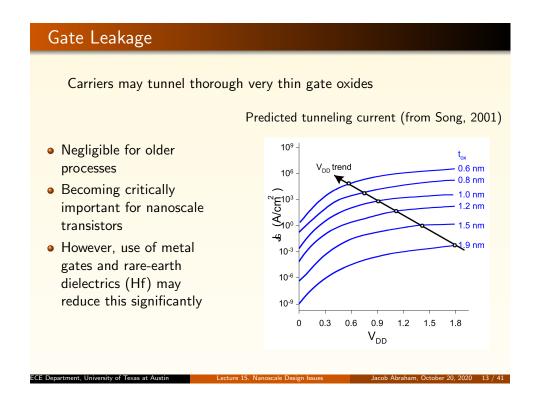

# Leakage Sources

- Subthreshold conduction

- Transistors can't abruptly turn ON or OFF

- Junction leakage

- Reverse-biased PN junction diode current

- Gate leakage

- Tunneling through ultrathin gate dielectric

- Subthreshold leakage is the biggest source of leakage in modern transistors

# Subthreshold Leakage

ullet Subthreshold leakage is exponential with  $V_{qs}$

$$I_{ds} = I_{ds0}e^{\frac{V_{gs} - V_t}{n\nu_T}} \left(1 - e^{\frac{-V_{ds}}{\nu_T}}\right), \quad I_{ds0} = \beta\nu_T^2 e^{1.8}$$

n is process dependent, typically 1.4 − 1.5

ECE Department, University of Texas at Austin

Lecture 15. Nanoscale Design Issues

Jacob Abraham, October 20, 2020 11 / 4

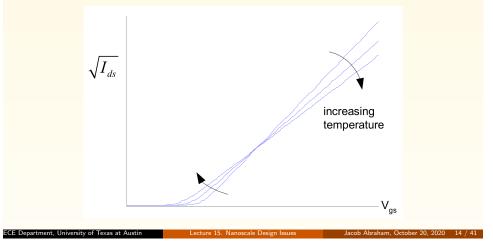

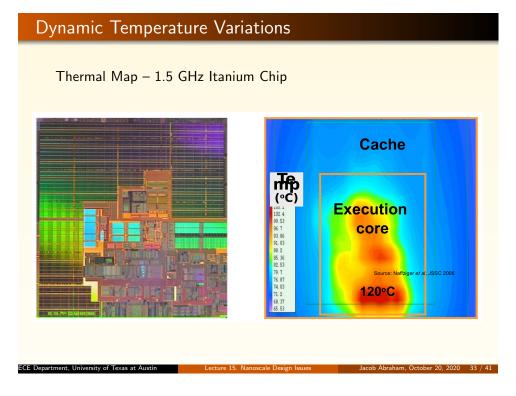

# Temperature Sensitivity

- Increasing temperature

- Reduces mobility

- ullet Reduces  $V_t$

- ullet  $I_{ON}$  decreases with temperature

- ullet  $I_{OFF}$  increases with temperature

# So What?

- So what if transistors are not ideal?

- They still behave like switches, and isn't that enough for digital logic?

- But these effects matter for . . .

- Supply voltage choice

- Logical effort

- Quiescent power consumption

- Pass transistors

- Temperature of operation

ECE Department, University of Texas at Austin

Lecture 15. Nanoscale Design Issues

lacob Abraham, October 20, 2020 15 /

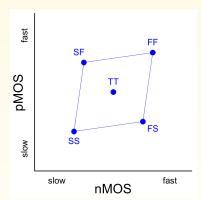

# Parameter Variations

- Transistors have uncertainty in parameters

- ullet Process:  $L_{eff}$ ,  $V_t$ ,  $t_{ox}$  of nMOS and pMOS

- Vary around typical (T) values

- Fast (F)

- $L_{eff}$ : short

- ullet  $V_t$ : low

- $t_{ox}$ : thin

- Slow (S): opposite

Not all parameters are independent for nMOS and pMOS

# **Environmental Variation**

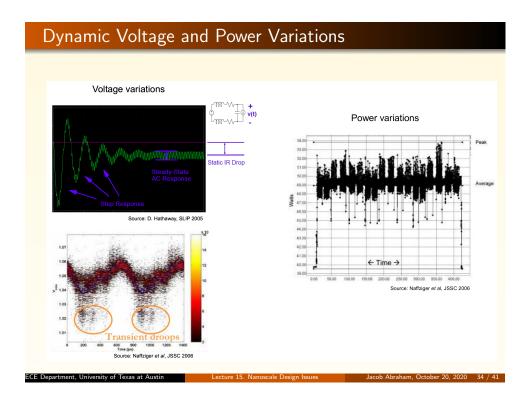

- ullet  $V_{DD}$  and Temperature also vary in time and space

- Fast:

- $\bullet$   $V_{DD}$ : high

- Temperature: low

| Corner | Voltage | Temperature |

|--------|---------|-------------|

| F      | 1.98    | 0°C         |

| Т      | 1.8     | 70°C        |

| S      | 1.62    | 125°C       |

# **Process Corners**

- Process corners describe worst case variations

- If a design works in all corners, it will probably work for any

- Describe corner with four letters (T, F, S)

- nMOS speed

- pMOS speed

- Voltage

- Temperature

# Important Corners

Some critical simulation corners include

| Purpose              | nMOS | pMOS | $V_{DD}$ | Temp |

|----------------------|------|------|----------|------|

| Cycle time           | S    | S    | S        | S    |

| Power                | F    | F    | F        | F    |

| Subthreshold leakage | F    | F    | F        | S    |

| Pseudo-nMOS          | S    | F    | ?        | ?    |

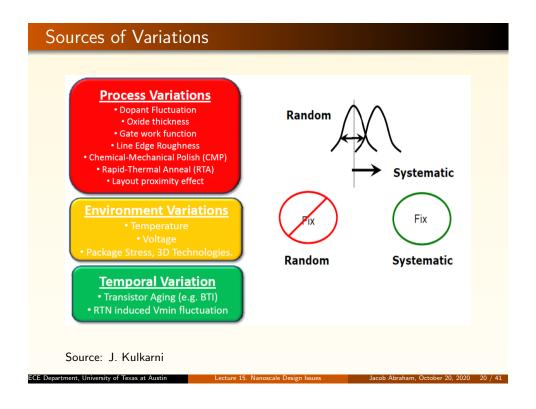

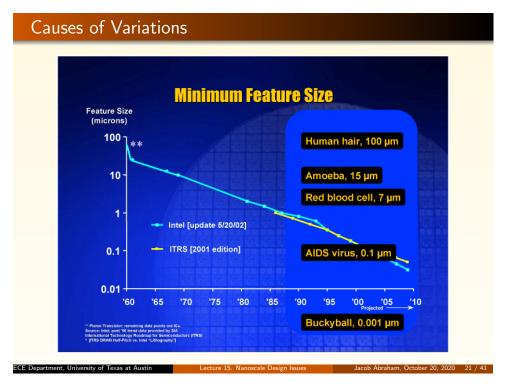

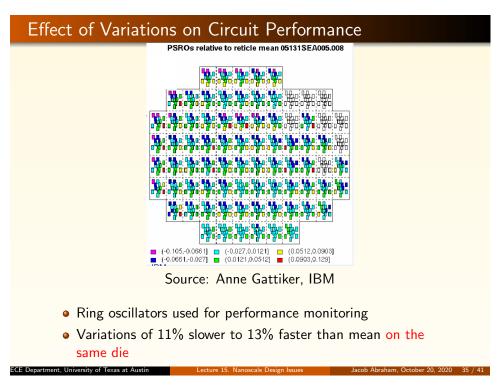

# Variability

- Variability: Statistical relationship between design parameters and process parameters

- Need the ability to accurately model the relationship and incorporate the behavior into simulation tools

- Possible to compensate for the variability

- Example:  $L_{eff}$ ,  $V_t$

- Conductor thickness as a function of interconnect density

- Modeling deficiencies may make variability look like uncertainty

- Example: circuit switching activity factor

ECE Department, University of Texas at Austin

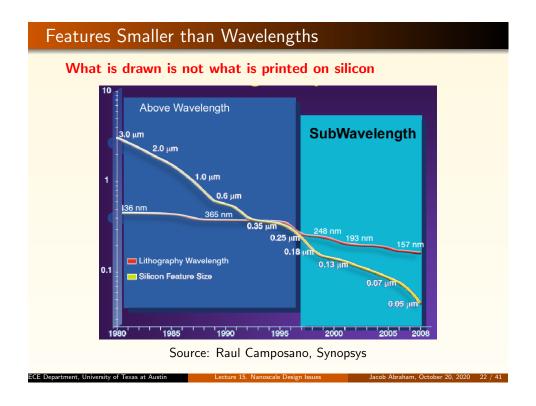

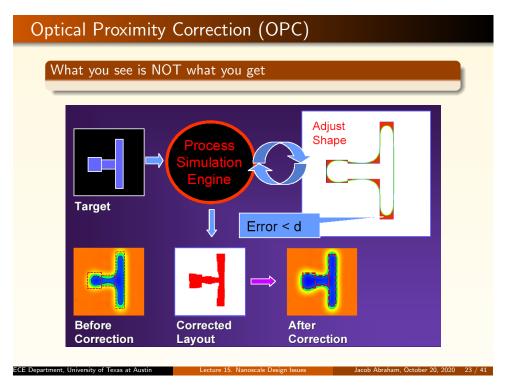

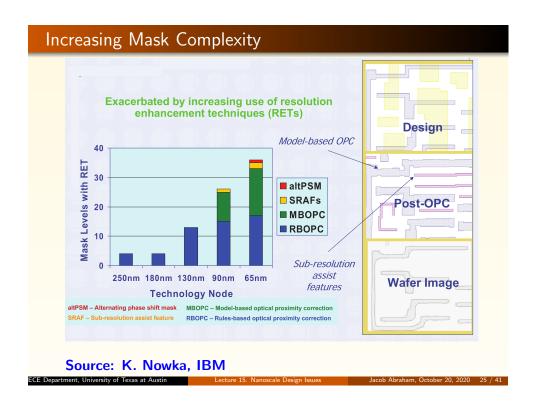

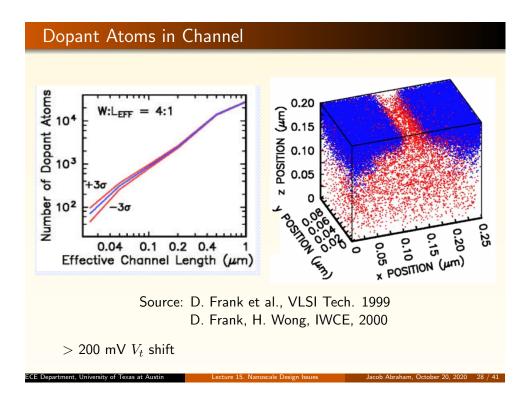

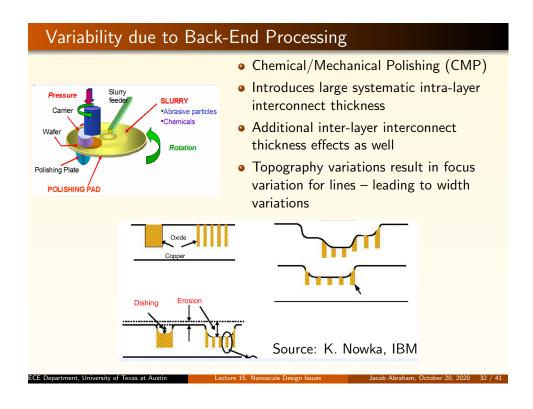

# Imperfect Process Control • Neighboring shapes interfere with the desired shape at some location: results in pattern sensitivity • This is predominantly in the same plane • There will be some interference from buried features for interconnect Source: T. Brunner, ICP 2003

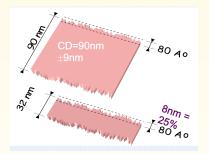

# Line Edge Roughness

- In the lithography process, dose of photons will fluctuate due to finite quanta

- Shot noise

- There will be fluctuations in the photon absorption positions

- Due to nanoscale impurities in the resist composition

- Poly lines subject to increasing line edge roughness (LER)

- Impact: circuit delay and leakage power

ECE Department, University of Texas at Austin

Lecture 15. Nanoscale Design Issues

ob Abraham. October 20, 2020 26 / 41

# Other Sources of Variability

N. Rohrer, ISSCC 2006

- Negative Bias Temperature Instability (NBTI)

- ullet At high negative bias and elevated temperature, the p-MOS  $V_t$ gradually becomes more and more negative - reducing p-channel current

- Mechanism thought to be the breakdown of H-Si bonds at the Si/SiO<sub>2</sub> interface, creating surface traps and injecting positive H-related species into the oxide

- Associated with the average NBTI shift, there are also random shifts - even identical use conditions result in mismatch shifts, due to random variations in the number and spatial distribution of the charges/interface states formed

- Charge trapping and hot-carrier defect generation mechanisms

- ullet Result in long-term  $V_t$  shifts in both n- and p-channel devices

- ullet The long-term  $V_t$  shifts are parameter variations which must be accounted for during circuit design

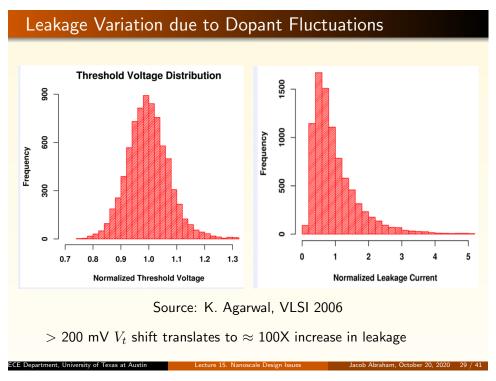

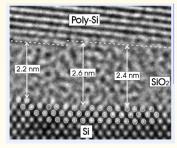

# Fluctuation in Gate Oxide Thickness

- Gate oxide variations have an exponential effect on gate tunneling currents

- ullet Impact on device threshold, but significantly less  $V_t$  variation than due to random dopant fluctuations

- Recent advances in high-k gate dielectrics (Hafnium oxides) with metal gates have alleviated this problem

1.1 nm oxide:  $\approx$  6 atomic layers

Gate tunneling current

Source: K. Nowka, IBM

Source: Kevin Nowka, IBM

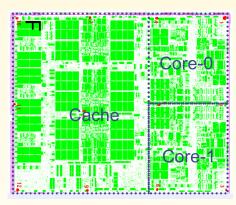

- Multicore chip from IBM

- $\bullet$  Core-0 was found to be  $\approx$  15% slower than other parts

- Models predicted that all parts of the design are identical

ECE Department, University of Texas at Austin

Lecture 15. Nanoscale Design Issues

ob Abraham. October 20, 2020 36 / 41

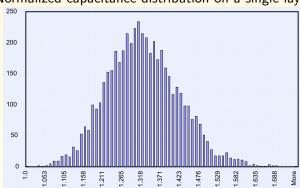

# Variation in Other Circuit Elements

Normalized capacitance distribution on a single layer

Source: C. Visweswariah

- This enormous variation has a significant impact on analog/RF design

- Industry "sweet spots" for analog design are  $0.25\mu 0/18\mu$

- High frequency RF designs forced to use much smaller dimensions

CE Department, University of Texas at Austi

Lecture 15. Nanoscale Design Issues

Jacob Abraham, October 20, 2020 37 /

| Delay Impact of Variations                                                        |                                         |  |  |  |

|-----------------------------------------------------------------------------------|-----------------------------------------|--|--|--|

| Parameter                                                                         | Delay Impact                            |  |  |  |

| BEOL metal                                                                        | -10% → +25%                             |  |  |  |

| (Metal mistrack, thin/thick wires))                                               |                                         |  |  |  |

| Environmental                                                                     | $\pm$ 15%                               |  |  |  |

| (Voltage islands, IR drop, temperature)                                           |                                         |  |  |  |

| Device fatigue (NBTI, hot electron effects)                                       | ± 10%                                   |  |  |  |

| $V_t$ and $T_{ox}$ device family tracking                                         | ± <b>5%</b>                             |  |  |  |

| (Can have multiple $V_t$ and $T_{ox}$ device families)                            |                                         |  |  |  |

| Model/hardware uncertainty                                                        | ± 5%                                    |  |  |  |

| (Per cell type)                                                                   |                                         |  |  |  |

| N/P mistrack                                                                      | $\pm$ 10%                               |  |  |  |

| (Fast rise/slow fall, fast fall/slow rise)                                        |                                         |  |  |  |

| PLL/Clock Tree                                                                    | ± 10%                                   |  |  |  |

| (Jitter, duty cycle, phase error)                                                 |                                         |  |  |  |

| Requires $2^{20}$ timing runs or [-65 $\%$ , $+80\%$ ] guard band                 |                                         |  |  |  |

| Source: K. Kalafala, C. Visweswariah                                              |                                         |  |  |  |

| ECE Department, University of Texas at Austin Lecture 15. Nanoscale Design Issues | Jacob Abraham, October 20, 2020 38 / 41 |  |  |  |