## 2. Transistors, Fabrication, Layout

#### Jacob Abraham

#### Department of Electrical and Computer Engineering The University of Texas at Austin

VLSI Design Fall 2020

September 1, 2020

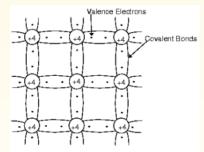

## Conductivity in Silicon Lattice

#### Look at the behavior of crystalline silicon

- At temperatures close to 0 K, electrons in outermost shell tightly bound (insulator)

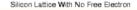

- At higher temps., (300 K), some electrons have thermal energy to break covalent bonds

Silicon Lattice With One Covalent Bond Broken

## The Elements (Periodic Table)

| H <sup>3</sup><br>Li <sup>3</sup><br>Na | Be<br>12<br>Mg      |                    |                      |                 |                  |            | B <sup>5</sup><br>AI | C <sup>6</sup><br>14<br>Si | N<br>15<br>P | 0 <sup>8</sup><br>S <sup>16</sup> | 9<br>F<br>CI         | He<br>10<br>Ne<br>18<br>Ar |                  |           |                       |                       |                  |

|-----------------------------------------|---------------------|--------------------|----------------------|-----------------|------------------|------------|----------------------|----------------------------|--------------|-----------------------------------|----------------------|----------------------------|------------------|-----------|-----------------------|-----------------------|------------------|

| 19<br>K                                 | Ca <sup>20</sup>    | SC <sup>21</sup>   | Ti<br>Ti             | V <sup>23</sup> | Cr <sup>24</sup> | 25<br>Mn   | Fe <sup>26</sup>     | C0                         | 28<br>Ni     | Cu<br>Cu                          | Zn<br>Zn             | Ga <sup>31</sup>           | Ge <sup>32</sup> | As        | 34<br>Se              | 35<br>Br              | 36<br>Kr         |

| 37<br>Rb                                | 38<br>Sr            | <sup>39</sup><br>Y | <sup>40</sup><br>Zr  | 41<br>Nb        | 42<br>Mo         | 43<br>TC   | 44<br>Ru             | Rh                         | 46<br>Pd     | 47<br>Ag                          | Cd <sup>48</sup>     | 49<br>In                   | 50<br>Sn         | Sb        | Te <sup>52</sup>      | 53<br>                | Xe <sup>54</sup> |

| Cs                                      | Ba                  | 57<br>La           | 72<br>Hf             | 73<br>Ta        | W <sup>74</sup>  | 75<br>Re   | 76<br>Os             | 77<br>Ir                   | Pt           | <sup>79</sup><br>Au               | Hg                   | 81<br>Ti                   | Pb               | Bi<br>Bi  | 84<br>Po              | At 85                 | 86<br>Rn         |

| 87<br>Fr                                | <sup>88</sup><br>Ra | AC                 | Unq                  | Unp             | Unh              | 107<br>Uns | 108<br>Uno           | Une                        | Unn          |                                   |                      |                            |                  |           |                       |                       |                  |

|                                         |                     |                    | 58<br>Ce<br>90<br>Th | Pr              | 60<br>Nd         | Pm         | 62<br>Sm<br>94<br>Pu | Eu<br>95                   | Gd           | 65<br>Tb<br>97<br>Bk              | 66<br>Dy<br>98<br>Cf | 67<br>Ho<br>99<br>Es       | Er               | Tm<br>101 | 70<br>Yb<br>102<br>No | 71<br>Lu<br>103<br>Lr |                  |

## Build Systems with Information on Electrical Characteristics of Building Blocks (Transistors)

This course will not cover semiconductor physics

- Learn this from other courses in the department

- We will design VLSI circuits knowing the electrical behavior of the transistors

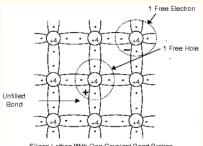

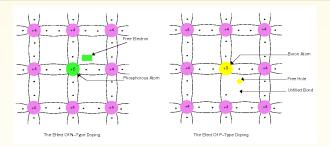

## Dopants

#### Used to selectively change the conductivity of silicon

- Silicon is a semiconductor

- Pure silicon has no free carriers and conducts poorly

- Adding dopants **impurities** to pure silicon increases the conductivity

- Group V: extra electron (n-type)

- Group III: missing electron, called hole (p-type)

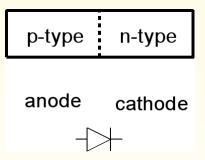

#### Diodes

- A junction between p-type and n-type semiconductor forms a diode

- Current flows only in one direction

## p-n Junction, Cont'd

Source: Prof. Dr. Helmut Föll, University of Kiel

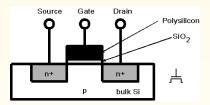

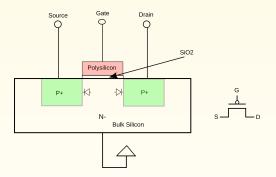

## nMOS Transistor

#### Four-Terminal device: gate, source, drain, body

- Gate oxide body stack looks like a capacitor

- Gate and body are conductors

- $SiO_2$  (oxide) is a very good insulator

- Called metal oxide semiconductor (MOS) capacitor, even though gate material changed to polysilicon

- Recent gate material in nanoscale processes is back to metal

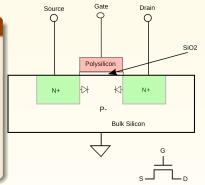

## nMOS Transistor Operation

Body (bulk) is commonly tied to Ground (0 V)

#### When the gate is at a low voltage

- P-type body is at low voltage

- Source-body and drain-body diodes are OFF

- No current flows, transistor is OFF

#### When the gate is at a high voltage

- Positive charge on gate of MOS capacitor

- Negative charge attracted to body

- Inverts a channel under gate to n-type

- Now electrons can flow through n-type silicon from source through channel to drain, transistor is ON

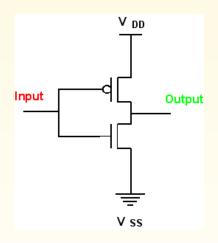

## pMOS Transistor

#### Similar to nMOS transistor, but doping and voltages reversed

- Body tied to high voltage (VDD)

- Gate low: transistor ON

- Gate high: transistor OFF

- Bubble indicates inverted behavior

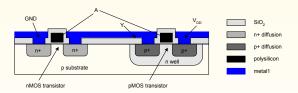

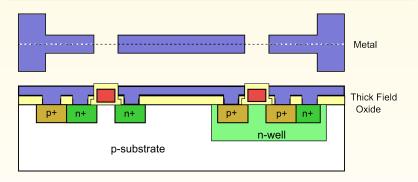

## **CMOS** Fabrication

#### Silicon technology

- CMOS transistors are fabricated on silicon wafer

- Lithography process similar to printing press

- On each step, different materials are deposited or etched

- Easiest to understand by viewing both top and cross-section of wafer in a simplified manufacturing process

#### Example inverter cross-section

- Typically use p-type substrate for nMOS transistors

- Requires n-well for body of pMOS transistors

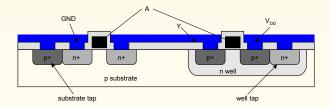

## Well and Substrate Taps

#### Substrate contacts are critical to correct operation of CMOS

- Substrate must be tied to GND, n-well to VDD (reverse-biased diodes isolate regions)

- Metal to lightly-doped semiconductor forms poor connection called Schottky Diode – use heavily doped well and substrate contacts/taps

## Inverter Masks

- Transistors and wires are defined by masks

- Cross-sections shown above taken along dashed line

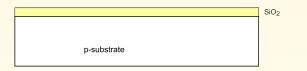

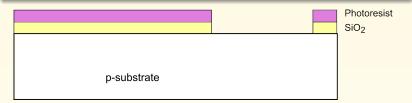

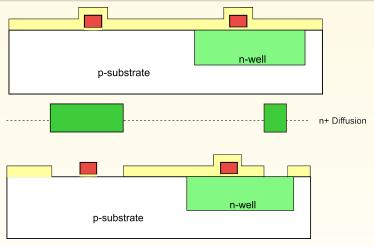

## **Examples of Fabrication Steps**

A VERY simplified description illustrating the major step – modern processes follow these basic steps, but are much more complex

- Start with blank wafer

- Build inverter from the bottom up

#### First step is to form the n-well

- Cover wafer with protective layer of  $SiO_2$  (oxide)

- Remove layer where n-well should be built

- Implant or diffuse n dopants into exposed wafer

- Strip off  $SiO_2$

p-substrate

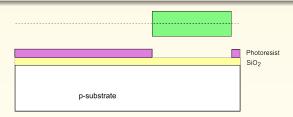

## Oxidation and Photoresist

#### Grow $SiO_2$ on top of Si wafer

•  $900 - 1200^{\circ}$ C with  $H_2O$  or  $O_2$  in oxidation furnace

#### Spin-on photoresist

• Photoresist is a light-sensitive organic polymer which softens where exposed to light (positive resist)

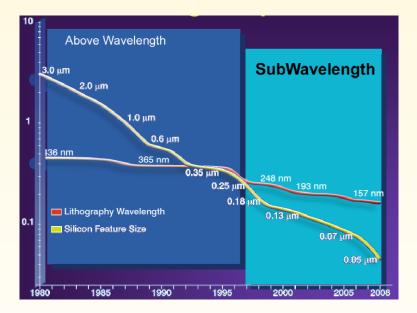

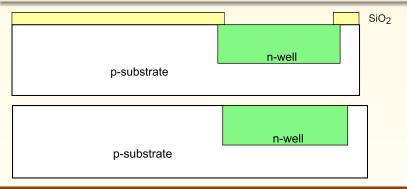

## Lithography

#### Use light to transfer a pattern to the wafer

- Expose photoresist through n-well mask (using UV light example 193 nm wavelength)

- "Immersion lithography" used in some nanoscale processes

- Strip off exposed photoresist

#### Interesting physics problem

- How can we "print" a 45 nm feature using light with a wavelength of 193 nm?

- Significant distortion of the image!

ECE Department, University of Texas at Austin

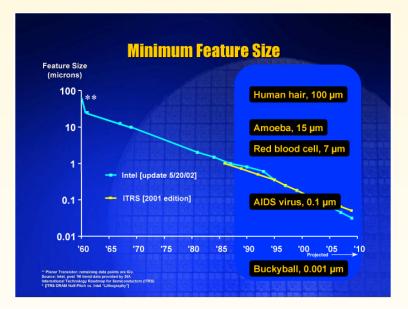

## Trend in Integrated Circuit Feature Sizes

ECE Department, University of Texas at Austin

## Features Smaller than Wavelength of Light Used

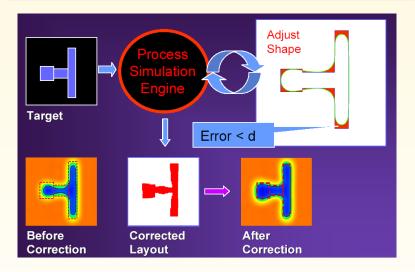

## **Optical Proximity Correction (OPC)**

#### What you see is NOT what you get

## Etch and Strip Photoresist

#### Etch oxide with Hydrofluoric acid (HF)

• Only attacks oxide where resist has been exposed

# Strip remaining photoresist using mixture of acids ("piranha" etch)Necessary so resist does not melt in the next step

|             | SiO <sub>2</sub> |

|-------------|------------------|

|             |                  |

| p-substrate |                  |

|             |                  |

## n-Well

#### Formed using ion implant (used to be diffusion)

- Bombard wafer with As ions, which only enter exposed Si

- (With diffusion, wafer is placed in a furnace with As gas)

- Remaining oxide is then stripped off using HF, and it is back to the bare wafer, but with an n-well

#### Subsequent steps repeat the above process

ECE Department, University of Texas at Austin

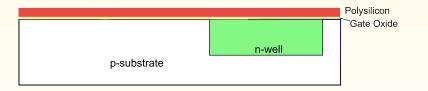

## Polysilicon (Modern Processes use Metal Gates)

#### Very thin layer of gate oxide is grown on wafer

- Gate oxide thickness is < 20Å (few atomic layers)

- One of the most critical steps in fabrication process

#### Polysilicon deposited on top of gate oxide

- Grown using Chemical vapor deposition (CVD)

- Wafer placed in furnace with Silane (SiH) gas

- Small crystals (polysilicon) formed on wafer

- Heavily doped to be a good conductor

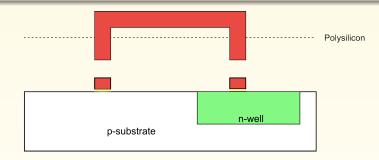

## Polysilicon Patterning

Use same lithography processing to pattern polysilicon

- Reactive Ion Etch (RIE) process

- Charge buildup on un-etched polysilicon can lead to "antenna effects" and damage gate oxide

# Self-aligned process Polysilicon "blocks" dopants where the channel should be formed ECE Department, University of Texas at Austin Lecture 2, Transistors, Fabrication, Lavout Jacob Abraham, September 1, 2020 22

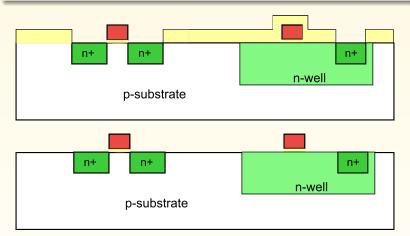

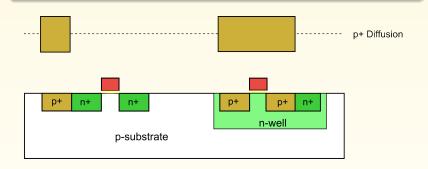

## N+ Diffusion

#### nMOS transistors are formed

- $\bullet$  Oxide is patterned to form the n+ regions

- N+ diffusion forms nMOS source, drain, and n-well contact

ECE Department, University of Texas at Austin

## N+ Diffusion, Cont'd

#### Ion implantation used to dope silicon

- n+ regions are formed

- Oxide is stripped off to complete patterning step

A similar set of steps is used to form the p+ diffusion regions for the pMOS transistor source and drain as well as the substrate contact

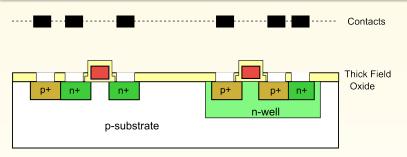

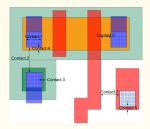

## Contacts

#### Points where the first level of metal contacts the transistors

- Used to wire the devices together

- Wafer is covered with thick field oxide

- Oxide is etched where the contact cuts are needed

## Metallization

#### Used to interconnect internal nodes

- Aluminum was the traditional metal

- Switch to Copper for high performance processes

- Aluminum is sputtered over the entire wafer

- Patterned to remove excess metal, leaving the wires

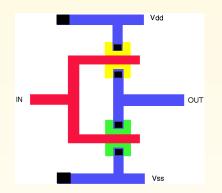

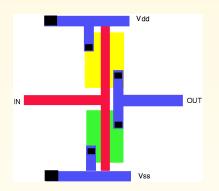

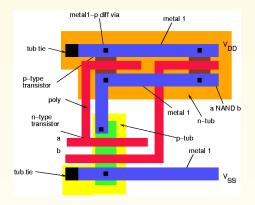

### Layout

- Describes actual layers and geometry on the silicon substrate to implement a function

- Need to define transistors, interconnection

- Transistor widths (for performance)

- Spacing, interconnect widths, to reduce defects, satisfy power requirements

- Contacts (between poly or active and metal), and vias (between metal layers)

- Wells and their contacts (to power or ground)

- Layout of lower-level cells constrained by higher-level requirements: **floorplanning**

- "design iteration"

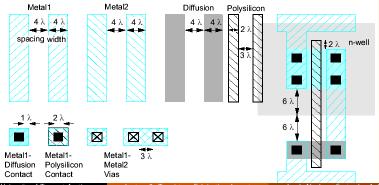

## Layout, Cont'd

- Chips are specified with set of masks

- Minimum dimensions of masks determine transistor size (and hence speed, cost, and power)

- Feature size f = distance between source and drain

- Set by minimum width of polysilicon (= minimum "drawn" gate length)

- Feature size improves 30% every 3 years or so

- Normalize for feature size when describing design rules

- Express rules in terms of  $\lambda = f/2$

- e.g.,  $\lambda=$  0.3 $\mu m$  in 0.6 $\mu m$  process

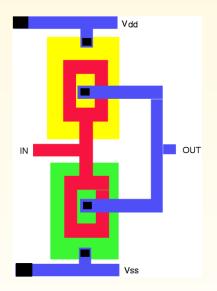

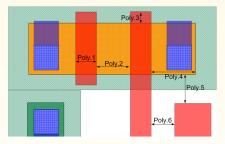

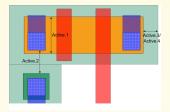

## **CMOS** Inverter Layout

Note: the N- and P- well are not shown in the layout

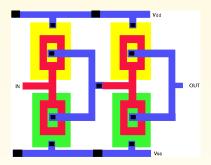

## Other CMOS Layouts

#### Using wide transistors

#### Using even wider transistors

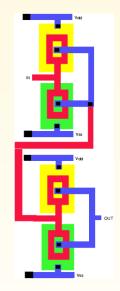

## Buffer with Two Inverters

#### Side by side

#### Stacked

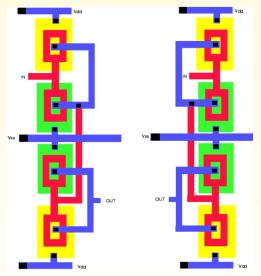

## Improving Layout Efficiency

"Flip" a cell so that power (or ground) can be shared with another cell  $% \left( {{{\left[ {{{C_{{\rm{B}}}} \right]}} \right]_{{\rm{C}}}}} \right)$

Stick diagrams identify actual layers (which a schematic does not); both can be annotated with transistor sizes

#### n- and p-wells are shown

## Simplified Design Rules

Based on  $\lambda$  (popular in academia)

Discussed in the textbook

Rules based on  $\lambda$  can theoretically be migrated to a different technology (by changing the value of  $\lambda$ ); in practice, all the rules do not scale in the same way, and industry typically does not use  $\lambda$  rules

ECE Department, University of Texas at Austin

Lecture 2. Transistors, Fabrication, Layout

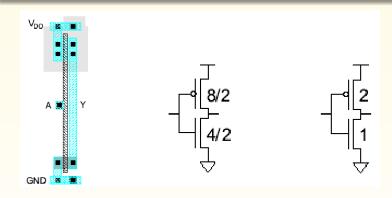

## Inverter Layout

#### Dimensions of pMOS and nMOS transistors

- Dimensions specified as Width/Length  $\left(\frac{W}{L}\right)$

- $\bullet\,$  Minimum size,  $4\lambda/2\lambda$  , sometimes called unit-size transistor

- (pMOS transistors are typically designed to be about twice the width of nMOS transistors, because of the mobilities of holes and electrons)

## The MOSIS Scalable CMOS Rules

# MOSIS is a prototyping and small-volume production service for VLSI circuit development

- MOSIS keeps costs down by combining many designs on a single die (multi-project chips)

- Similar facilities exist in Europe (Europractice, CMP), Taiwan, etc.

- $\lambda$ -based rules

- Designs using these rules are fabricated by a variety of companies

- Support for submicron digital CMOS, analog (buried poly layer for capacitor), micromachines, etc.

- https://www.mosis.com/files/scmos/scmos.pdf

## Nangate 45nm Open Cell Library

#### Used in the laboratory exercises

- This is an open-source, standard-cell library

- To aid university research programs and other organizations in developing design flows, designing circuits and exercising new algorithms

- Link to the wiki: http://www.eda.ncsu.edu/wiki/FreePDK45:Contents

- Example: poly rules (note: summarized here)

| Rule | Value  | Description     |

|------|--------|-----------------|

| 1    | 50 nm  | Minimum width   |

| 2    | 140 nm | Minimum spacing |

| 3    | 55 nm  | Min. extension  |

| 4    | 70 nm  | Min. enclosure  |

| 5    | 50 nm  | Min. spacing    |

| 6    | 75 nm  | Min. spacing    |

#### Active Rules

| Rule | Value | Description      |

|------|-------|------------------|

| 1    | 90 nm | Minimum width    |

| 2    | 80 nm | Minimum spacing  |

| 3    | -     | Min. well-active |

| 4    | -     | active inside    |

#### Contact Rules

| Rule    | Value | Description            |  |  |  |

|---------|-------|------------------------|--|--|--|

| 1 65 nm |       | Minimum width          |  |  |  |

| 2       | 75 nm | Minimum spacing        |  |  |  |

| 3       | -     | contact inside         |  |  |  |

| 4       | 5 nm  | Min. active around     |  |  |  |

| 5       | 5 nm  | Min. poly around       |  |  |  |

| 6       | 35 nm | Min. spacing with gate |  |  |  |

| 7       | 90 nm | Min. spacing with poly |  |  |  |

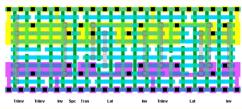

## Trend Towards Reducing Number of Rules

#### Improve manufacturability

- Less flexibility for designers

- Intel reduced the number of poly layout rules for logic layout in 45nm by 37% compared with the 65 nm process

- Highly regular layout greatly reduces lithographic distortions

- Limit rules, thereby limiting the number of allowed structures and shape relationships

- Move towards 1-dimensional shapes and "Gridded Design Rules" (GDR)

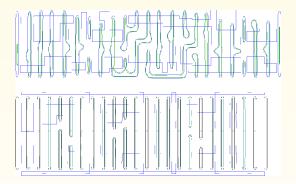

#### Example layout from Tela Innovations

## Regular Layout

#### Lithography simulations

- Lithographic distortions reduced significantly with 1-D shapes and GDR

- Scan D Flip-Flop, 45nm process

- Source: Tela Innovations, Inc., ISPD 2009

#### 2D Conventional Layout

#### 1D GDR Layout

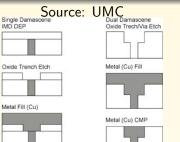

## Copper and the Damascene Process

#### Metal (Cu) CMP

IMD DEP

| · _  | _ | _ |

|------|---|---|

| - 11 |   |   |

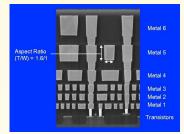

## Layers of Damascene Copper (Intel)

#### Copper Damascene Interconnect (Intel)

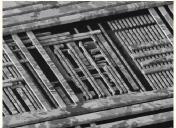

## Advanced Metallization

IBM Technology (in Rabaey, Digital Integrated Circuits, 2nd ed.) First commercial Copper process  $(0.12\mu)$

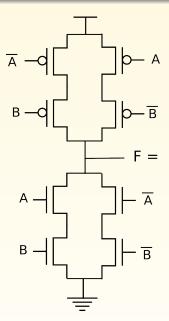

## Example CMOS Circuit

ECE Department, University of Texas at Austin