# 3. Implementing Logic in CMOS

#### Jacob Abraham

### Department of Electrical and Computer Engineering The University of Texas at Austin

VLSI Design Fall 2020

September 3, 2020

# Static CMOS Circuits

#### N- and P-channel Networks

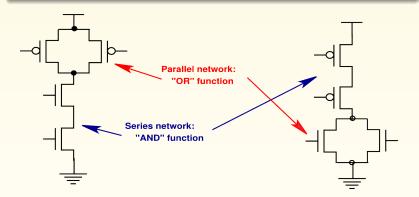

- N- and P-channel networks implement logic functions

- Each network connected between **Output** and  $V_{DD}$  or  $V_{SS}$

- Function defines path between the terminals

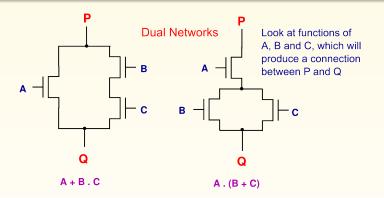

# Duality in CMOS Networks

Straightforward way of constructing static CMOS circuits is to implement dual N- and P- networks

- N- and P- networks must implement complementary functions

- Duality sufficient for correct operation (but not necessary)

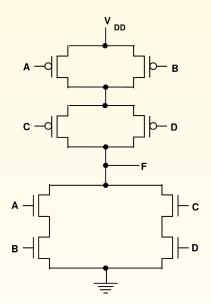

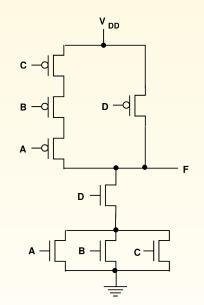

# Constructing Complex Gates

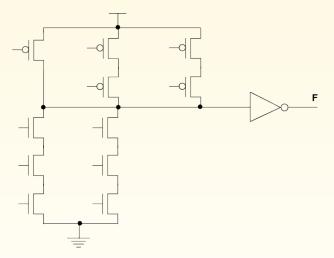

#### Example: $F = \overline{(A \cdot B) + (C \cdot D)}$

- **2** Identify AND, OR components: F is OR of AB, CD

- O Make connections of transistors

# Construction of Complex Gates, Cont'd

G Construct P-network by taking complement of N-expression (AB + CD), which gives the expression,  $(\overline{A} + \overline{B}) \cdot (\overline{C} + \overline{D})$

**6** Combine P and N circuits

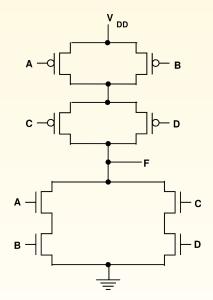

### Layout of Complex Gate

#### AND-OR-INVERT (AOI) gate

Note: Arbitrary shapes are not allowed in some nanoscale design rules

$$F = \overline{(A + B + C) \cdot D)}$$

Note:

N- and P- graphs are duals of each other

In this case, the function is the complement of the switching function between F and GND

Question: Does it make any difference to the function if the transistor with input D is connected between the parallel A, B, C, transistors and GND?

What about the electrical behavior?

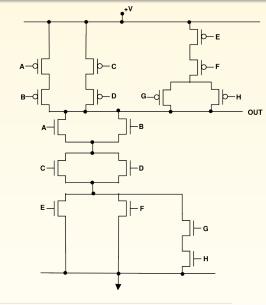

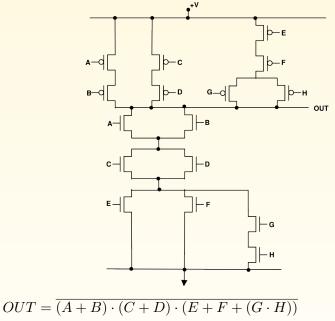

### Example of More Complex Gate

#### $OUT = (A+B) \cdot (C+D) \cdot (E+F+(G \cdot H))$

### Example of More Complex Gate

ECE Department, University of Texas at Austin

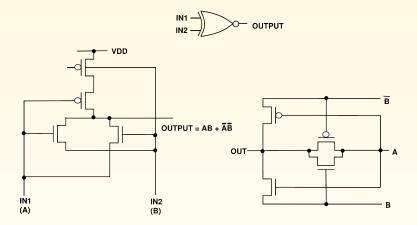

### **Exclusive-NOR** Gate in CMOS

Note: designs such as these should be checked very carefully for correct behavior using circuit simulation

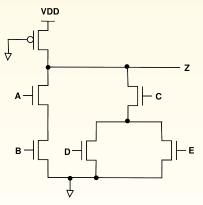

# Pseudo nMOS Logic

Based on the old NMOS technology where a "depletion" transistor was used as a pullup resistor

What happens when there is no path from Z to ground (i.e., Z = 1)?

What happens when there is a path from Z to ground (i.e., Z = 0)?

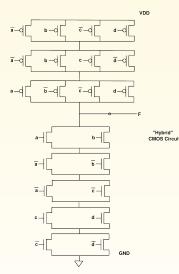

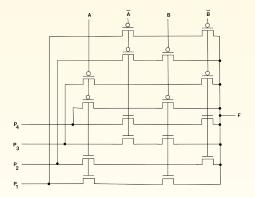

# Duality is Not Necessary for a CMOS Structure

Functions realized by N and P networks must be **complementary**, and one of them must conduct for every input combination

$$F = a \cdot b + \overline{a} \cdot \overline{b} + a \cdot c + c \cdot d + \overline{c} \cdot \overline{d}$$

The N and P networks are NOT duals, but the switching functions they implement are complementary

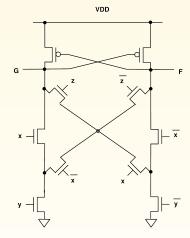

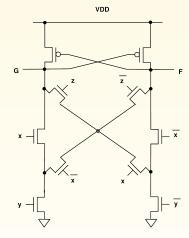

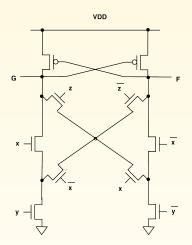

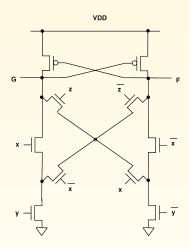

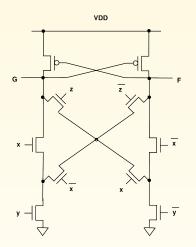

### Example of Another Complex CMOS Gate

This circuit does not have a pMOS network – just one transistor for each function; it will work only if F and G are complements of each other. Why?

Can evaluate the voltages at F and G ( $\{0, V_{DD}\}$ ) for each value of x, y, and z

$F = x \cdot \overline{y} \cdot z + \overline{x} \cdot y \cdot z + x \cdot y \cdot \overline{z} + x \cdot y \cdot z$

$G = \overline{x} \cdot y \cdot \overline{z} + x \cdot \overline{y} \cdot \overline{z} + \overline{x} \cdot \overline{y} \cdot z + \overline{x} \cdot \overline{y} \cdot \overline{z}$

### Example of Another Complex CMOS Gate

This circuit does not have a pMOS network – just one transistor for each function; it will work only if F and G are complements of each other. Why?

Can evaluate the voltages at F and G ( $\{0, V_{DD}\}$ ) for each value of x, y, and z

$$F = x \cdot \overline{y} \cdot z + \overline{x} \cdot y \cdot z + x \cdot y \cdot \overline{z} + x \cdot y \cdot z$$

$$G = \overline{x} \cdot y \cdot \overline{z} + x \cdot \overline{y} \cdot \overline{z} + \overline{x} \cdot \overline{y} \cdot z + \overline{x} \cdot \overline{y} \cdot \overline{z}$$

# Example of Another Complex CMOS Gate, Cont'd

Can also follow every path from F and G to GND and identify values of x, y, and z which will enable the path to be enabled.

$$F = \overline{x} \cdot \overline{y} + x \cdot \overline{y} \cdot \overline{z} + \overline{x} \cdot y \cdot \overline{z}$$

$$F = (x+y) \cdot (\overline{x} + y + z) \cdot (x + \overline{y} + z)$$

$$= (y+x \cdot z) \cdot (x + \overline{y} + z)$$

$$= x \cdot y + y \cdot z + x \cdot z$$

$$G = \overline{x} \cdot y \cdot \overline{z} + x \cdot \overline{y} \cdot \overline{z} + \overline{x} \cdot \overline{y}$$

$$= \overline{x} \cdot \overline{y} + \overline{x} \cdot \overline{z} + \overline{y} \cdot \overline{z}$$

Can you describe the functions in simple terms? (Hint: look at the number of input variables which are true (or false) when the output is 1.)

# Example of Another Complex CMOS Gate, Cont'd

Can also follow every path from F and G to GND and identify values of x, y, and z which will enable the path to be enabled.

$$\overline{F} = \overline{x} \cdot \overline{y} + x \cdot \overline{y} \cdot \overline{z} + \overline{x} \cdot y \cdot \overline{z}$$

$$F = (x + y) \cdot (\overline{x} + y + z) \cdot (x + \overline{y} + z)$$

$$= (y + x \cdot z) \cdot (x + \overline{y} + z)$$

$$= x \cdot y + y \cdot z + x \cdot z$$

$$G = \overline{x} \cdot y \cdot \overline{z} + x \cdot \overline{y} \cdot \overline{z} + \overline{x} \cdot \overline{y}$$

$$= \overline{x} \cdot \overline{y} + \overline{x} \cdot \overline{z} + \overline{y} \cdot \overline{z}$$

Can you describe the functions in simple terms? (Hint: look at the number of input variables which are true (or false) when the output is 1.)

# Example of Another Complex CMOS Gate, Cont'd

Can also follow every path from F and G to GND and identify values of x, y, and z which will enable the path to be enabled.

$$\overline{F} = \overline{x} \cdot \overline{y} + x \cdot \overline{y} \cdot \overline{z} + \overline{x} \cdot y \cdot \overline{z}$$

$$F = (x + y) \cdot (\overline{x} + y + z) \cdot (x + \overline{y} + z)$$

$$= (y + x \cdot z) \cdot (x + \overline{y} + z)$$

$$= x \cdot y + y \cdot z + x \cdot z$$

$$G = \overline{x} \cdot y \cdot \overline{z} + x \cdot \overline{y} \cdot \overline{z} + \overline{x} \cdot \overline{y}$$

$$= \overline{x} \cdot \overline{y} + \overline{x} \cdot \overline{z} + \overline{x} \cdot \overline{y}$$

Can you describe the functions in simple terms? (Hint: look at the number of input variables which are true (or false) when the output is 1.)

#### Voltages represent digital logic values

- Strength of signal:

- How close it approximates ideal voltage

- $\bullet~V_{DD}$  and GND rails are strongest 1 and 0

- nMOS transistors pass a strong 0

- But degraded or weak 1

- pMOS transistors pass a strong 1

- But degraded or weak 0

# Therefore, nMOS transistors are best for the "pull-down" network

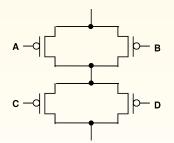

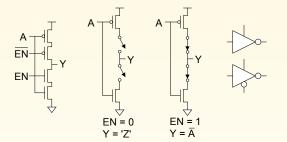

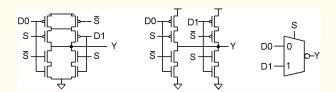

### Pass Transistors and Transmission Gates

Transistors can be used as switches; however, they could produce degraded outputs

Transmission gates pass both 0 and 1 well

### Pass Transistor Logic

#### "Pull-Up" Circuit

Used to restore degraded logic 1 from output of nMOS pass transistor

Group similar transistors, so they can be in the same well

| EN | А | Y |

|----|---|---|

| 0  | 0 | Ζ |

| 0  | 1 | Ζ |

| 1  | 0 | 0 |

| 1  | 1 | 1 |

Tristate Buffer produces Z (high impedance) when not enabled

Non-Restoring Tristate

- Transmission gate acts as a tristate buffer

- Only two transistors, but nonrestoring

- Noise on A is passed to Y

Tristate inverter produces restored output, but complements signal

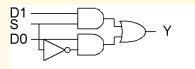

| S | D1 | D0 | Y |

|---|----|----|---|

| 0 | Х  | 0  | 0 |

| 0 | Х  | 1  | 1 |

| 1 | 0  | Х  | 0 |

| 1 | 1  | Х  | 1 |

How many transistors are needed? (The better design uses 3 NAND gates and 1 inverter)

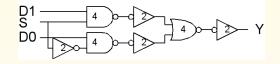

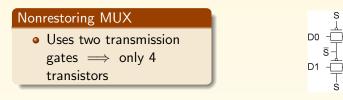

### Transmission Gate MUX

#### Inverting MUX – adds an inverter

- Uses compound gate AOI22

- Alternatively, a pair of tristate inverters (same thing)

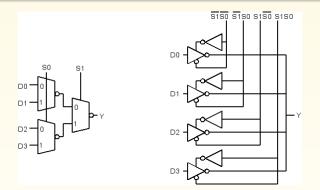

#### A 4:1 MUX chooses one of 4 inputs using two selects

- Two levels of 2:1 MUXes

- Alternatively, four tristates

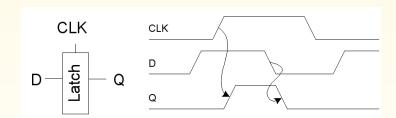

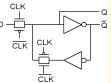

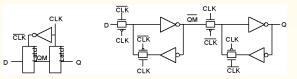

# D Latch

#### **Basic Memory Element**

- When CLK = 1, latch is transparent

- D flows through to Q like a buffer

- When CLK = 0, the latch is opaque

- Q holds its old value independent of D

- a.k.a., transparent latch or level-sensitive latch

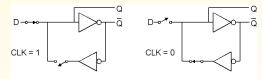

# D Latch, Cont'd

D Latch Design: MUX chooses between D and old Q

D Latch Operation

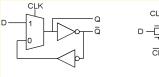

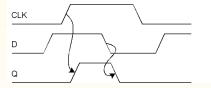

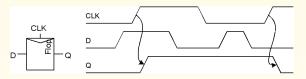

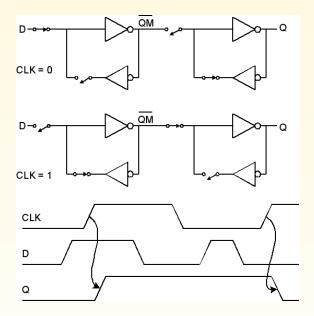

# D Flip-Flop (D-Flop)

#### Another common storage element

- When CLK rises, D is copied to Q

- At all other times, Q holds its value

- positive edge-triggered flip-flop or master-slave flip-flop

- Built from "master" and "slave" D latches

### **D** Flip-Flop Operation

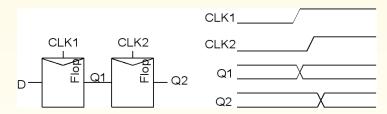

# Race Condition – Hold Time Failure

#### Back-to-back flops can malfunction from clock skew

- Second flip-flop fires late

- Sees first flip-flop change and captures its result

- Called hold-time failure or race condition

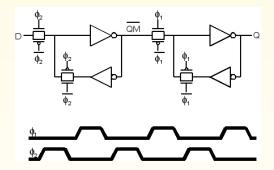

# Non-Overlapping Clocks

#### A simple way to prevent races

- This works as long as non-overlap exceeds clock skew

- Used in safe (conservative) designs

- Industry does not generally use this approach managing skew more carefully instead

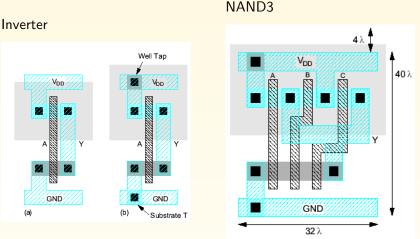

#### Building a library of standard cells

- Layout can be time consuming

- One solution is to have layouts of commonly used functions (Inverter, NAND, OR, MUX, etc.), designed to fit together very well

#### Standard cell design methodology

- V<sub>DD</sub> and GND should abut (standard height)

- Adjacent gates should satisfy design rules

- nMOS at bottom and pMOS at top

- All gates include well and substrate contacts

- One of the large industry suppliers is ARM, others include TSMC and other foundries

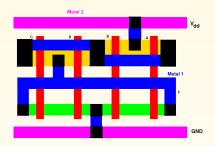

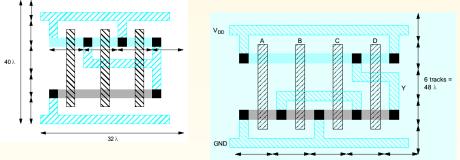

# Examples of Standard Cell Layout

Horizontal N-diffusion and P-diffusion strips Vertical Polysilicon gates Metal1  $V_{DD}$  rail at top, Metal1 GND rail at bottom  $32\lambda$  by  $40\lambda$

ECE Department, University of Texas at Austin

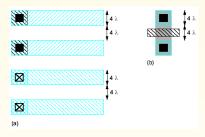

Wiring Track is the space required for a wire Example,  $4\lambda$  width,  $4\lambda$  spacing from neighbor =  $8\lambda$  pitch Transistors also consume one wiring track

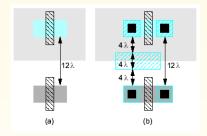

Example, well spacing: wells must surround transistors by  $6\lambda$ Implies  $12\lambda$  between opposite transistor flavors Leaves room for one wire track

Estimate area by counting wiring tracks Multiply by 8 to express in  $\lambda$

Estimating area of O3AI Sketch a stick diagram and estimate area

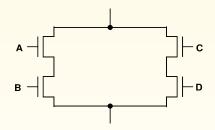

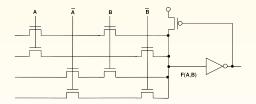

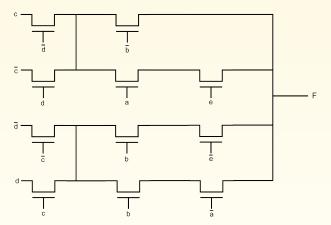

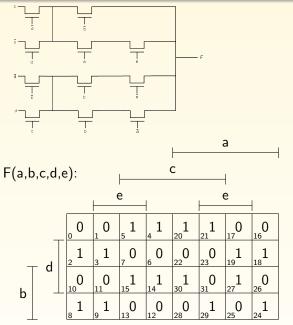

Fill in the Karnaugh map to represent the Boolean function implemented by the pass-transistor circuit.

ECE Department, University of Texas at Austin

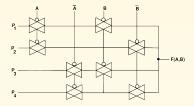

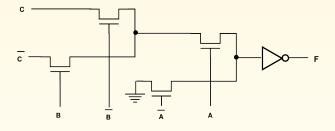

Find the function, F, implemented by the following circuit

$\overline{A} + BC + \overline{B} \ \overline{C}$

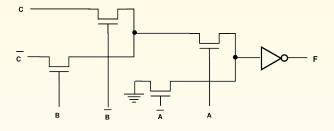

Find the function, F, implemented by the following circuit

$\overline{A} + BC + \overline{B} \ \overline{C}$

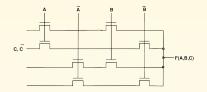

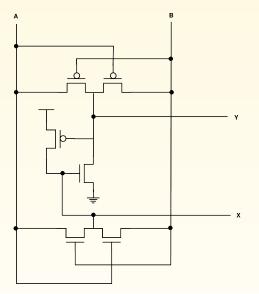

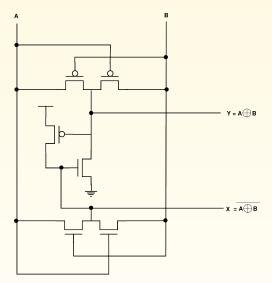

Find the functions X and Y implemented by the following circuit

Find the functions X and Y implemented by the following circuit

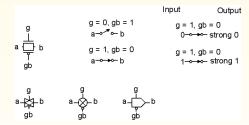

### Functions to Circuits

Label the circuit so that it implements the function:  $F=a\cdot(b\cdot c+\bar{b}\cdot\bar{c})$