|                    | 7. Combinational Circuits                                                                     |

|--------------------|-----------------------------------------------------------------------------------------------|

|                    | Jacob Abraham                                                                                 |

|                    | Department of Electrical and Computer Engineering<br>The University of Texas at Austin        |

|                    | VLSI Design<br>Fall 2020                                                                      |

|                    | September 17, 2020                                                                            |

| Department, Univer | sity of Texas at Austin Lecture 7. Combinational Circuits Jacob Abraham, September 17, 2020 1 |

# Support for Students

ECE Department, University of Texas at Austin

"IEEE UT created a Discord server to help all ECE students with group studying and collaboration. Each ECE course has a channel where you can communicate with other students in the class about coursework. The Discord can be also be used for discussion about other ECE-related topics, including interview preparation and registration advice. Use this link to join the Discord: https://discord.gg/7kWzKze (IEEE membership not required to join)."

Lecture 7. Combinational Circuits

Jacob Abraham, September 17, 2020 1 / 26

| view: Logical Ei  | fort, Gates and Pat                                  | ns                                     |

|-------------------|------------------------------------------------------|----------------------------------------|

| Term              | Stage                                                | Path                                   |

| Number of stages  | 1                                                    | N                                      |

| Logical effort    | g                                                    | $G = \prod g_i$                        |

| Electrical effort | $h = \frac{C_{out}}{C_{in}}$                         | $H = \frac{C_{out-path}}{C_{in-path}}$ |

| Branching effort  | $b = \frac{C_{on-path} + C_{off-path}}{C_{on-path}}$ | $B = \prod b_i$                        |

| Effort            | f = gh                                               | F = GBH                                |

| Effort delay      | f                                                    | $D_F = \sum f_i$                       |

| Parasitic delay   | р                                                    | $P = \sum p_i$                         |

| Delay             | d = f + p                                            | $D = \sum d_i = D_F + P$               |

| Steps in Logical Effort                                          |                                  |  |

|------------------------------------------------------------------|----------------------------------|--|

| 1. Compute path effort                                           | F = GBH                          |  |

| 2. Estimate best number of stages                                | $N = \log_4 F$                   |  |

| 3. Sketch path with N stages                                     |                                  |  |

| 4. Estimate least delay                                          | $D = NF^{\frac{1}{N}} + P$       |  |

| 5. Determine best stage effort                                   | $\hat{f} = F^{\frac{1}{N}}$      |  |

| 6. Find gate sizes                                               | $C_{in} = \frac{g_i C_{out}}{f}$ |  |

|                                                                  | -                                |  |

| Limits of logical effort                                         |                                  |  |

| <ul> <li>Chicken and egg problem</li> </ul>                      |                                  |  |

| • Need path to compute G                                         |                                  |  |

| <ul> <li>But, don't know number of stages without G</li> </ul>   |                                  |  |

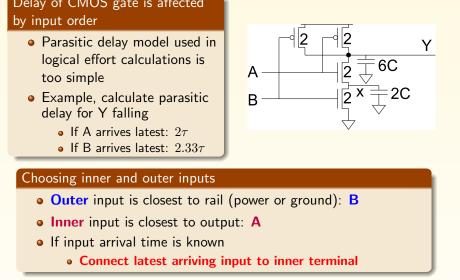

| • Simplistic delay model, neglects input rise time effects       |                                  |  |

| Interconnect                                                     |                                  |  |

| • Iteration required in designs with significant wires           |                                  |  |

| • Maximum speed only                                             |                                  |  |

| <ul> <li>Not minimum area/power for constrained delay</li> </ul> |                                  |  |

ECE Department, University of Texas at Austin

Jacob Abraham, September 17, 2020 2 / 26

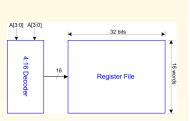

# Review: Decoder Example, Number of Stages

- 16 word, (32 bit) register file

- Each bit presents load of 3 unit-sized transistors

- True and complementary address inputs A[3:0]

- Each input may drive 10 unit-sized transistors

b Abraham, September 17, 2020 4 / 26

### Find: number of stages, sizes of gates, speed

- Decoder effort is mainly electrical and branching

- Electrical Effort: H = (32\*3)/10 = 9.6

- Branching Effort: B = 8

- If we neglect logical effort (assume G = 1)

Path Effort: F = GBH = 76.8

- Number of Stages:  $N = \log_4 F = 3.1$

- Try a 3-stage design

ECE Department, University of Texas at Austin

# **Decoder Review:** Gate Sizes and Delay Logical Effort: G = 1 \* 6/3 \* 1 = 2Path Effort: F = GBH = 154Stage Effort: $\hat{f} = F^{\frac{1}{3}} = 5.36$ Path Delay: $D = 3\hat{f} + 1 + 4 + 1 = 22.1$ Gate sizes: z = 96\*1/5.36 = 18Gate sizes: y = 18\*2/5.36 = 6.7A[3] A[3] A[2] A[2] A[1] A[1] A[0] A[0] 10/10/ word[0] 96 units of wordline capacitance word[15] ECE Department, University of Texas at Austin

# Decoder Review: Comparison

Compare many alternatives with a spreadsheet

| Design                  | Ν | G    | Ρ | D    |

|-------------------------|---|------|---|------|

| NAND4-INV               | 2 | 2    | 5 | 29.8 |

| NAND2-NOR2              | 2 | 20/9 | 4 | 30.1 |

| INV-NAND4-INV           | 3 | 2    | 6 | 22.1 |

| NAND4-INV-INV-INV       | 4 | 2    | 7 | 21.1 |

| NAND2-NOR2-INV-INV      | 4 | 20/9 | 6 | 20.5 |

| NAND2-INV-NAND2-INV     | 4 | 16/9 | 6 | 19.7 |

| INV-NAND2-INV-NAND2-INV | 5 | 16/9 | 7 | 20.4 |

| NAND2-INV-NAND2-INV-INV | 6 | 16/9 | 8 | 21.6 |

### Review: Logical Effort Example

ECE Department, University of Texas at Aus

ECE Department, University of Texas at Austin

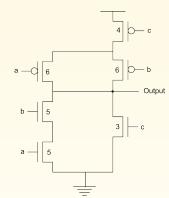

Find the logical efforts for the inputs, a, b, and c in the circuit below.

| Output |        |         |  |

|--------|--------|---------|--|

|        | Rising | Falling |  |

| а      |        |         |  |

| b      |        |         |  |

| с      |        |         |  |

am, September 17, 2020 7 / 26

b Abraham, September 17, 2020 6 / 26

Suggest a way to reduce the parasitic delay of this circuit by modifying the structure (but keeping the same function).

Department of Electrical and Computer Engineering, The University of Texas at Austin J. A. Abraham, September 17, 2020

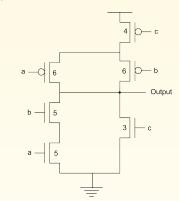

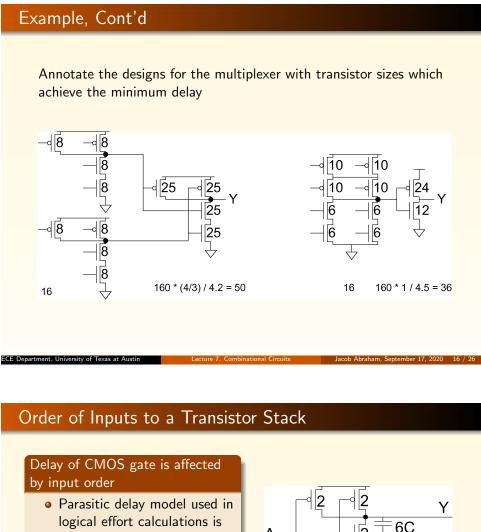

### Example, Cont'd

Find the logical efforts for the inputs, a, b, and c in the circuit below.

| Output |        |         |  |

|--------|--------|---------|--|

|        | Rising | Falling |  |

| а      | 55/18  | 22/15   |  |

| b      | 55/18  | 22/15   |  |

| с      | 35/18  | 7/9     |  |

mber 17, 2020 8 / 26

To reduce the parasitic delay of this circuit, swap the parallel combination of pMOS transistors with inputs a, b with the pMOS transistor with input c

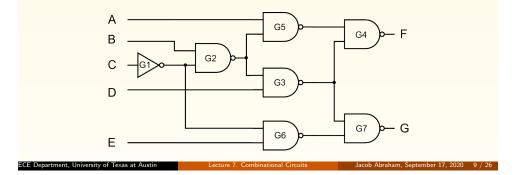

### **Example:** Sizing Paths

ECE Department, University of Texas at Austin

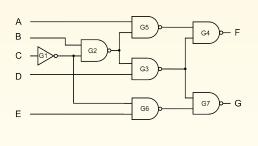

Size the path G1-G2-G3-G4 in the circuit below using logical effort Find the minimum delay and give the sizes of the P and N transistors to achieve this delay

Assume that the off-path capacitance is the same as the on-path capacitance for each branch

Input capacitance of Inverter G1 = 3 units.

Load capacitance driven by Gate G4 = 52 units.

# Sizing Paths, Cont'd

Size the path G1-G2-G3-G4 in the circuit Input capacitance of Inverter G1 = 3 units. Load capacitance driven by Gate G4 = 52 units.

| Sizes of transistors: |   |   |

|-----------------------|---|---|

| Gate                  | Р | Ν |

| Gate G4               | 8 | 8 |

| Gate G3               | 5 | 5 |

| Gate G2               | 3 | 3 |

| Gate G1               | 2 | 1 |

Jacob Abraham, September 17, 2020 10 / 26

Delay = |4.8| FO4 units

c .

Delay of the path from A through gates G5 and G4 (assuming the input from G2=1 and D=0):  $\boxed{2.08}$  FO4 units

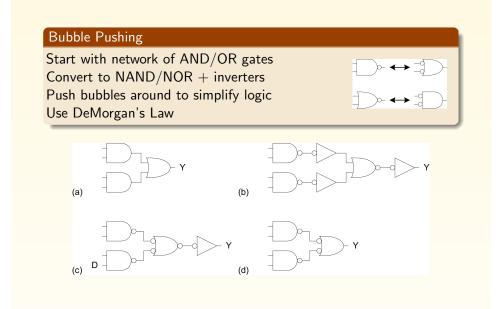

### Example of "Bubble Pushing"

ECE Department, University of Texas at Austin

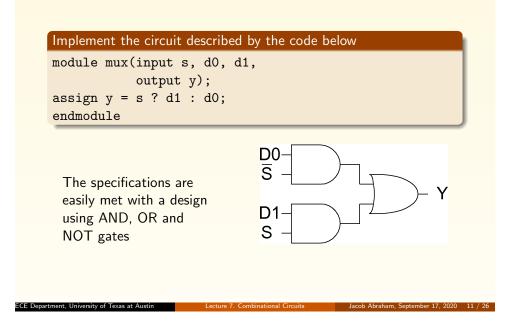

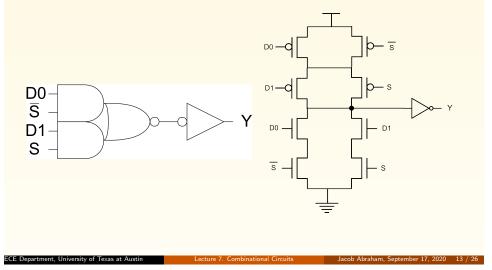

# Convert to Design using NAND/NOR/NOT Gates

# Example, Continued

ECE Department, University of Te

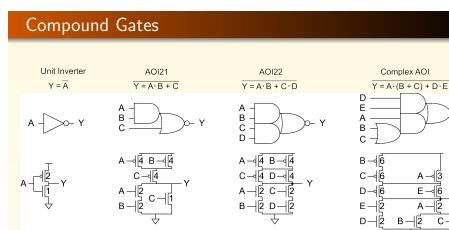

Now, design the circuit with one compound gate and one inverter. Assume that  $\bar{S}$  is available

er 17, 2020 12 / 26

g<sub>A</sub> = 6/3

$g_{_{\rm B}} = 6/3$

$g_{c} = 5/3$

p = 7/3

### Another Example

ECE Department, University of Texas at Au

$g_{A} = 3/3$

p = 3/3

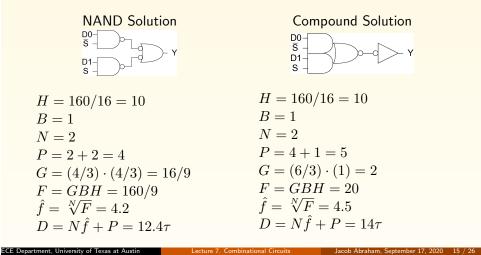

A multiplexer has a maximum input capacitance of 16 units on each input. It must drive a load of 160 units

$g_{A} = 6/3$

$g_{_{\rm B}} = 6/3$

$g_{c} = 6/3$

$g_{D} = 6/3$

p = 12/3

Estimate the delay of the NAND and compound gate designs

C – [2

g<sub>A</sub> = 5/3

g<sub>B</sub> = 8/3

$g_c = 8/3$

$g_D = 8/3$

g<sub>E</sub> = 8/3

p = 16/3

b Abraham, September 17, 2020 14 / 26

Jacob Abraham, September 17, 2020 17 / 26

ECE Department, University of Texas at Austin

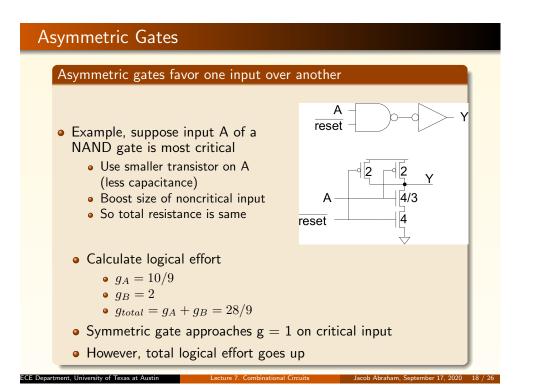

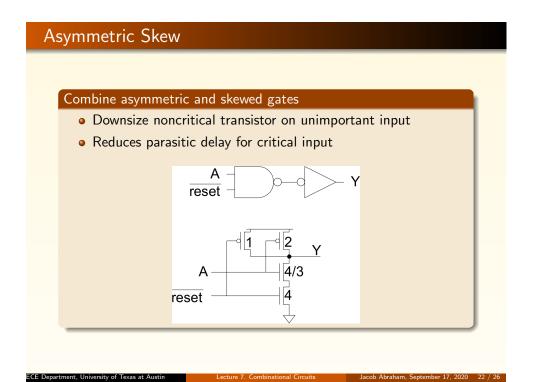

# <section-header><section-header><section-header><section-header><section-header><text><image>

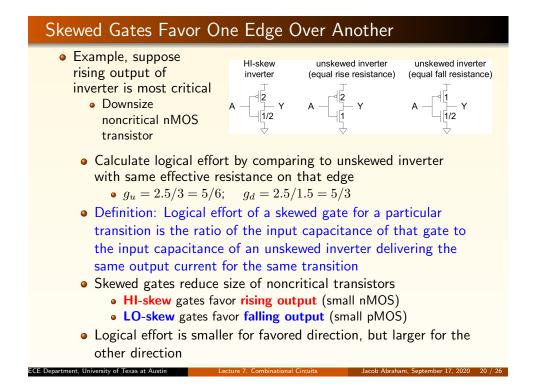

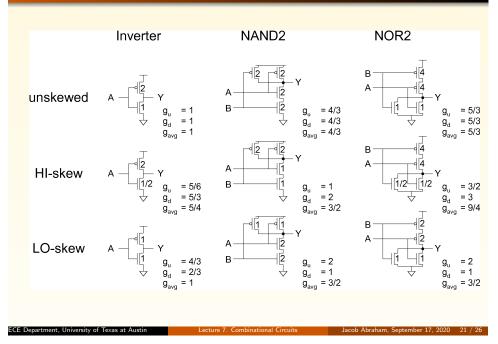

# Catalog of Skewed Gates

# Example – I

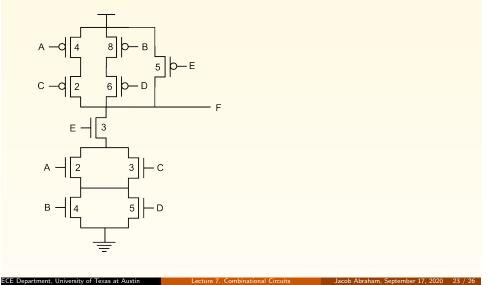

Find the (worst case) logical efforts of the different inputs in the CMOS circuit below.

### Example - II

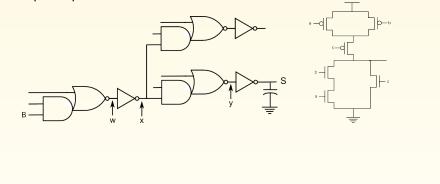

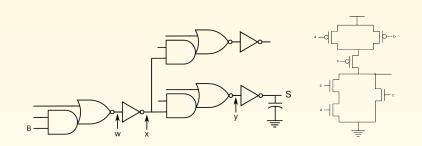

(a) Calculate the delay of the segment from B to S of the adder shown below (the AOI21 is a single stage, shown on the right), given that the output capacitance is 25 units (normalized), and the input capacitance at B is 6 units.

Example - II, Cont'd

ECE Department, University of Texas at Austin

ECE Department, University of Texas at Austin

(b) Calculate the capacitances of the nodes y,  $\times$  and w, and the resulting widths of the transistors.

Lecture 7. Combinational Circuits

Jacob Abraham, September 17, 2020 24 / 26

Jacob Abraham, September 17, 2020 25 / 26

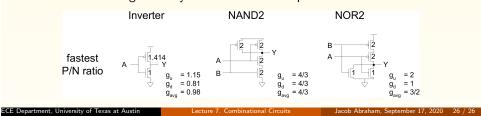

# Best P/N Ratio

- Alternative: choose ratio for least average delay • Example: inverter

- Delay driving identical inverter

- $t_{pdf} = (P+1)$

•

$$t_{pdr} = (P+1)(\mu/P)$$

- $t_{pd} = (P+1)(1+\mu/P)/2 = (P+1+\mu+\mu/P)/2$

- Differentiating  $t_{pd}$  w.r.t. P, we get, least delay for  $P = \sqrt{\mu}$  In general, best P/N ratio is sqrt of that giving equal delay

- - Only improves average delay slightly for inverters

- But significantly decreases area and power

P