Department of Electrical and Computer Engineering, The University of Texas at Austin J. A. Abraham, September 22, 2020

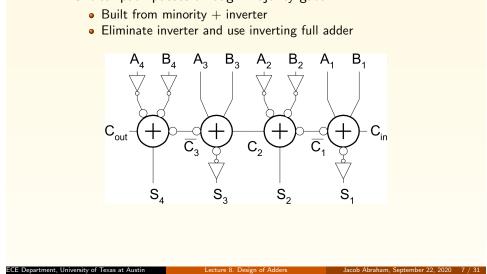

#### Full Adder Design I

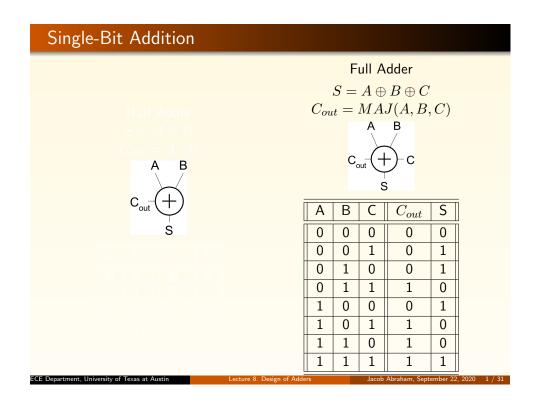

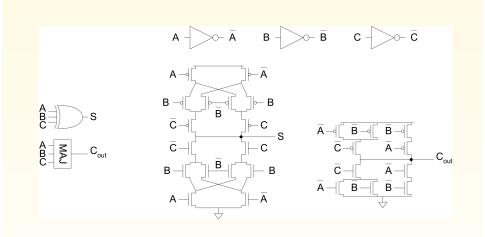

Brute force implementation from equations  $S = A \oplus B \oplus C$  $C_{out} = MAJ(A, B, C)$

#### Full Adder Design II

ECE Department, University of Texas at A

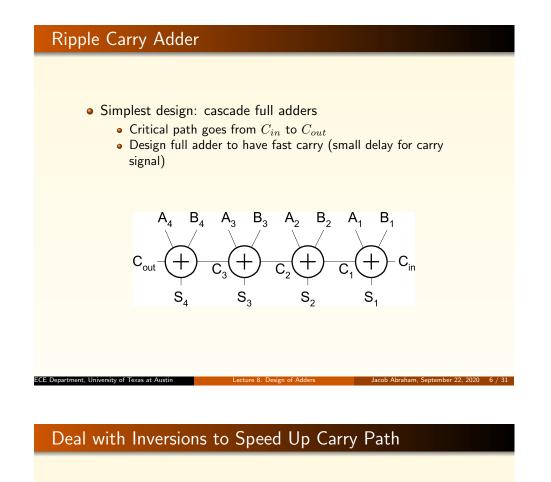

$\bullet\,$  Critical path is usually C to  $C_{out}$  in ripple adder

2 / 31

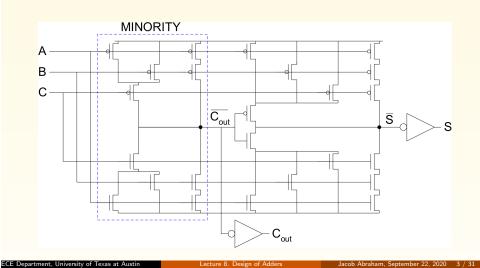

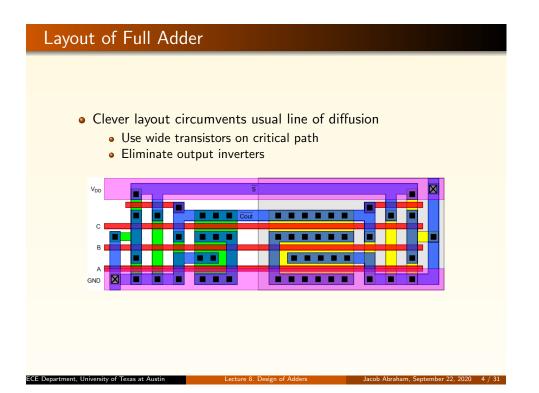

#### Full Adder Design III • Complementary Pass Transistor Logic (CPL) • Slightly faster, but more area В B С В B С $\overline{\mathbf{C}}$ B ē в в Ē в С R B $\overline{C}$ С в B ECE Department, University of Texas at Austin Jacob Abraham, September 22, 2020 5 / 31

4

ECE Department, University of Texas at A

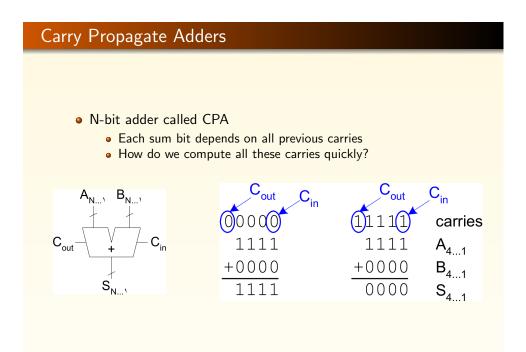

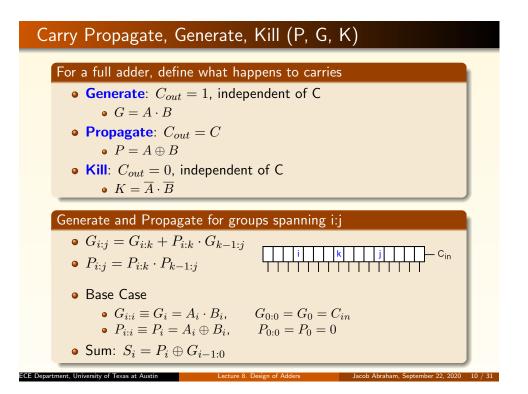

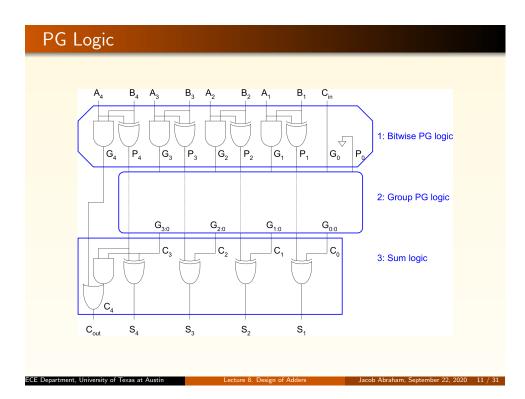

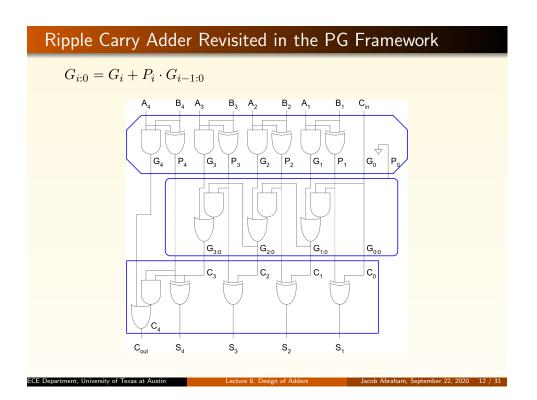

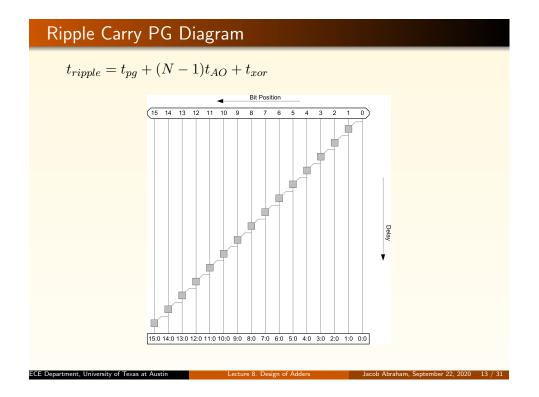

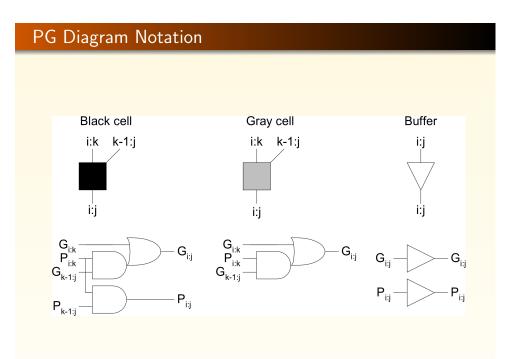

Carry Propagate, Generate, Kill (P, G, K) For a full adder, define what happens to carries • Generate:  $C_{out} = 1$ , independent of C •  $G = A \cdot B$ • **Propagate**:  $C_{out} = C$ •  $P = A \oplus B$ • Kill:  $C_{out} = 0$ , independent of C •  $K = \overline{A} \cdot \overline{B}$ Generate and Propagate for groups spanning i:j •  $G_{i:i} = G_{i:k} + P_{i:k} \cdot G_{k-1:i}$ •  $P_{i:j} = P_{i:k} \cdot P_{k-1:j}$ Base Case •  $G_{i:i} \equiv G_i = A_i \cdot B_i$ ,  $G_{0:0} = G_0 = C_{in}$ •  $P_{i:i} \equiv P_i = A_i \oplus B_i$ ,  $P_{0:0} = P_0 = 0$ • Sum:  $S_i = P_i \oplus G_{i-1:0}$ ECE Department, University of Texas at Austin lacob Abraham, September 22, 2020 9 / 31

Department of Electrical and Computer Engineering, The University of Texas at Austin J. A. Abraham, September 22, 2020

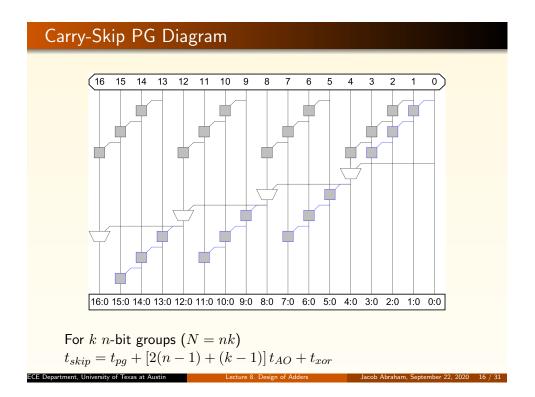

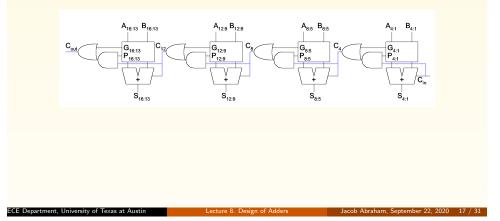

### Carry-Skip Adder

ECE Department, University of Texas at Austi

- Carry-ripple is slow through all N stages

- Carry-skip allows carry to skip over groups of n bits

- Decision based on n-bit propagate signal

Jacob Abraham, September 22, 2020 14 / 31

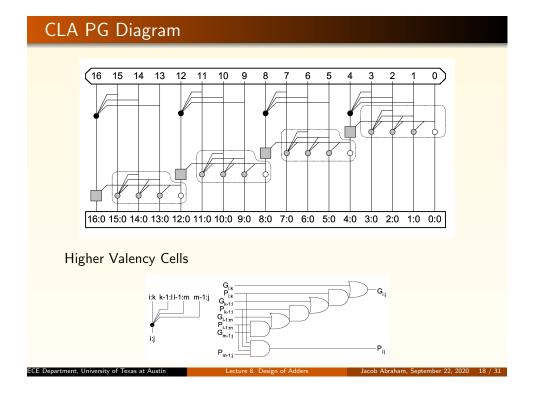

# Carry-Lookahead Adder (CLA)

- Carry-lookahead adder computes  $G_{i:0}$  for many bits in parallel

- Uses higher-valency cells with more than two inputs

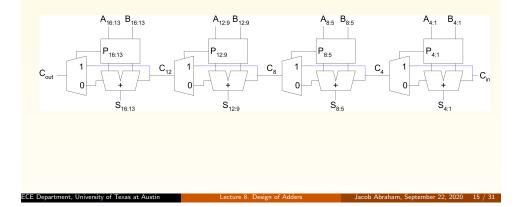

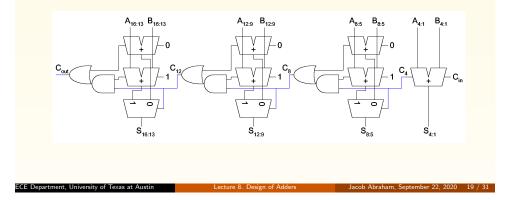

## Carry-Select Adder

- Trick for critical paths dependent on late input X

- Precompute two possible outputs for X = 0, 1

- Select proper output when X arrives

- Carry-select adder precomputes n-bit sums for both possible carries into n-bit group

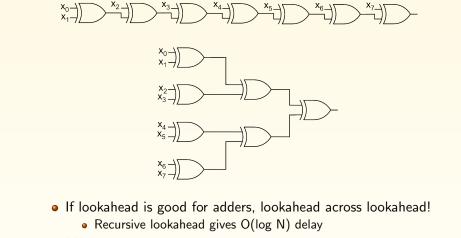

#### **Tree Adders**

ECE Department, University of Texas at Austin

- Tree structures can be used to speed up computations

- Look at computing the XOR of 8 bits using 2-input XOR-gates

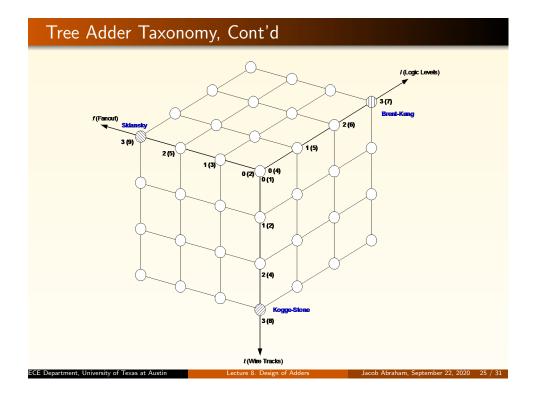

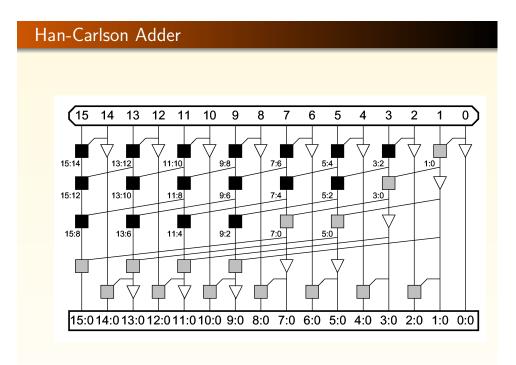

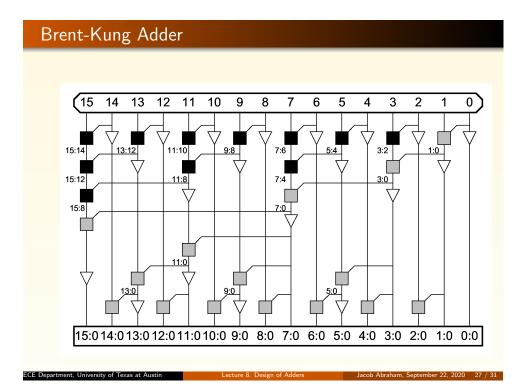

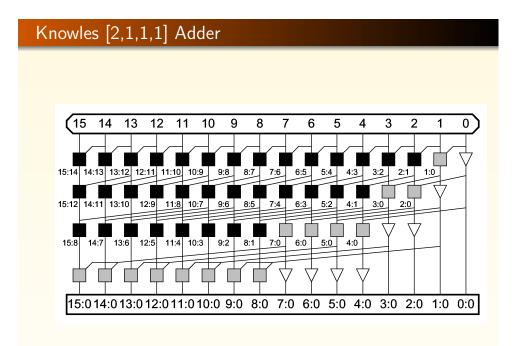

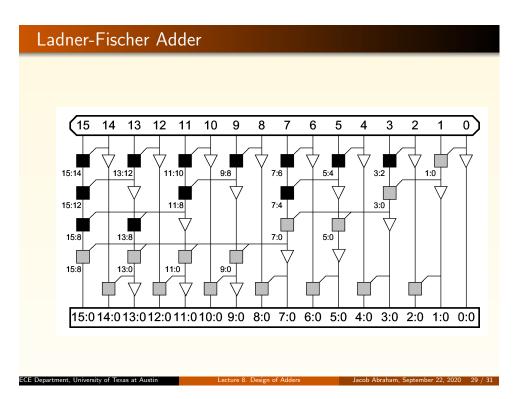

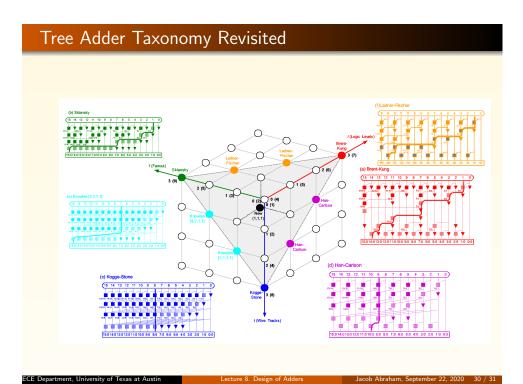

Many variations on tree adders

Jacob Abraham, September 22, 2020 20 / 31

ECE Department, University of Texas at Austin

Jacob Abraham, September 22, 2020 26 / 31

ECE Department, University of Texas at Au

Jacob Abraham, September 22, 2020 28 / 31

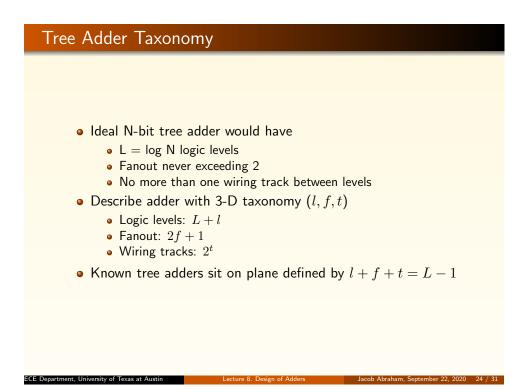

# Summary of Adders

ECE Department, University of Texas at Austin

Adder architectures offer area/power/delay tradeoffs Choose the best one for your application

| Architecture    | Classifi- | Logic lev-  | Max.   | Tra- | Cells        |

|-----------------|-----------|-------------|--------|------|--------------|

|                 | cation    | els         | fanout | cks  |              |

| Ripple Carry    |           | N-1         | 1      | 1    | Ν            |

| Carry-skip(n=4) |           | N/4 + 5     | 2      | 1    | 1.25N        |

| Carry-inc.(n=4) |           | N/4 + 2     | 4      | 1    | 2N           |

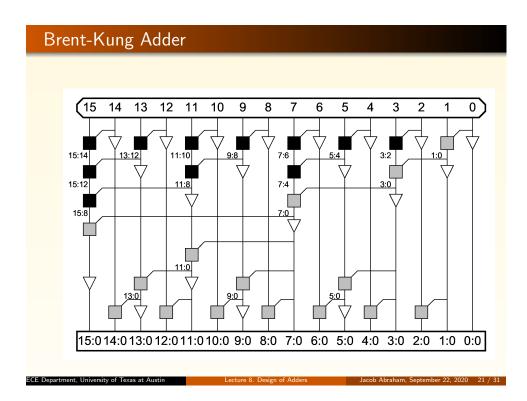

| Brent-Kung      | (L-1,0,0) | $2log_2N-1$ | 2      | 1    | 2N           |

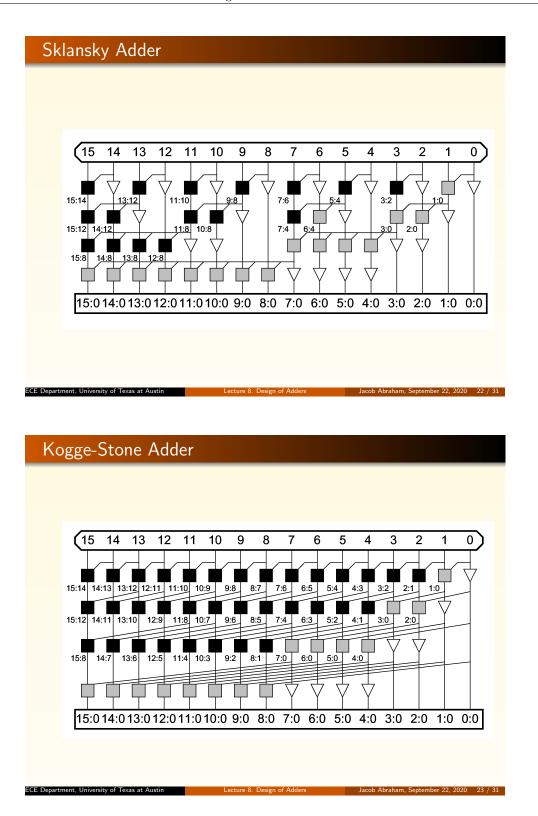

| Sklansky        | (0,L-1,0) | $log_2N$    | N/2+1  | 1    | $0.5Nlog_2N$ |

| Kogge-Stone     | (0,0,L-1) | $log_2N$    | 2      | N/2  | $Nlog_2N$    |

Jacob Abraham, September 22, 2020 31 / 31