Jacob Abraham

Department of Electrical and Computer Engineering The University of Texas at Austin

> VLSI Design Fall 2020

September 24, 2020

re 9. Datapath Desi

Jacob Abraham, September 24, 2020 1 / 27

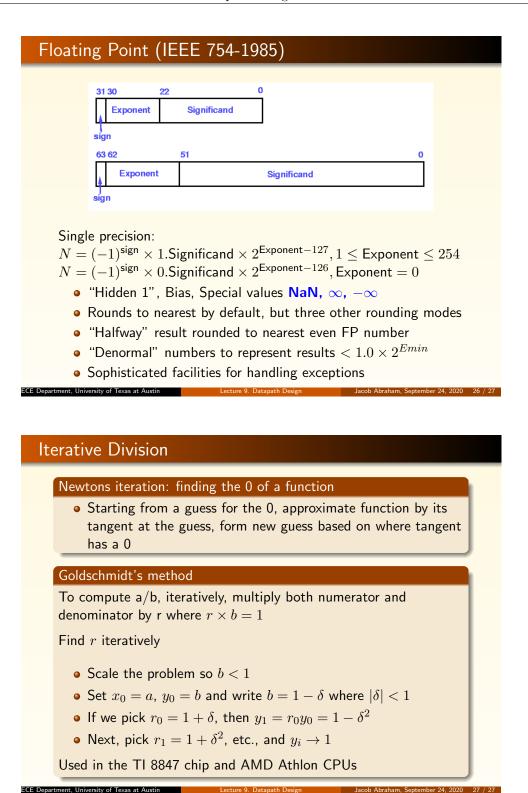

#### 1s and 0s Detectors

ECE Department, University of Texas at Austin

- 1s detector: N-input AND gate

- Os detector: Inversions + 1s detector (N-input NOR)

## Signed Versus Unsigned Numbers

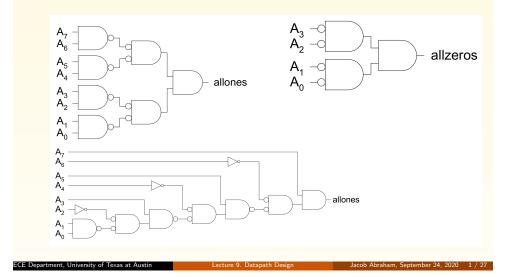

- For signed numbers, comparison is harder

- C: carry out

- Z: zero (all bits of A-B are 0)

- N: negative (MSB of result)

- V: overflow (inputs had different signs, output sign  $\neq$  B)

#### Magnitude Comparison

|             | Relation                | Unsigned Comparison           | Signed Comparison          |                             |

|-------------|-------------------------|-------------------------------|----------------------------|-----------------------------|

|             | A = B                   | Ζ                             | Ζ                          |                             |

|             | $A \neq B$              | $\overline{Z}$                | $\overline{Z}$             |                             |

|             | A < B                   | $\overline{C+Z}$              | $\overline{(N\oplus V)+Z}$ |                             |

|             | A > B                   | $\overline{C}$                | $(N\oplus V)$              |                             |

|             | $A \leq B$              | C                             | $\overline{(N\oplus V)}$   |                             |

|             | $A \ge B$               | $\overline{C} + Z$            | $(N \oplus V) + Z$         |                             |

| ECE Departr | ment, University of Tex | as at Austin Lecture 9. Datap | ath Design Jacob Abraham   | , September 24, 2020 3 / 27 |

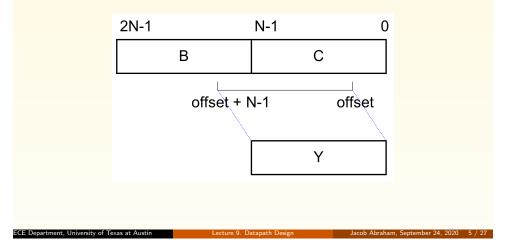

#### Shifters

#### • Logical Shift:

- Shifts number left or right and fills with 0s

- 1011 LSR 1 = 0101

- 1011 LSL 1 = 0110

#### • Arithmetic Shift:

- Shifts number left or right; right shift sign extend

- 1011 ASR 1 = 1101

- 1011 ASL 1 = 0110

#### Rotate:

• Shifts number left or right and fills with lost bits

ire 9. Datapath Desi

- 1011 ROR 1 = 1101

- 1011 ROL 1 = 0111

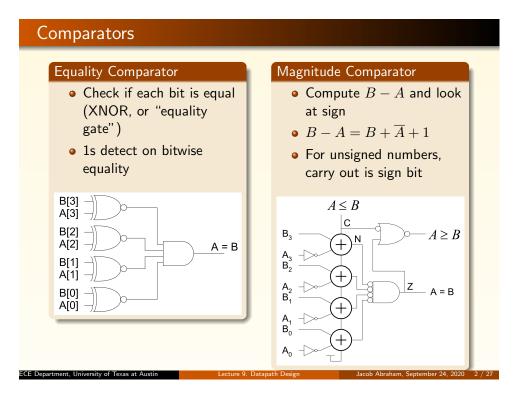

### **Funnel Shifter**

ECE Department, University of Texas at Austin

- A funnel shifter can do all six types of shifts

- Selects N-bit field Y from 2N-bit input

- Shift by k bits  $(0 \le k < N)$

Jacob Abraham, September 24, 2020 4 / 27

# Funnel Shifter Operation

| Shift Type       | В                                        | С                   | Offset |

|------------------|------------------------------------------|---------------------|--------|

| Logical Right    | 00                                       | $A_{N-1}\ldots A_0$ | k      |

| Logical Left     | $A_{N-1}\ldots A_0$                      | 00                  | N-k    |

| Arithmetic Right | $A_{N-1} \dots A_{N-1}$ (sign extension) | $A_{N-1}\ldots A_0$ | k      |

| Arithmetic Left  | $A_{N-1}\ldots A_0$                      | 0                   | N-k    |

| Rotate Right     | $A_{N-1}\ldots A_0$                      | $A_{N-1}\ldots A_0$ | k      |

| Rotate Left      | $A_{N-1}\ldots A_0$                      | $A_{N-1}\ldots A_0$ | N-k    |

e 9. Datapath D

Computing N-k requires an adder

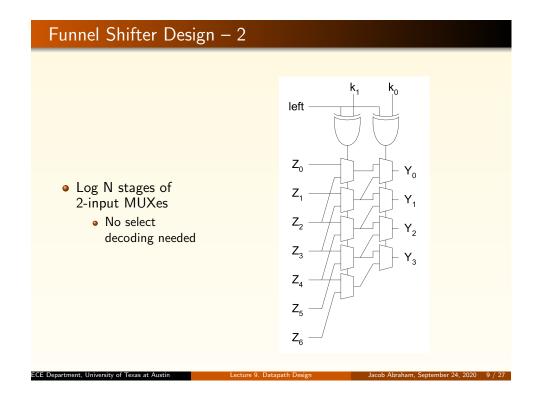

# Simplified Funnel Shifter

ECE Department, University of Texas at Austin

ECE Department, University of Texas at Austin

Optimize down to 2N-1 bit input

| Shift Type       | Z                                          | Offset         |

|------------------|--------------------------------------------|----------------|

| Logical Right    | $00, A_{N-1} \dots A_0$                    | k              |

| Logical Left     | $A_{N-1} \dots A_0, 00$                    | $\overline{k}$ |

| Arithmetic Right | $A_{N-1}\ldots A_{N-1}, A_{N-1}\ldots A_0$ | k              |

| Arithmetic Left  | $A_{N-1} \dots A_0, 00$                    | $\overline{k}$ |

| Rotate Right     | $A_{N-2}\ldots A_0, A_{N-1}\ldots A_0$     | k              |

| Rotate Left      | $A_{N-1}\ldots A_0, A_{N-1}\ldots A_1$     | $\overline{k}$ |

Jacob Abraham, September 24, 2020 6 / 27

Jacob Abraham, September 24, 2020 7 / 27

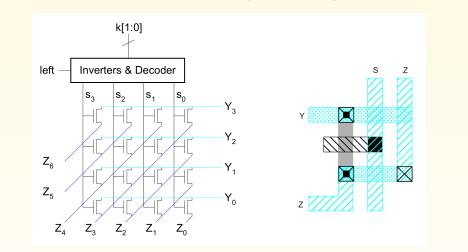

# Funnel Shifter Design – 1

ECE Department, University of Te

- N N-input multiplexers

- Use 1-of-N hot select signals for shift amount

- nMOS pass transistor design (Note:  $V_t$  drops)

8 / 27

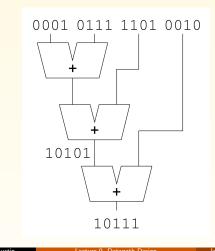

## Multi-Input Adders

- Suppose we want to add k N-bit words

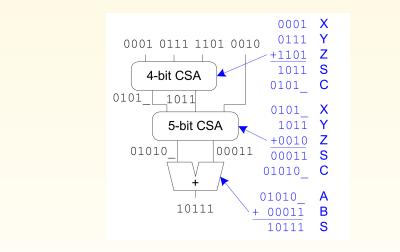

Example: 0001 + 0111 + 1101 + 0010 = 10111

- Straightforward solution: k-1 N-input CPAs

- Large and slow

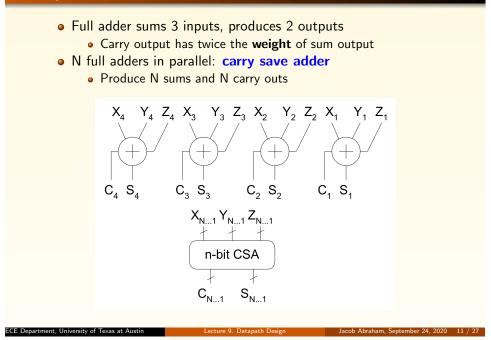

## Carry Save Addition

ECE Department, University of Texas at A

b Abraham, September 24, 2020 10 / 27

# **CSA** Application

ECE Department, University of Texas at Au

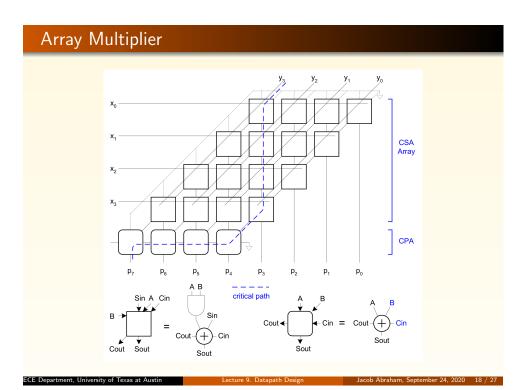

- Use k-2 stages of CSAs

Keep result in carry-save redundant form

- Final CPA computes actual result

bb Abraham, September 24, 2020 12 / 27

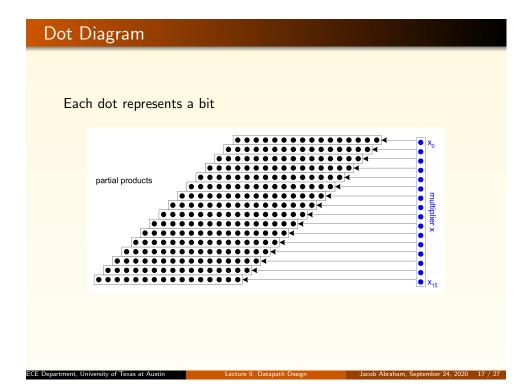

# General Form for Multiplication

ECE Department, University of Texas at Austi

Multiplicand:

$$Y = (y_{M-1}, y_{M-2}, ..., y_1, y_0)$$

Multiplier:  $X = (x_{N-1}, x_{N-2}, ..., x_1, x_0)$

Product:

$$P = \left(\sum_{j=0}^{M-1} y_j 2^j\right) \left(\sum_{i=0}^{N-1} x_i 2^i\right) = \sum_{i=0}^{N-1} \sum_{j=0}^{M-1} x_i y_j 2^{i+j}$$

|                 |                 |                            |                |                |                               | У <sub>5</sub><br>х <sub>5</sub> | У <sub>4</sub><br>х <sub>4</sub> | y <sub>3</sub><br>x <sub>3</sub> | У <sub>2</sub><br>х <sub>2</sub> | У <sub>1</sub><br>х <sub>1</sub> | y <sub>0</sub><br>x <sub>0</sub> | multiplicand multiplier |

|-----------------|-----------------|----------------------------|----------------|----------------|-------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------|

|                 |                 |                            |                |                |                               | x <sub>0</sub> y <sub>5</sub>    | x <sub>0</sub> y <sub>4</sub>    | $\mathbf{x}_0 \mathbf{y}_3$      | x <sub>0</sub> y <sub>2</sub>    | x <sub>0</sub> y <sub>1</sub>    | $\mathbf{x}_0 \mathbf{y}_0$      | ]                       |

|                 |                 |                            |                |                | x <sub>1</sub> y <sub>5</sub> | x <sub>1</sub> y <sub>4</sub>    | $\mathbf{x}_1\mathbf{y}_3$       | $\mathbf{x}_1\mathbf{y}_2$       | $\mathbf{x}_1 \mathbf{y}_1$      | $\mathbf{x}_1 \mathbf{y}_0$      |                                  |                         |

|                 |                 |                            |                | $x_2y_5$       | $x_2y_4$                      | $\mathbf{x}_2\mathbf{y}_3$       | $\mathbf{x}_2\mathbf{y}_2$       | $\mathbf{x}_2\mathbf{y}_1$       | $\mathbf{x}_2 \mathbf{y}_0$      |                                  |                                  | partial                 |

|                 |                 |                            | $x_3y_5$       | $x_3y_4$       | $x_3y_3$                      | $x_3y_2$                         | $\mathbf{x}_3\mathbf{y}_1$       | $\mathbf{x}_3\mathbf{y}_0$       |                                  |                                  |                                  | products                |

|                 |                 | $\mathbf{x}_4\mathbf{y}_5$ | $x_4^{}y_4^{}$ | $x_4y_3$       | $x_4y_2$                      | x <sub>4</sub> y <sub>1</sub>    | $\mathbf{x}_4\mathbf{y}_0$       |                                  |                                  |                                  |                                  |                         |

|                 | $x_5y_5$        | $x_5y_4$                   | $x_5y_3$       | $x_5y_2$       | x <sub>5</sub> y <sub>1</sub> | $x_5y_0$                         |                                  |                                  |                                  |                                  |                                  |                         |

| p <sub>11</sub> | p <sub>10</sub> | p <sub>9</sub>             | p <sub>8</sub> | p <sub>7</sub> | $p_6$                         | p <sub>5</sub>                   | $P_4$                            | $p_3$                            | $p_2$                            | p <sub>1</sub>                   | $\mathbf{p}_0$                   | product                 |

Jacob Abraham, September 24, 2020 16 / 27

Department of Electrical and Computer Engineering, The University of Texas at Austin J. A. Abraham, September 24, 2020

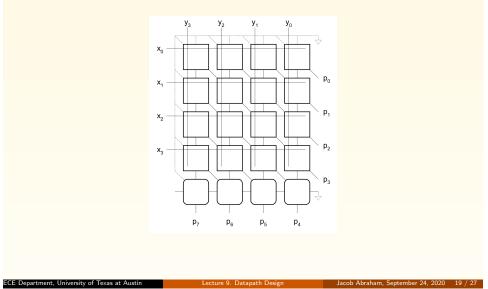

# Rectangular Array

Squash array to fit rectangular floorplan

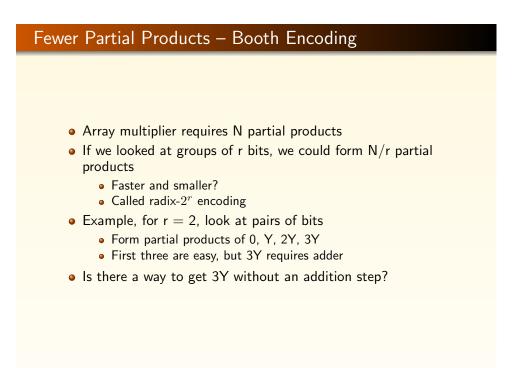

## Booth Encoding

ECE Department, University of Texas at Austin

• Instead of 3Y, try -Y, then increment next partial product to add 4Y

Jacob Abraham, September 24, 2020 20 / 27

| Inputs     |                                                                                             |   | Partial Product | Boo    | oth Sel |       |  |

|------------|---------------------------------------------------------------------------------------------|---|-----------------|--------|---------|-------|--|

| $x_{2i+1}$ | $x_{2i}   x_{2i-1}$                                                                         |   | $PP_i$          | $X_i$  | $2X_i$  | $M_i$ |  |

| 0          | 0                                                                                           | 0 | 0               | 0      | 0       | 0     |  |

| 0 0 1      |                                                                                             | 1 | Y               | 1      | 0 0     |       |  |

| 0          | 0 1 0                                                                                       |   | Y               | 1      | 0       | 0     |  |

| 0          | 1                                                                                           | 1 | 2Y              | 0      | 1       | 0     |  |

| 1          | $ \begin{array}{c ccccc} 1 & 0 & 0 \\ \hline 1 & 0 & 1 \\ \hline 1 & 1 & 0 \\ \end{array} $ |   | -2Y             | 0      | 1       | 1     |  |

| 1          |                                                                                             |   | -Y              | 1<br>1 | 0       | 1     |  |

| 1          |                                                                                             |   | -Y              |        | 0       | 1     |  |

| 1          | 1                                                                                           | 1 | -0(=0)          | 0      | 0       | 1     |  |

• Similarly, for 2Y, try -2Y + 4Y in next partial product

### Advanced Multiplication

- Signed vs. unsigned inputs

- Higher radix Booth encoding

- Array vs. tree CSA networks

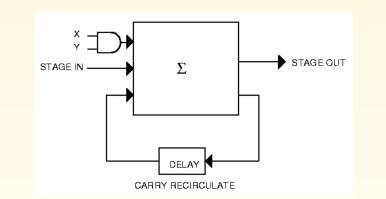

#### Serial Multiplication

ECE Department, University of Te

ECE Department, University of Texas at Austin

- Lower area at expense of speed

- Example, signal processing on bit streams

- Delay for  $n \times n$  multiply

- 2n bit product with 2n bit delay

- Additional n-bit delay to shift n bits

- Total delay of 3n bits

- Pipelined multiplier: possible to produce a new 2n bit product every 2n bit times after initial n bit delay

- Only interest in high-order bits: n bit *latency* for n bit product

- Can design for desired throughput

#### Serial Multiplier Architecture

Area for structure increases linearly with number of bits, n

Pipeline multiplier accumulates partial product sums starting with the least significant partial product (result is n-bit number which is truncated to n-1 bits before the next partial product)

Jacob Abraham, September 24, 2020 23 / 27

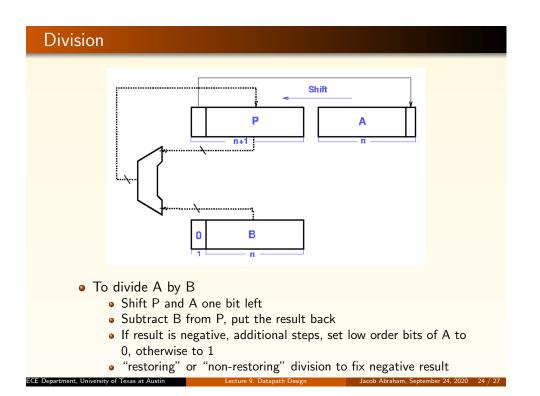

#### SRT Division

ECE Department, University of Texas at Austin

Divide A by B (n-bits)(view numbers as fractions between 1/2 and 1)

If B has k leading 0s when expressed using n bits, shift all registers by k bits

- e For i = 0 to (n-1)

- If top 3 bits of P equal, set  $q_i = 0$ , shift (P,A) one bit left

- **②** If top 3 bits of P not all equal, and P negative, set  $q_i = -1$ , (written as  $\overline{1}$ , shift (P,A) one bit left and add B

- $\textbf{Otherwise, set } q_i = 1, \text{ shift (P,A) one bit left, subtract B}$

- If the final remainder is negative, correct by adding B, correct quotient by subtracting 1; finally, shift remainder k bits right adding A CDT alreadition used in Dantium action

Jacob Abraham, September 24, 2020 25 / 27

Radix-4 SRT algorithm used in Pentium chip